A gallium nitride transistor structure and its preparation method

A technology of transistors and gallium nitride, which is applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of small etching options and difficult device processes, and achieve the effects of alleviating electric field concentration, simple growth process, and alleviating virtual gate effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

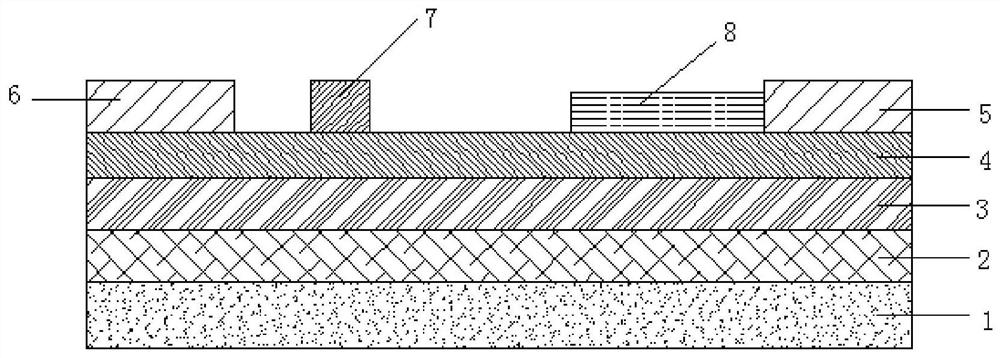

[0040] A gallium nitride transistor structure, comprising a substrate 1, the substrate 1 being a Si, SiC, GaN or sapphire substrate;

[0041] A GaN-based buffer layer 2 located above the substrate 1; a GaN-based channel layer 3 located above the GaN-based buffer layer 2; an In located above the GaN-based channel layer 3 x Al y Ga 1-x-y N barrier layer 4, where 0≤x<1, 0≤y<1, and x+y≠0;

[0042] The structure of the GaN-based buffer layer 2 is, from bottom to top, an AlN nucleation layer, a GaN buffer layer, and an AlGaN buffer layer;

[0043] in In x Al y Ga 1-x-y The source electrode 6 at one end above the N barrier layer 4; the source electrode 6 is an ohmic contact metal electrode, and the ohmic contact metal electrode is composed of a single layer or multiple layers of metal and In x Al y Ga 1-x-y The N barrier layer 4 forms an ohmic contact electrode;

[0044] in In x Al y Ga 1-x-y The drain 5 at the other end above the N barrier layer 4; the drain 5 is an ohmi...

Embodiment 2

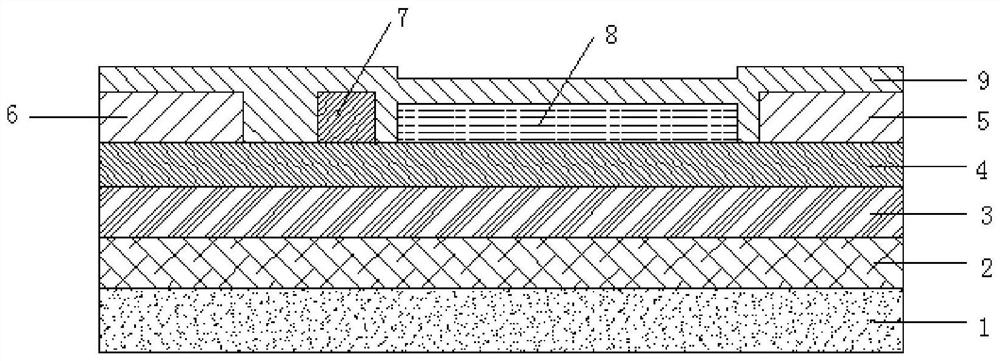

[0055] A gallium nitride transistor structure, the others are the same as in Embodiment 1, except that the uppermost layer of the gallium nitride transistor structure is also covered with a passivation layer 9; the passivation layer 9 includes Si 3 N 4 , Al 2 O 3 , AlN, Y 2 O 3 , La 2 O 3 , Ta 2 O 5 , TiO 2 , HfO 2 , ZrO 2 single-layer or multi-layer composite structures in

[0056] The preparation method of the gallium nitride transistor is the same as in Embodiment 1, except that after step (6), a passivation layer 9 deposition step is included, and the passivation layer 9 is deposited by PECVD, MOCVD, ALD or sputtering.

Embodiment 3

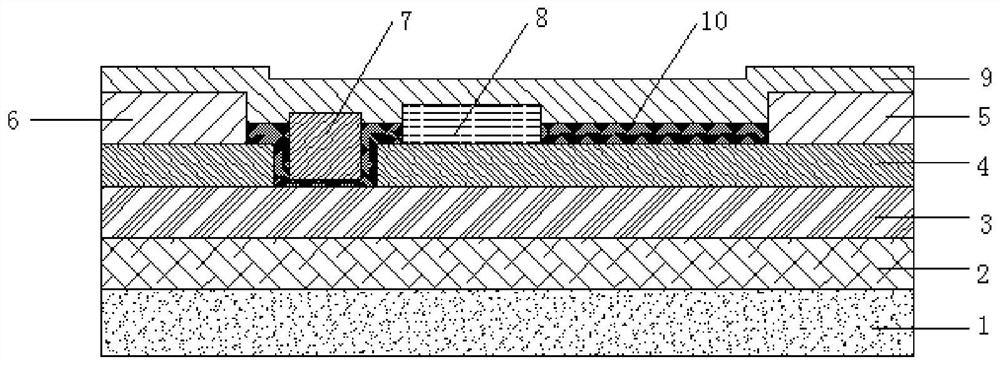

[0058] A gallium nitride transistor structure, comprising a substrate 1, the substrate 1 being a Si, SiC, GaN or sapphire substrate;

[0059] A GaN-based buffer layer 2 located above the substrate 1; a GaN-based channel layer 3 located above the GaN-based buffer layer 2; an In located above the GaN-based channel layer 3 x Al y Ga 1-x-y N barrier layer 4, where 0≤x<1, 0≤y<1, and x+y≠0;

[0060] The structure of the GaN-based buffer layer 2 is, from bottom to top, an AlN nucleation layer, a GaN buffer layer, and an AlGaN buffer layer;

[0061] in In x Al y Ga 1-x-y The source electrode 6 at one end above the N barrier layer 4; the source electrode 6 is an ohmic contact metal electrode, and the ohmic contact metal electrode is composed of a single layer or multiple layers of metal and In x Al y Ga 1-x-y The N barrier layer 4 forms an ohmic contact electrode;

[0062] in In x Al y Ga 1-x-y The drain 5 at the other end above the N barrier layer 4; the drain 5 is an ohmi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More