Patents

Literature

35results about How to "Suppression of avalanche effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Gallium nitride based transistor structure with high electron mobility

InactiveCN101399284APrevent segregation and spreadHigh conduction band discontinuitySemiconductor devicesIndiumIsolation layer

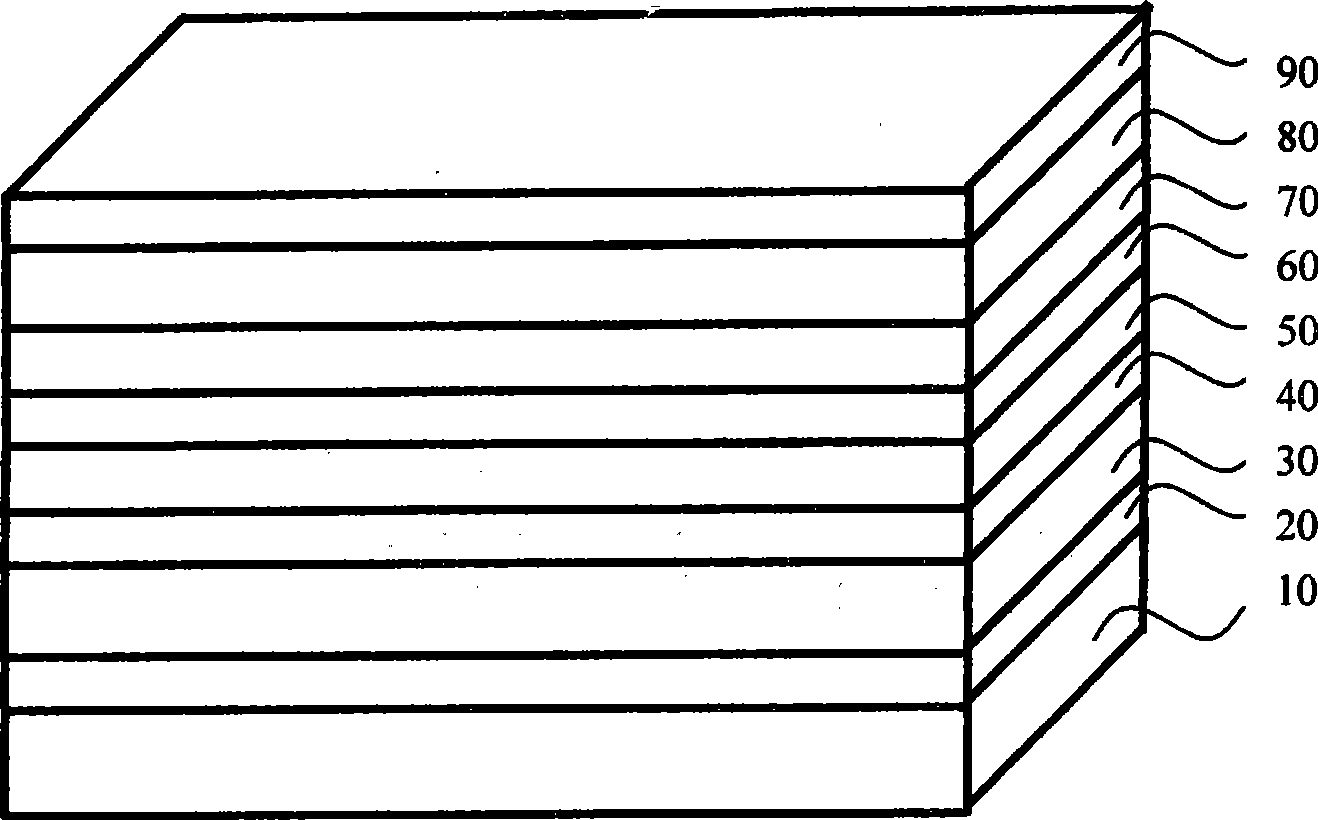

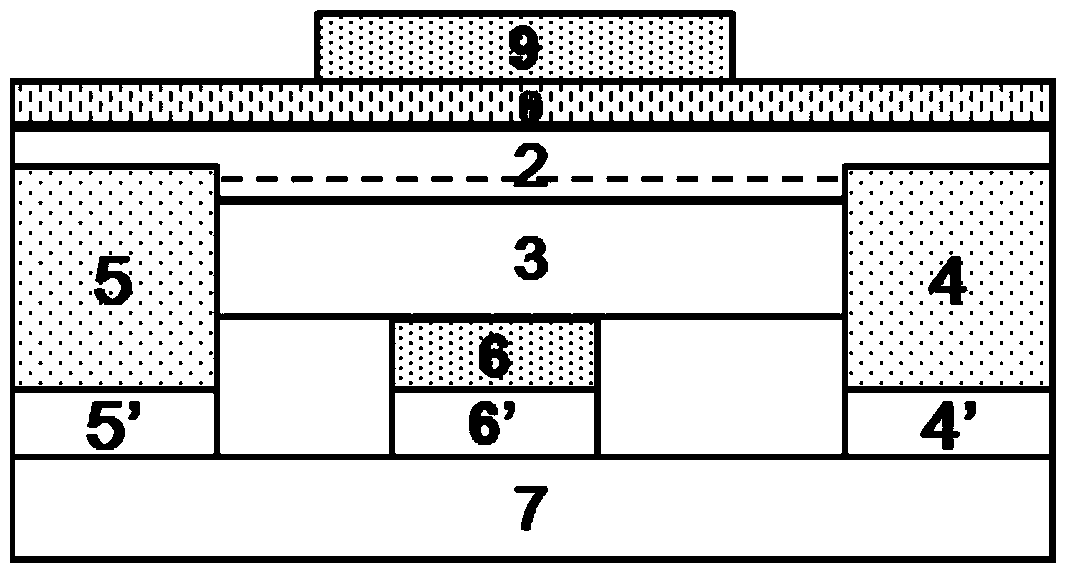

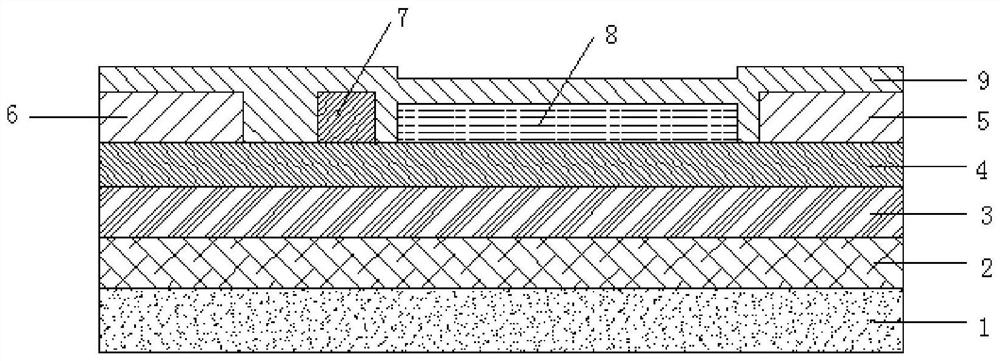

A gallium nitride-based high electron mobility transistor structure comprises: a substrate; a low temperature nucleating layer is produced on the substrate; a gallium nitride-based high resistivity layer is produced on the low temperature nucleation layer; an indium gallium nitride insertion layer is produced on the gallium nitride-based high resistivity layer; a low temperature gallium nitride isolation layer is produced on the indium gallium nitride insertion layer; a high mobility gallium nitride layer is produced on the low temperature gallium nitride isolation layer; an aluminum nitride insertion layer is produced on the high mobility gallium nitride layer; an aluminium gallium nitride barrier layer is produced on the aluminum nitride insertion layer; a gallium nitride cap layer is produced on the aluminium gallium nitride barrier layer, and the gallium nitride cap layer effectively inhibit the current collapse effect.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

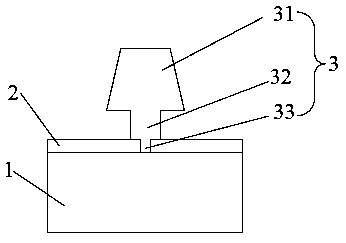

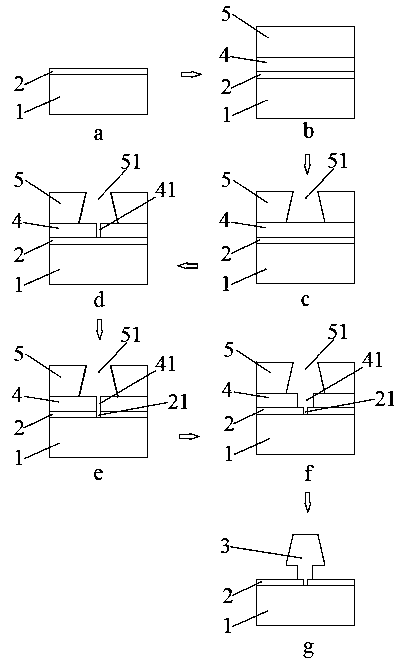

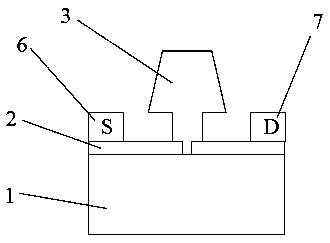

A double T-shaped gate, and a manufacturing method and an application thereof

InactiveCN109103245AImprove the problem of low exposure efficiencyIncrease production capacitySemiconductor devicesParasitic capacitanceEngineering

A double T-shaped gate, and a manufacturing method and an application thereof are provided. The double T-shaped gate comprises a gate foot, a gate root and a gate cap, wherein the gate foot and the gate root form a first level T-shaped gate, the gate root and the gate cap form a second level T-shaped gate, the gate cap is suspended, and the gate foot grows on a substrate through a dielectric passivation layer. The invention can reduce the gate resistance, and the manufacturing method thereof not only can effectively realize the small line width gate, reduce the gate parasitic capacitance, butalso can improve the efficiency of the gate fabrication.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

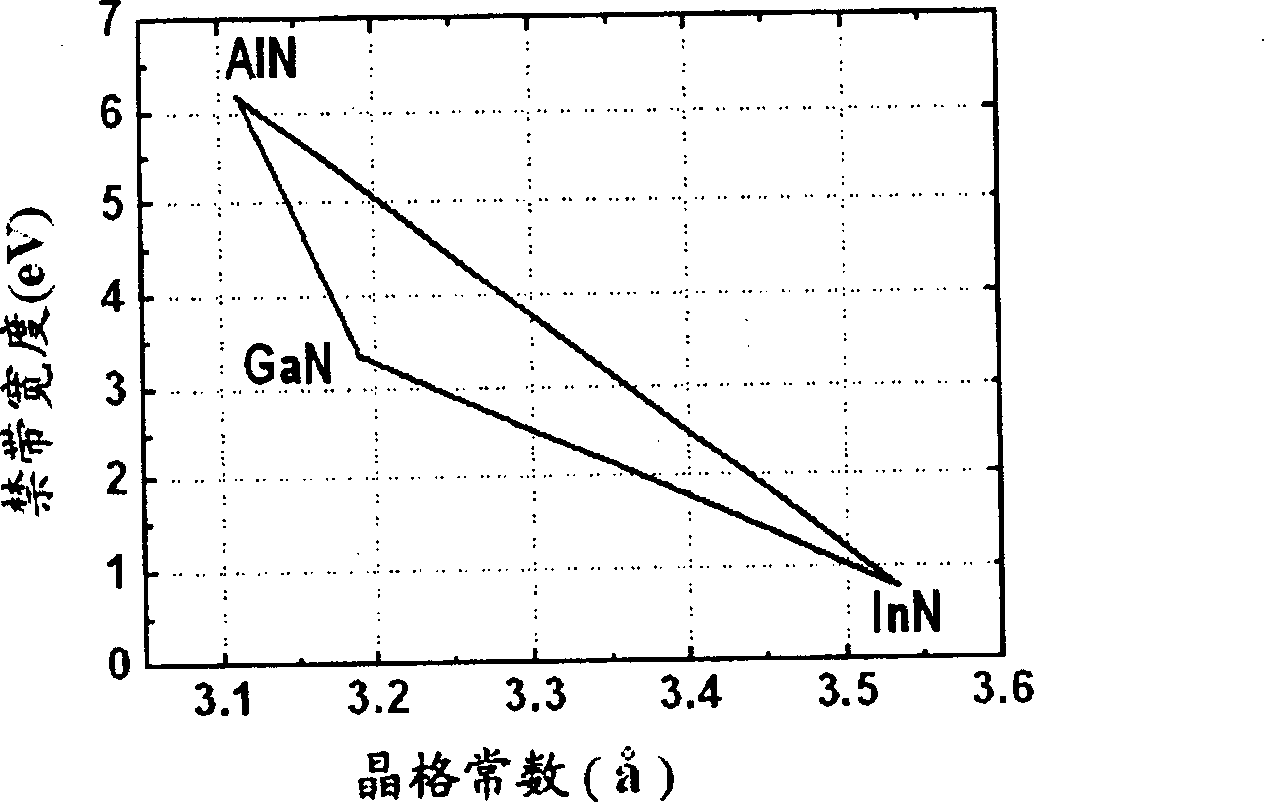

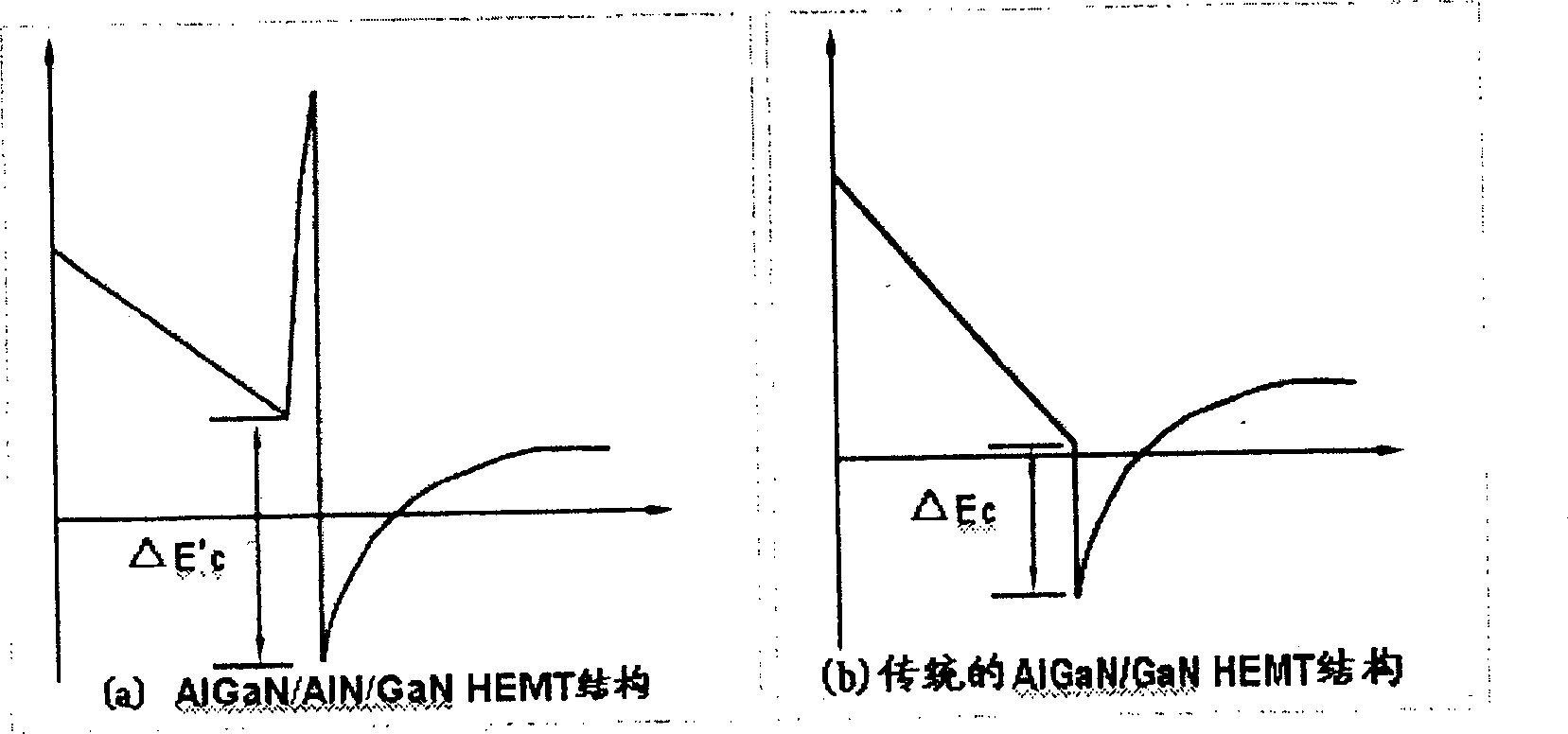

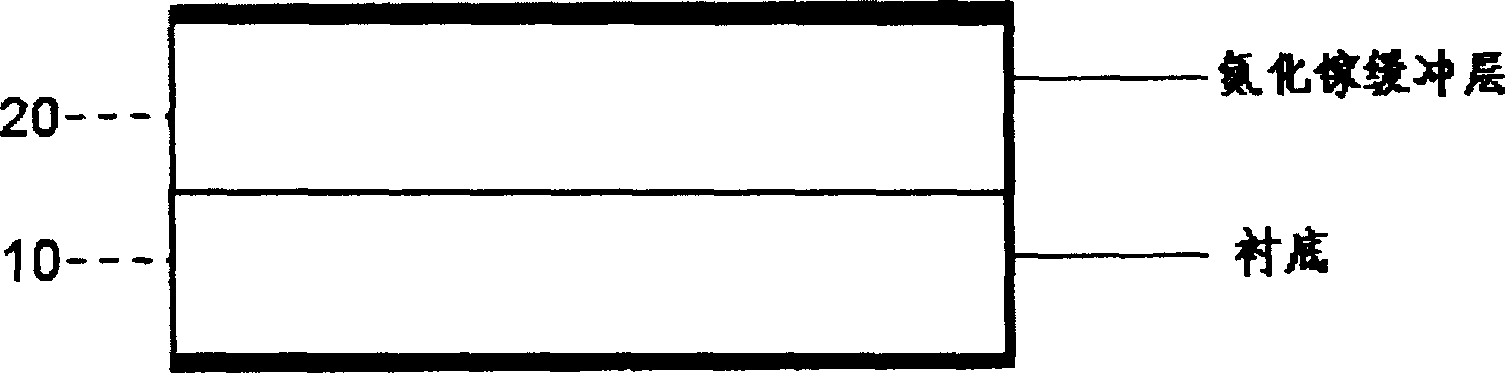

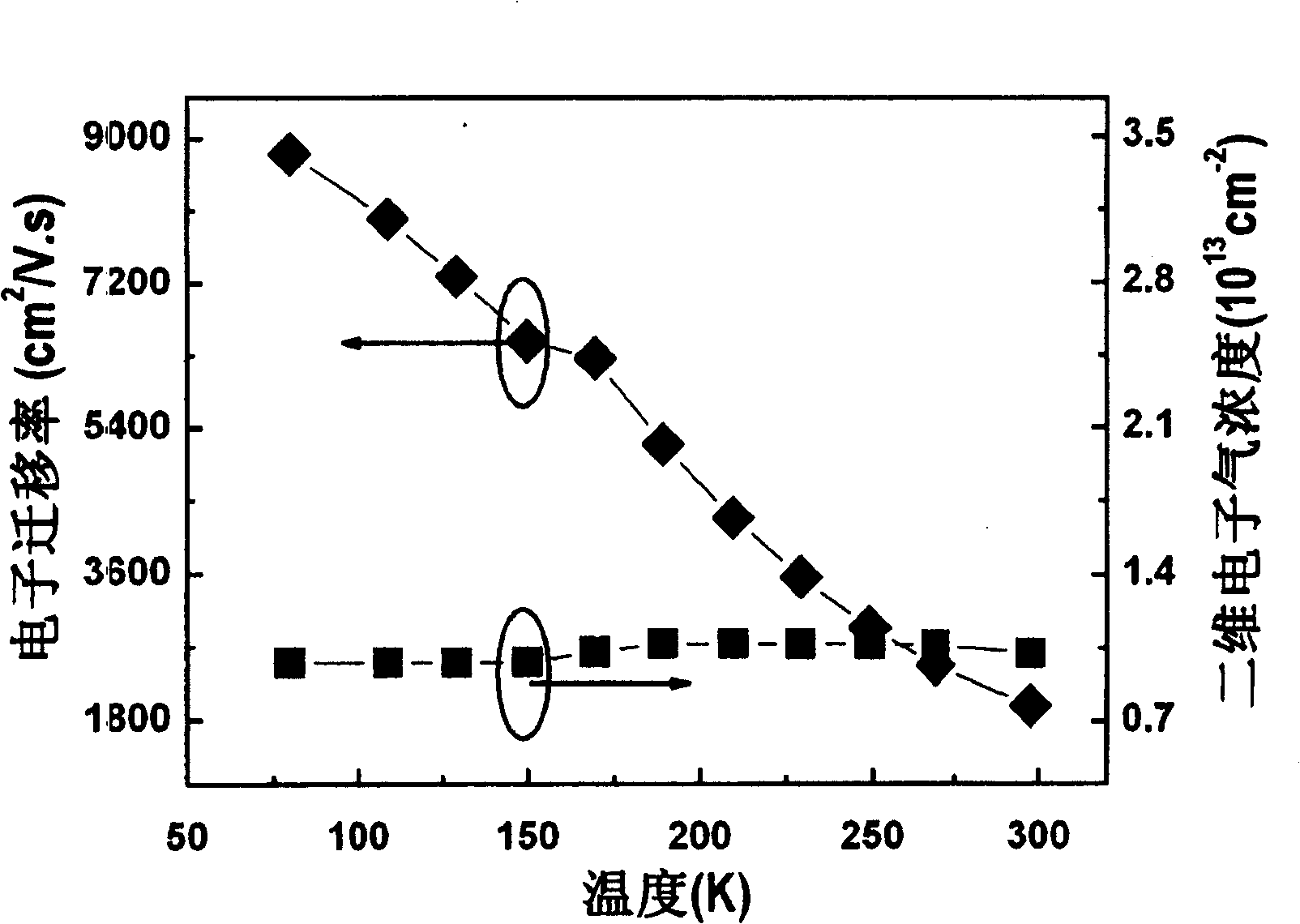

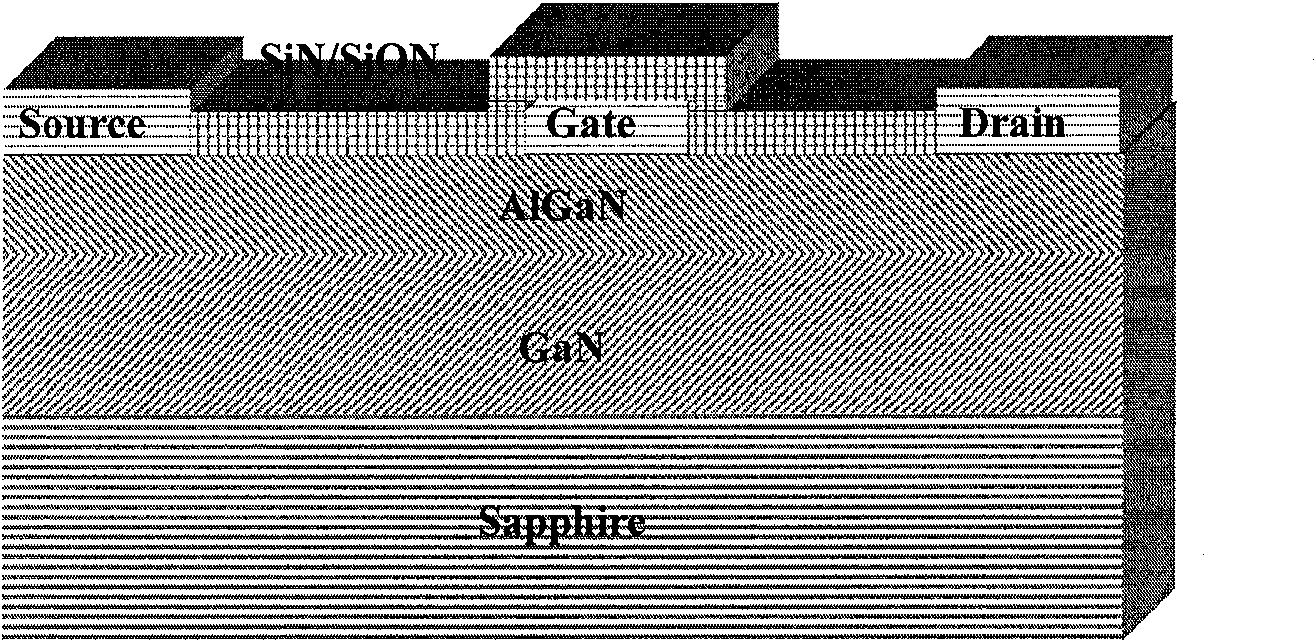

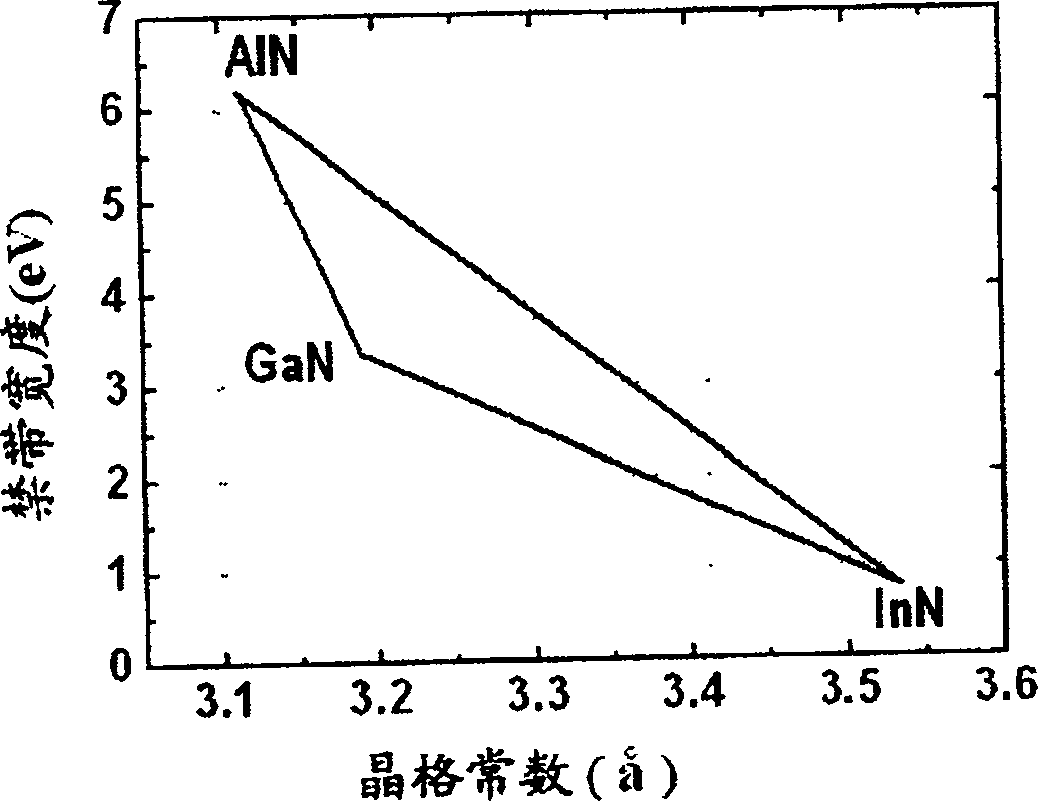

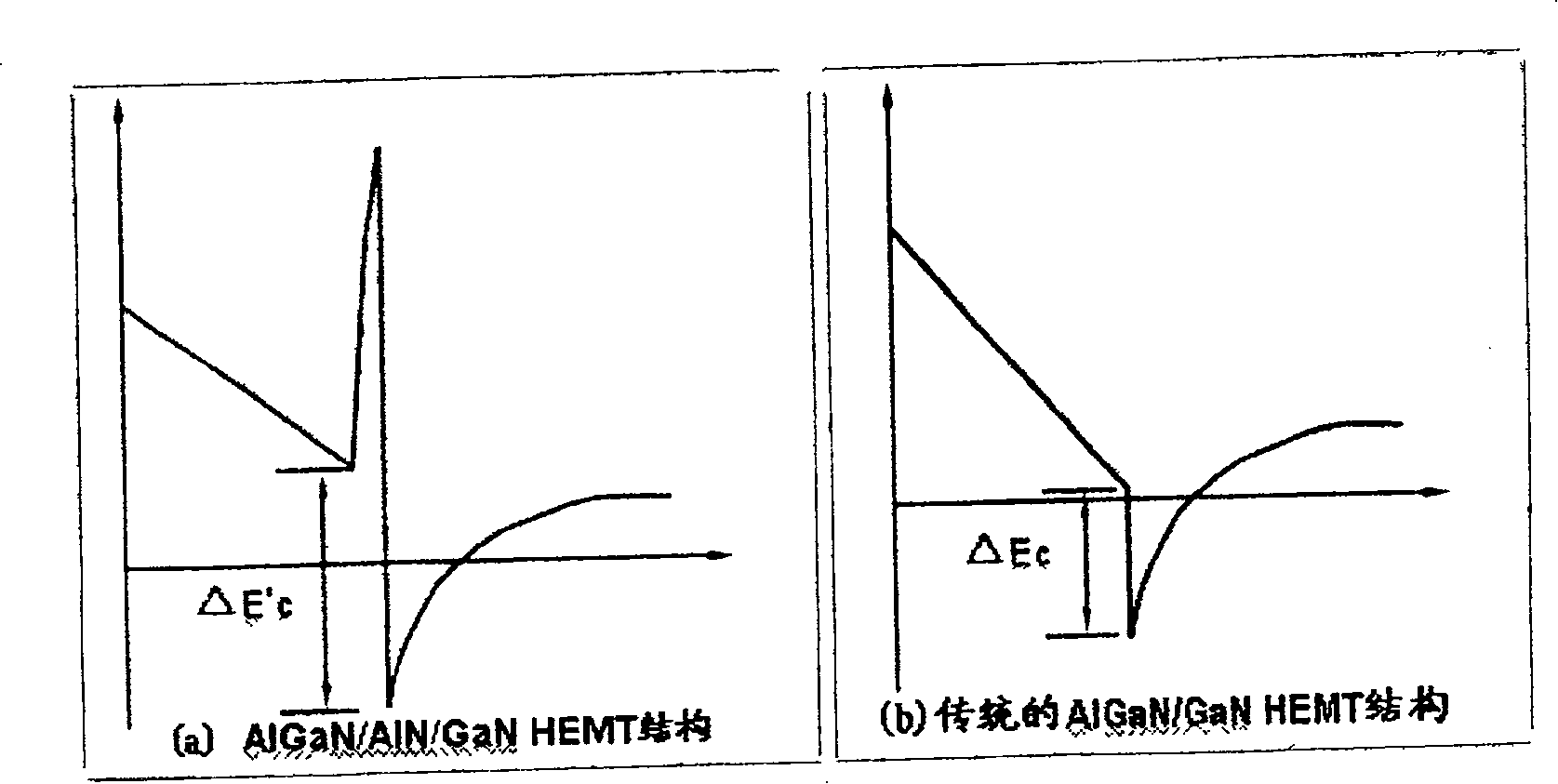

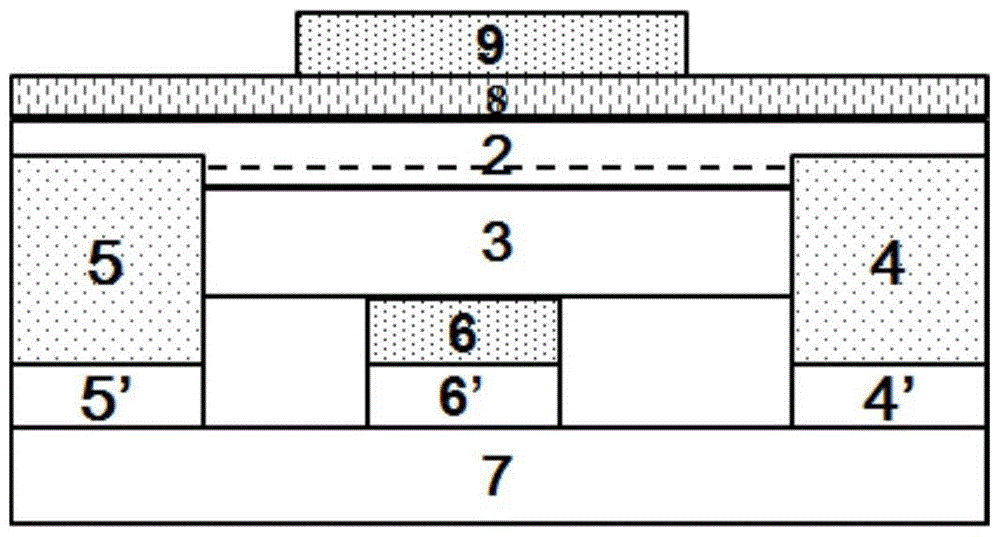

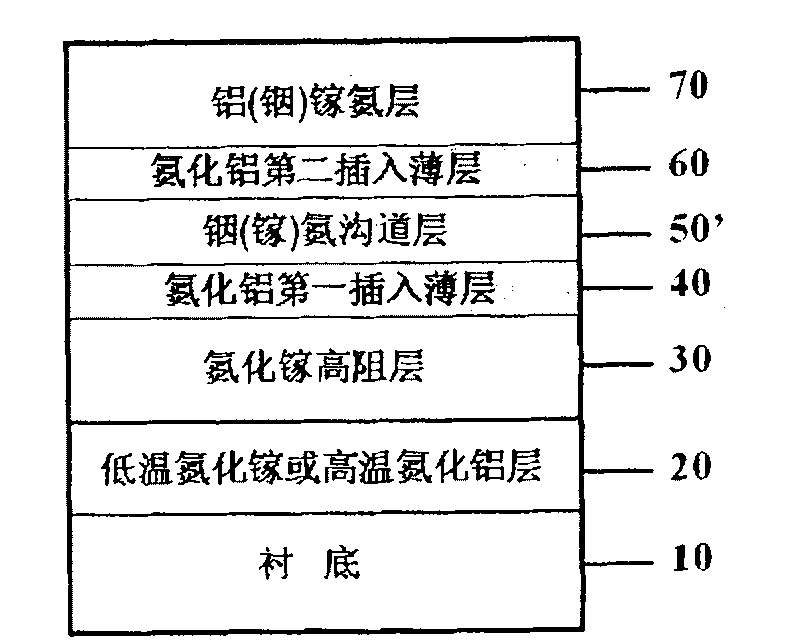

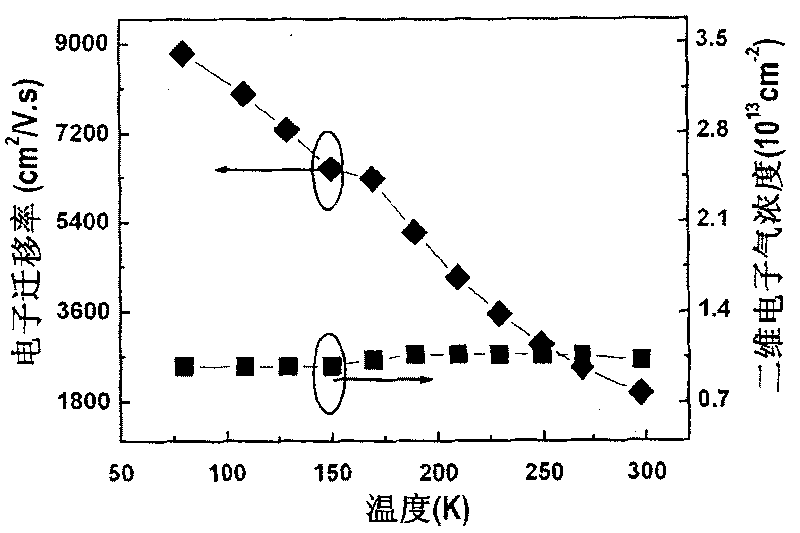

Structure of improving gallium nitride base high electronic mobility transistor property and producing method

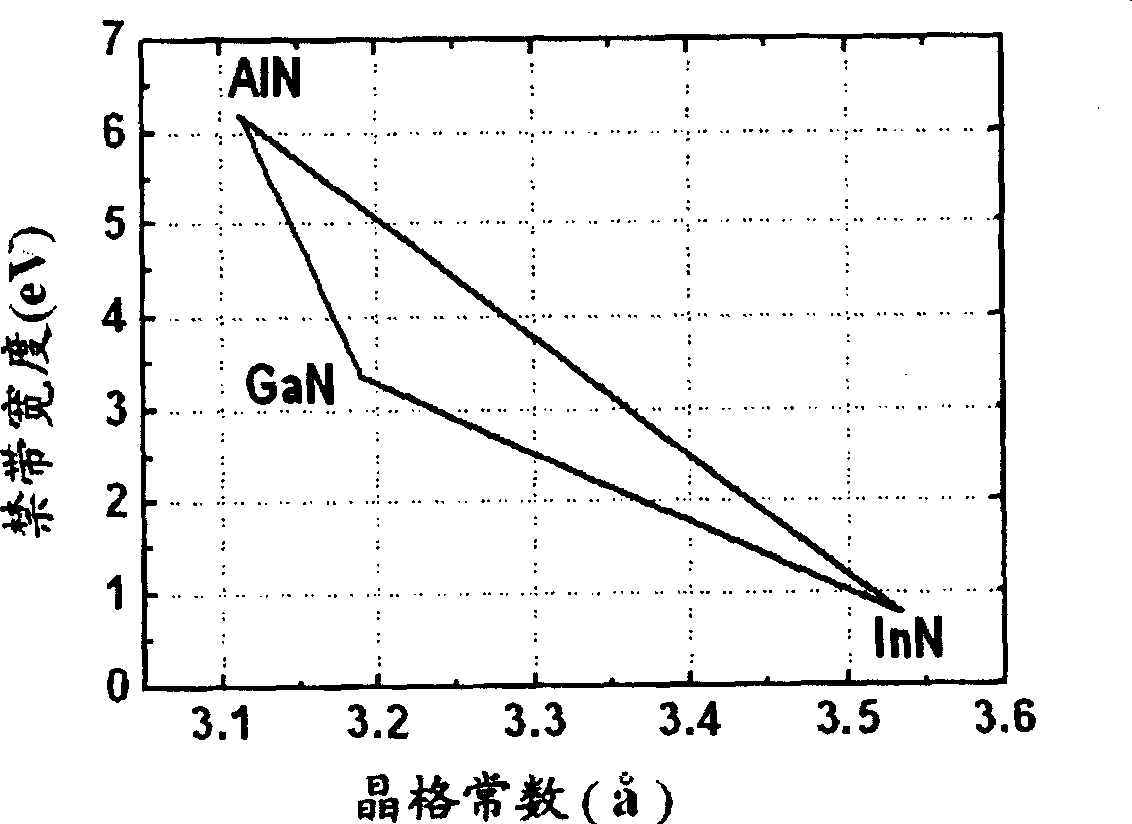

InactiveCN1783512AIncrease concentrationImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceGallium nitride

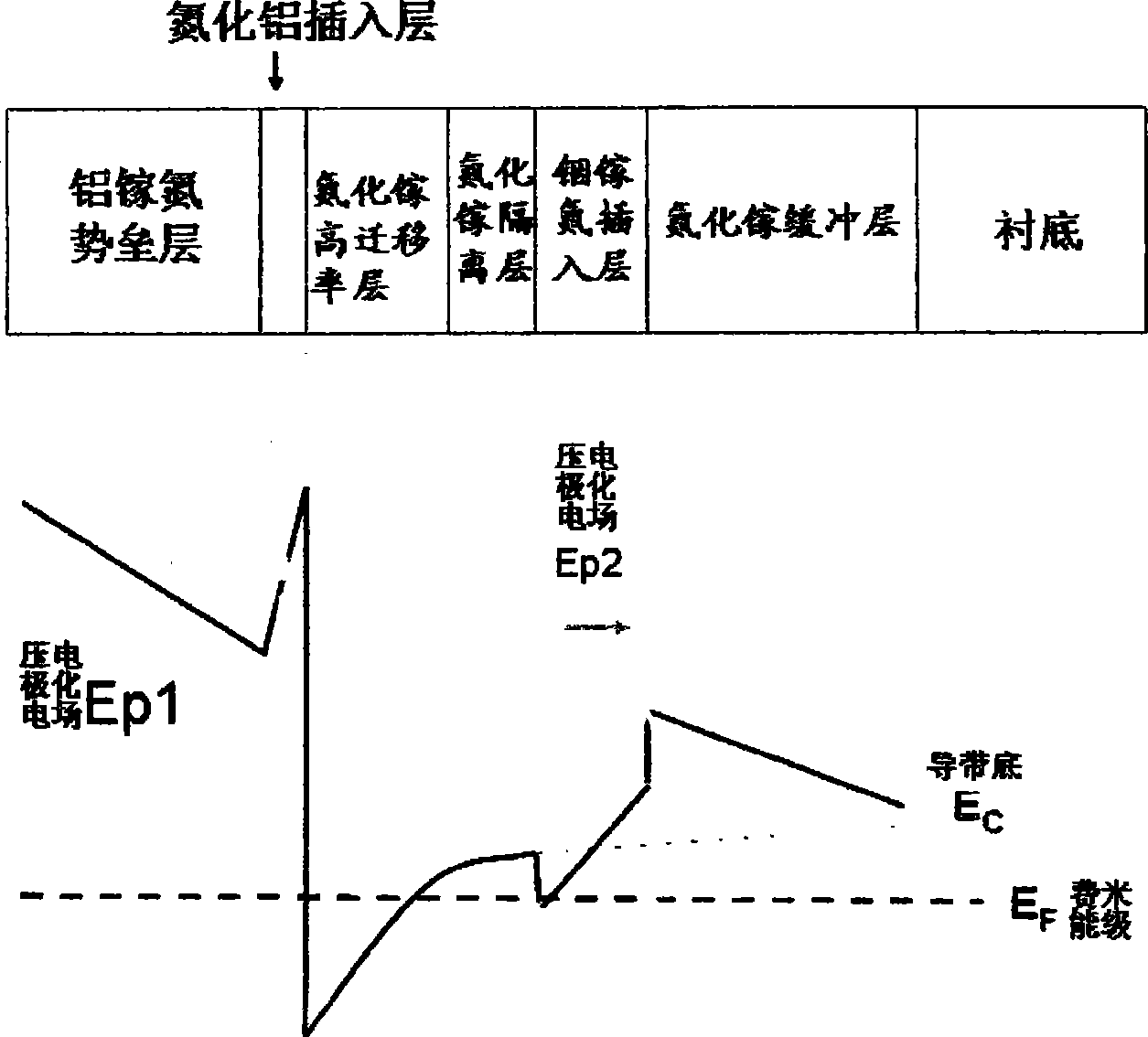

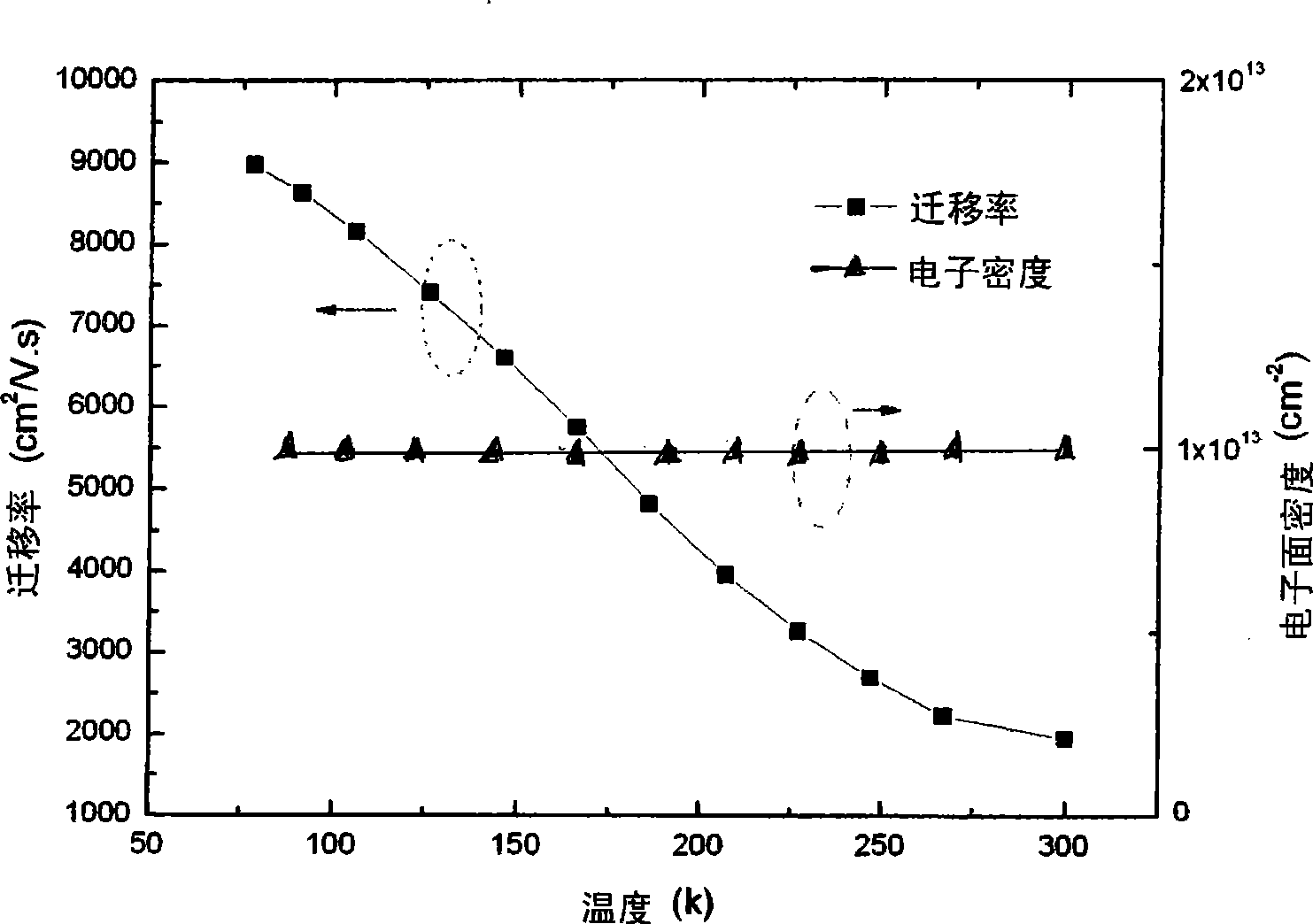

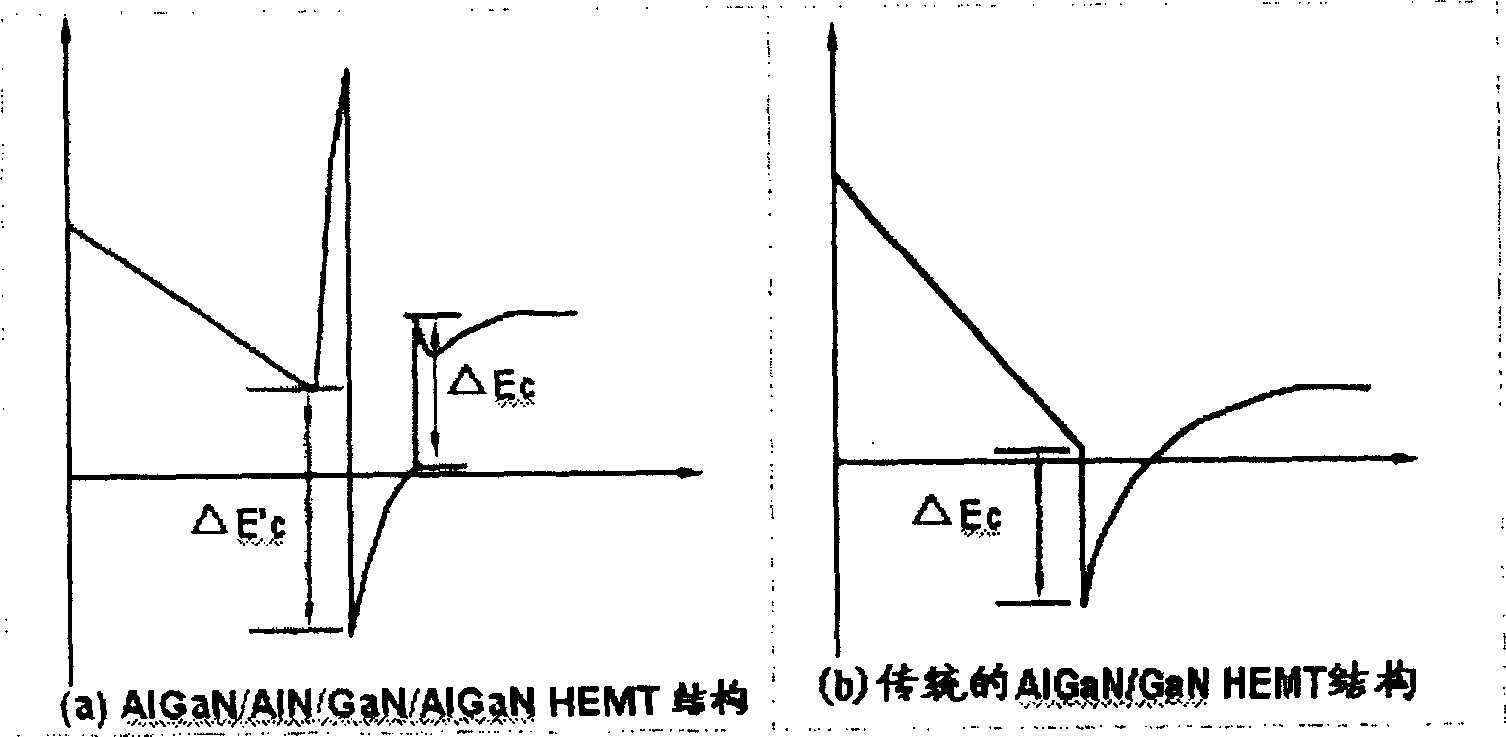

A structure is for increasing performance of transistors of GaN base high electronic movability includes: a sapphire substrate, a SiC2 substrate or a silicon substrate, a high resistance semi-insulation GaN buffer layer processed on the substrate, a high movability GaN channel layer processed on the buffer layer, a thin ALN plug-in layer processed on the channel layer to increase the integrated performance of the transistor materials of GaN base high electronic movability, a n-type doped or un-purpose doped ALGaN barrier layer processed on the thin ALN plug-in layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

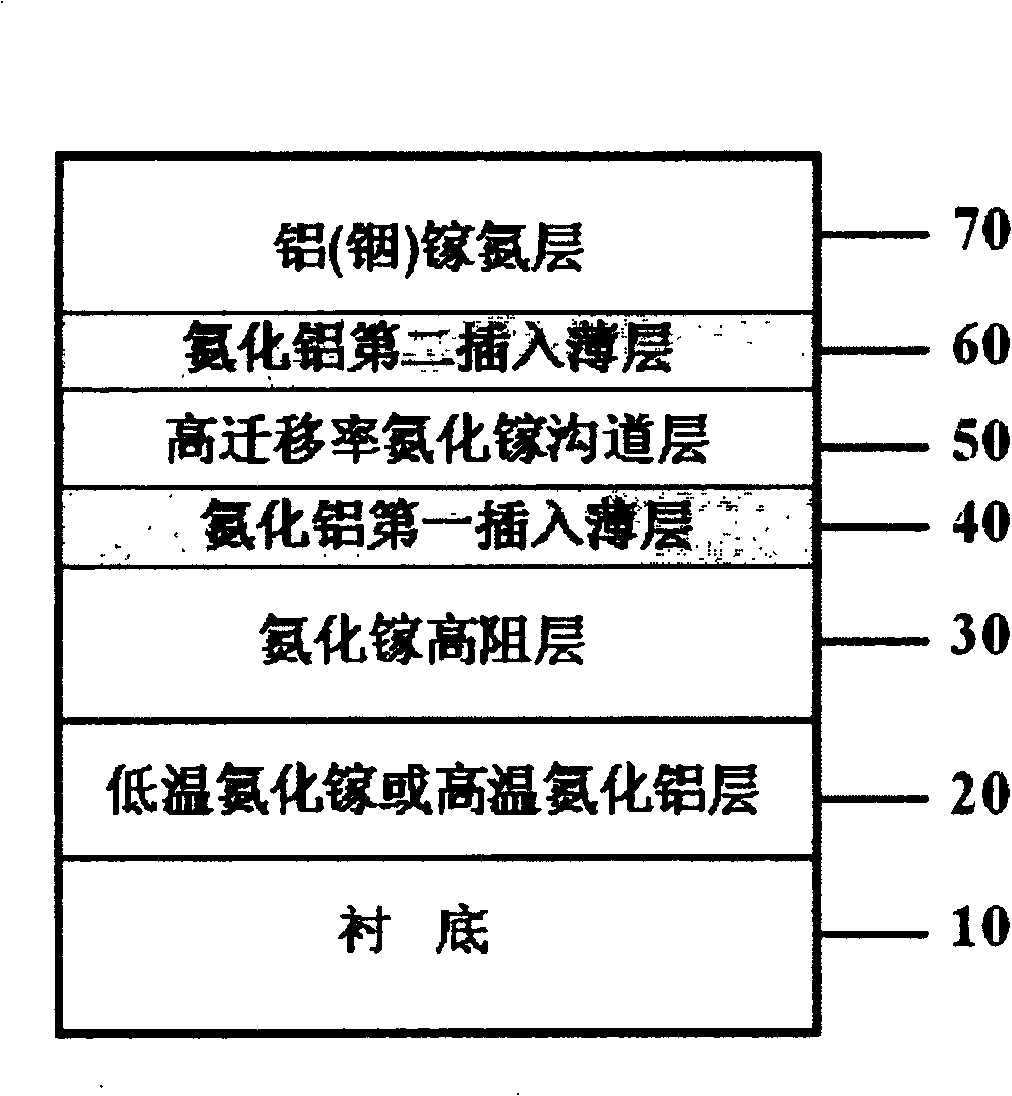

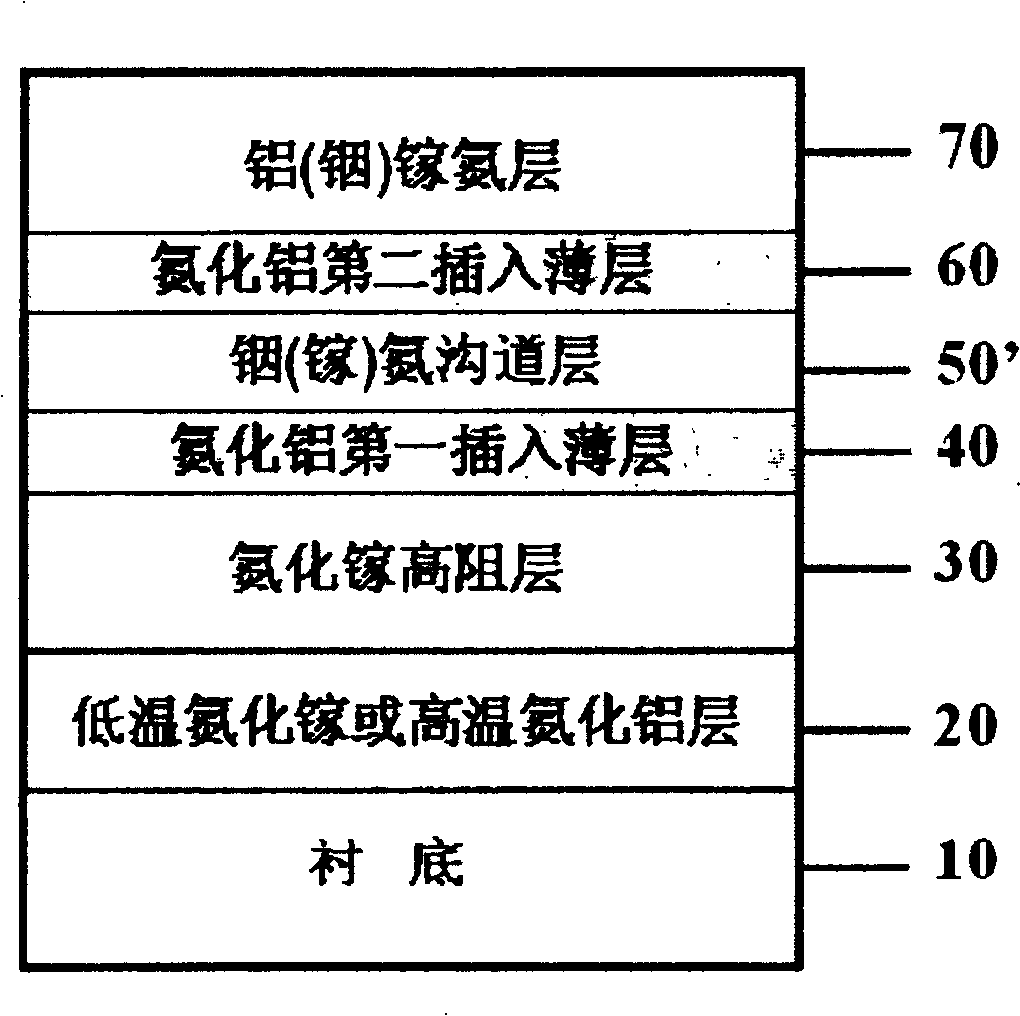

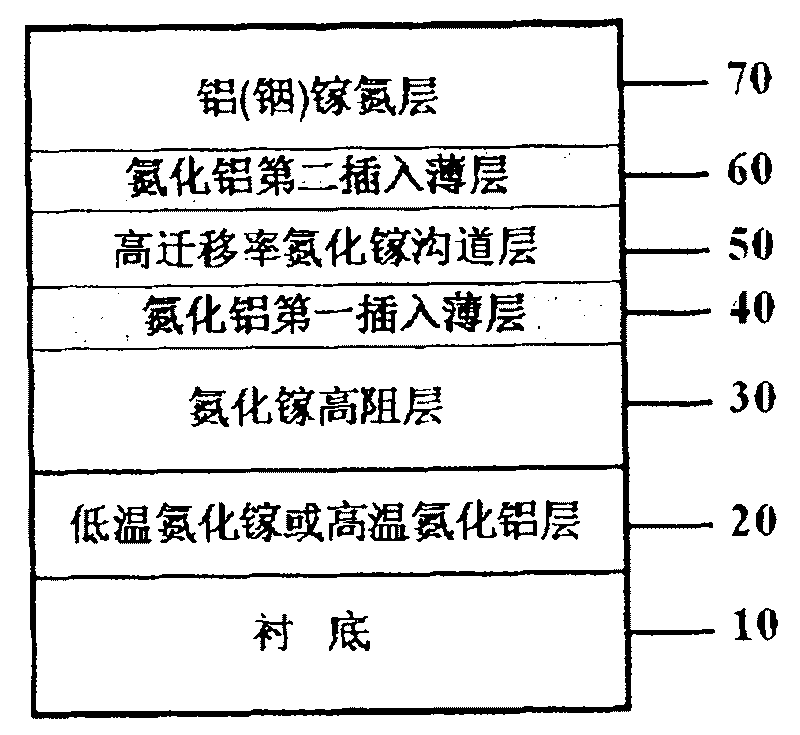

GaN dual heterogeneity node field effect transistor structure and its making method

InactiveCN101266999ARaise the barrier heightImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerGallium nitride

A gallium nitride-based double heterojunction field effect transistor structure comprises a substrate, a low temperature gallium nitride layer or high temperature aluminum nitride layer formed on the substrate; a high insulation layer with unintentional-doped or doped gallium nitride; the high insulation layer with unintentional-doped or doped gallium nitride is formed on a low temperature gallium nucleation layer or a high temperature gallium nitride nucleation layer; a first aluminum nitride inserting layer, the first aluminum nitride inserting layer is formed on the high insulation layer with unintentional-doped or doped gallium nitride; a unintentional-doped gallium nitride channel layer, the unintentional-doped gallium nitride channel layer is formed on the first aluminum nitride inserting layer; a second aluminum nitride inserting layer, the second aluminum nitride inserting layer is formed on the unintentional-doped gallium nitride channel layer, an unintentional-doped or n-type doped AlxInyGazN layer, the unintentional-doped or n-type doped AlxInyGazN layer is formed on the second aluminum nitride inserting layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

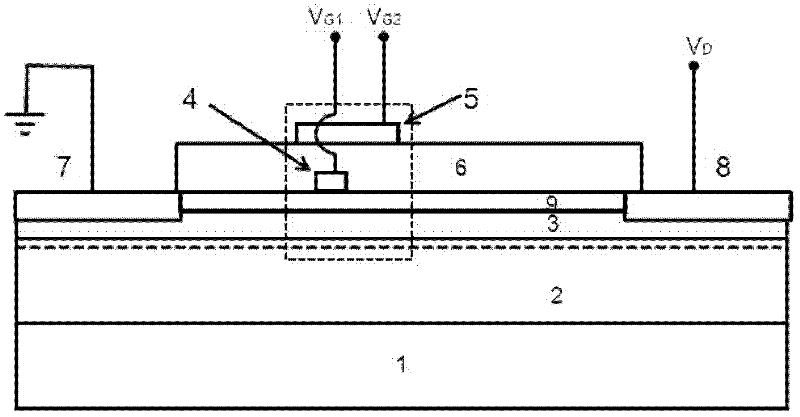

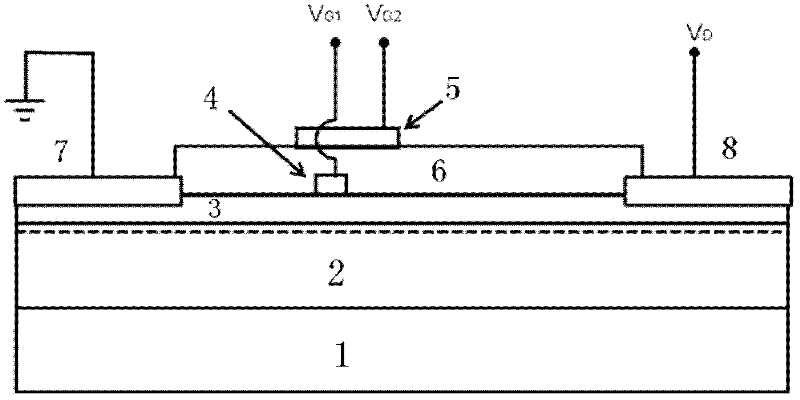

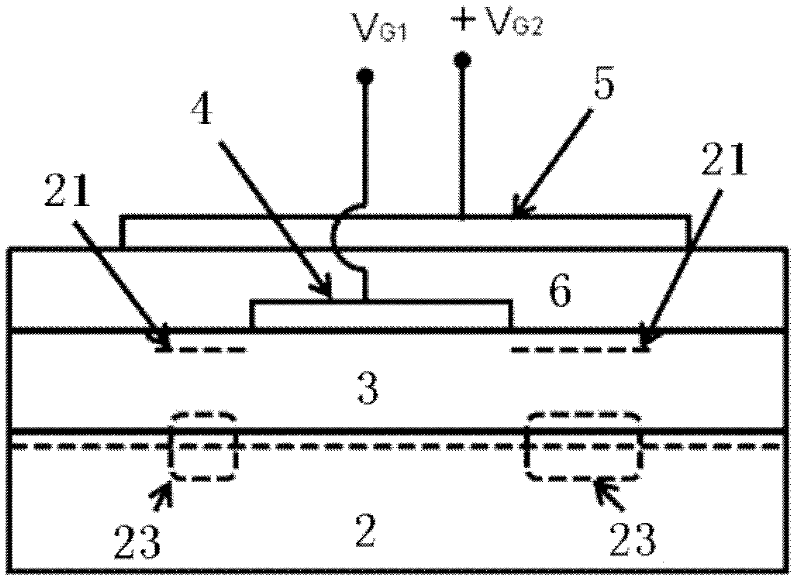

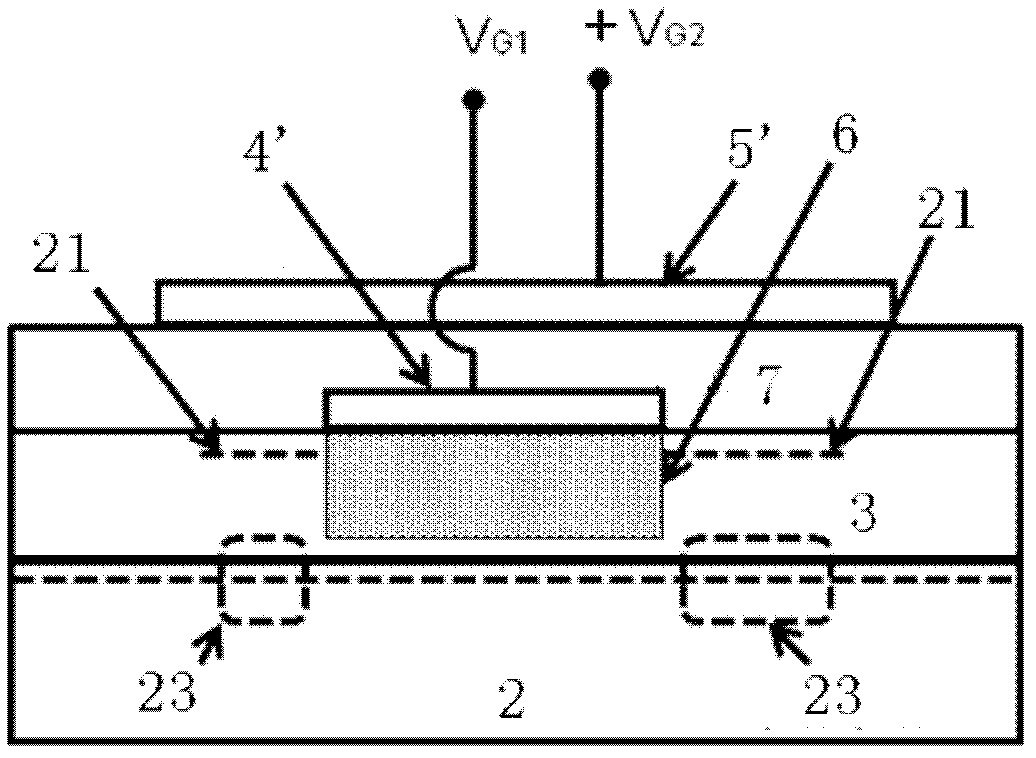

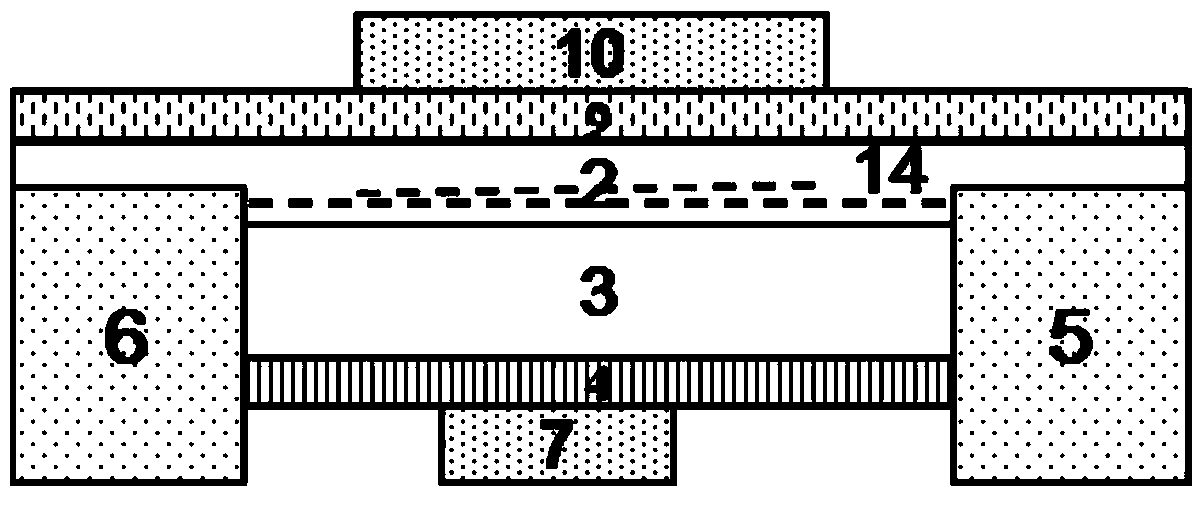

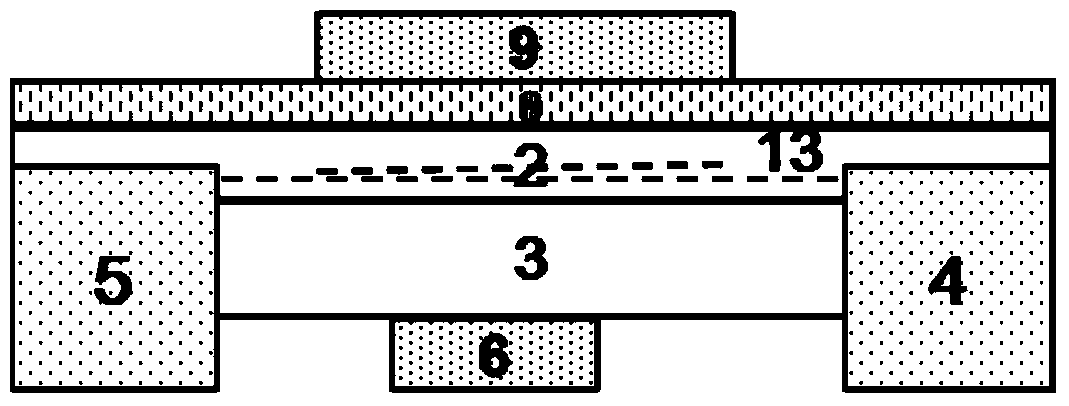

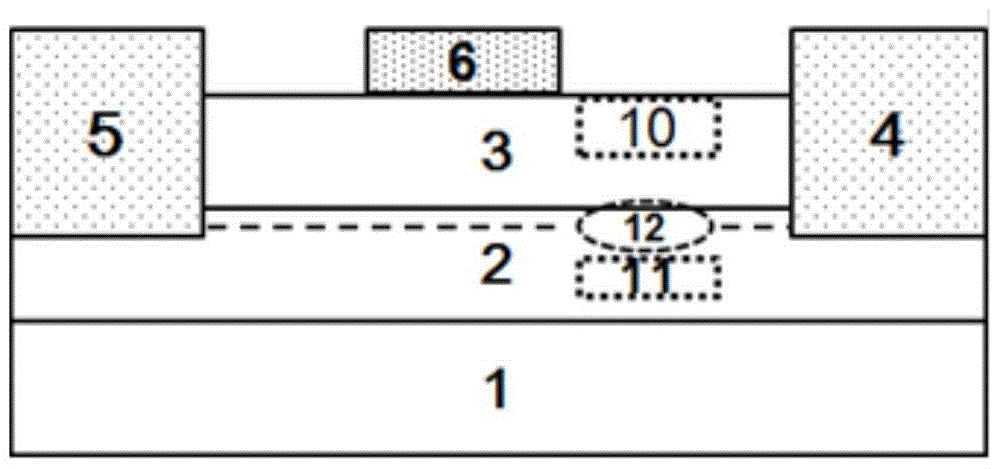

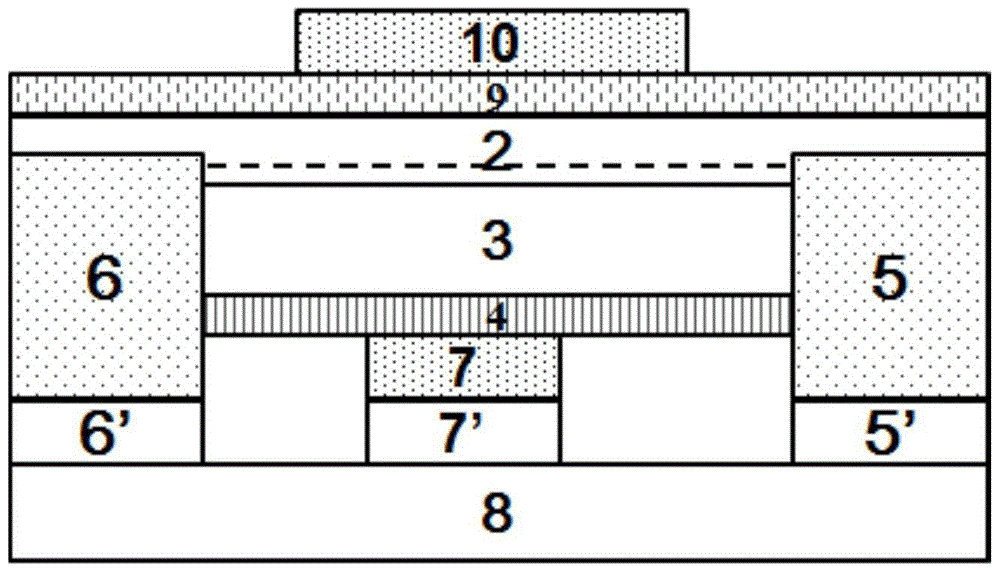

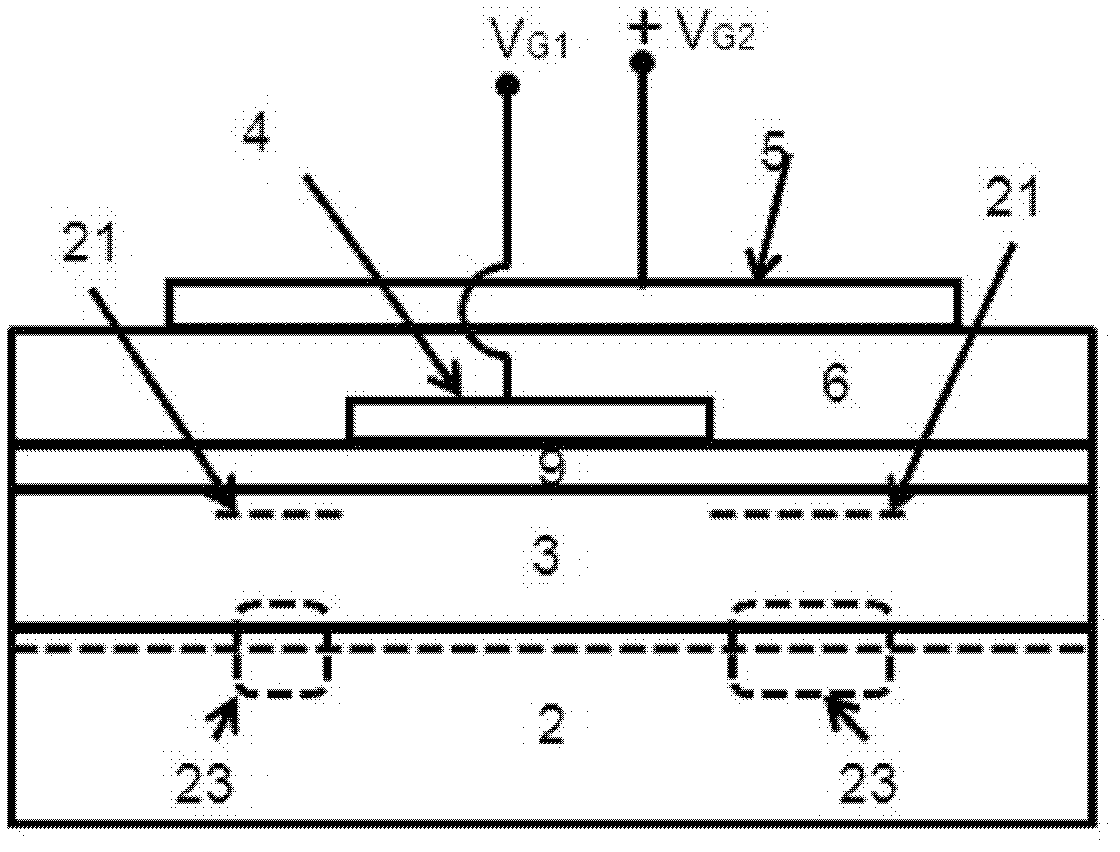

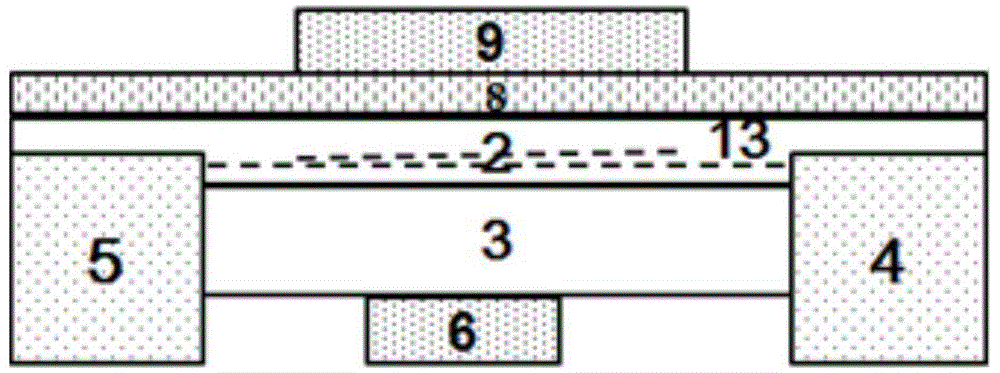

III nitride MISHEMT device

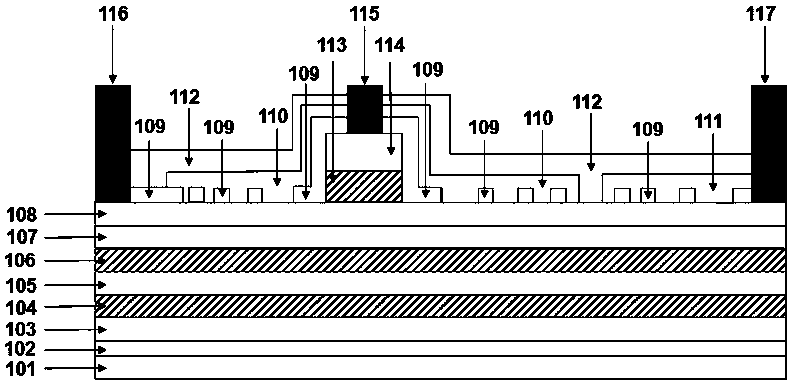

InactiveCN102403349ASuppression of avalanche effectsSemiconductor devicesElectricityInsulation layer

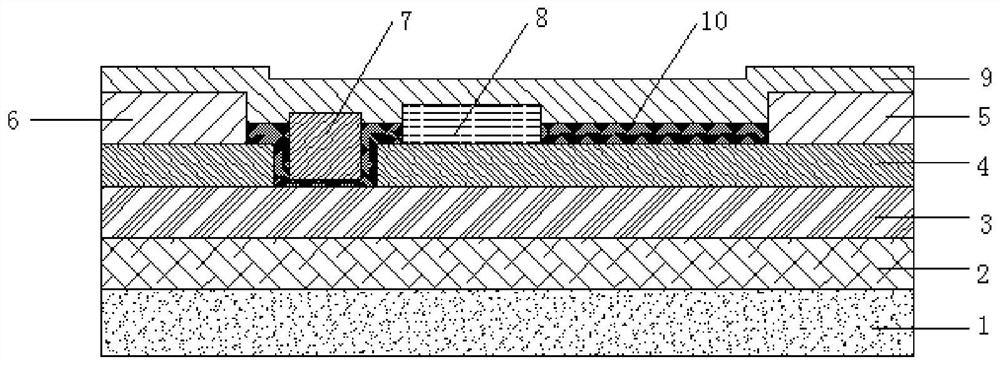

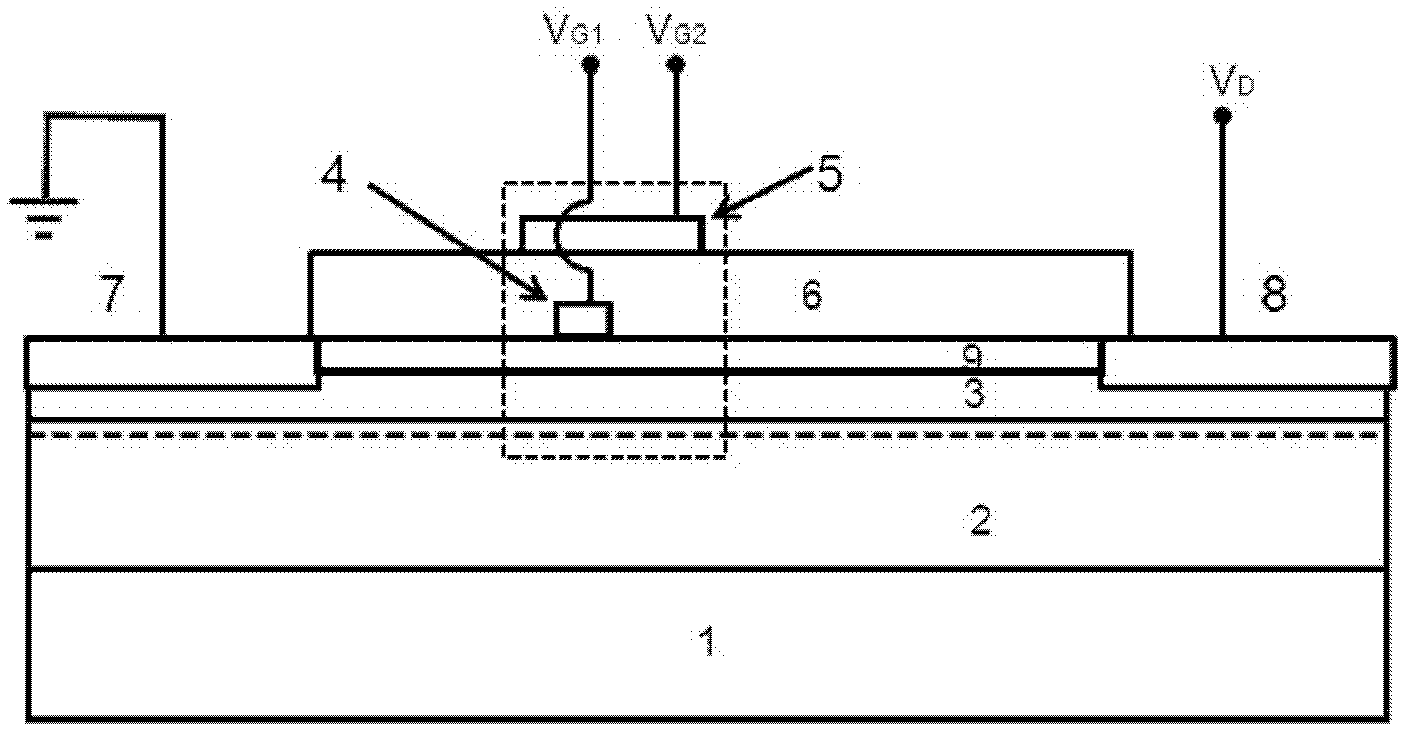

The invention discloses an III nitride MISHEMT device, which comprises source and drain electrodes, main and secondary grids, first and second medium layers and a heterostructure; the source and drain electrodes are electrically connected through two-dimensional electron gas formed in the heterostructure; the heterostructure comprises first and second semiconductors; the first semiconductor is arranged between the source and drain electrodes; the second semiconductor is formed on the surface of the first semiconductor and is provided with a band gap wider than the first semiconductor; the first medium layer is arranged on the surface of the second semiconductor and forms a metal insulation layer semiconductor contact (MIS) along with the second semiconductor and the main grid; the second medium layer is arranged on the surfaces of the first medium layer and the main grid and forms electric isolation for the main grid and the secondary grid; the main grid is arranged at one side of thesurface of the first medium layer close to the source electrode; and the secondary grid is formed on the surface of the second medium layer, and at least one side edge of the secondary grid is extended to the direction of the source electrode or the drain electrode, and meanwhile orthographic projection of the secondary grid is overlapped with the two side edges of the main grid. The ''current collapse effect'' can be substantially and effectively inhibited by the III nitride MISHEMT device.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

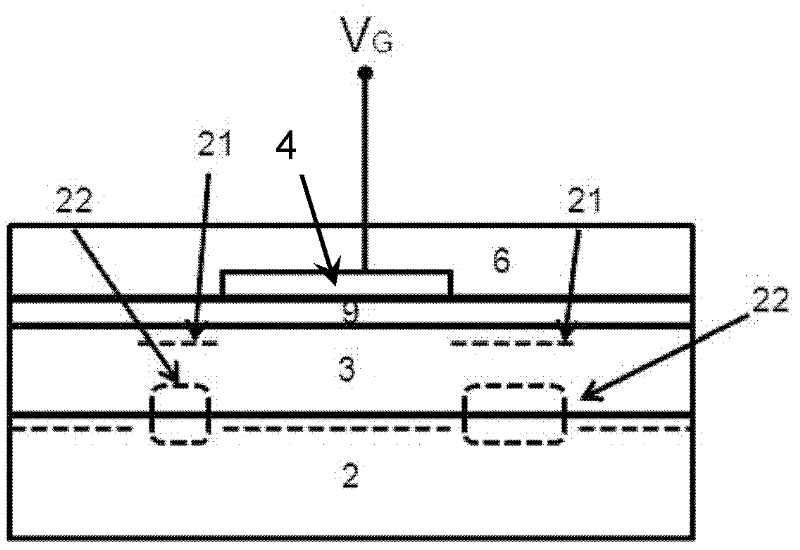

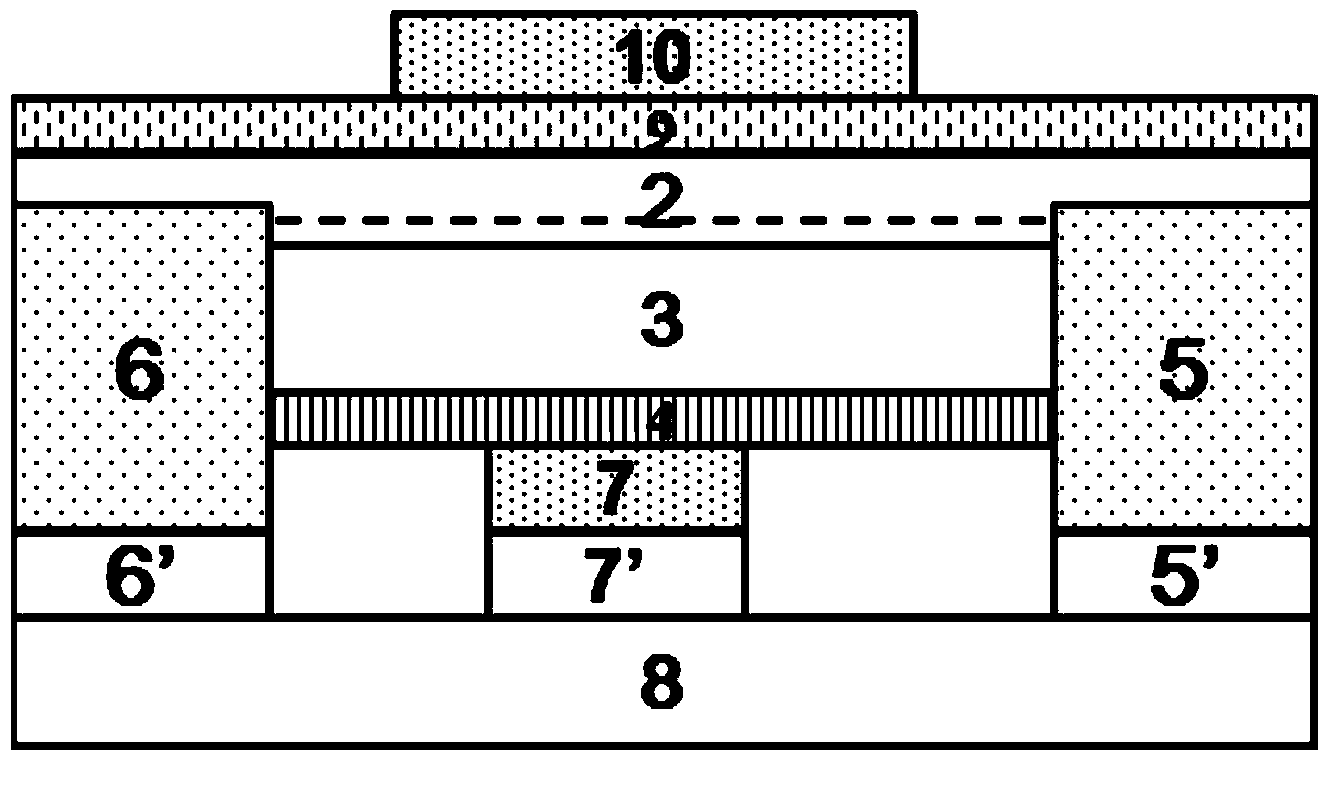

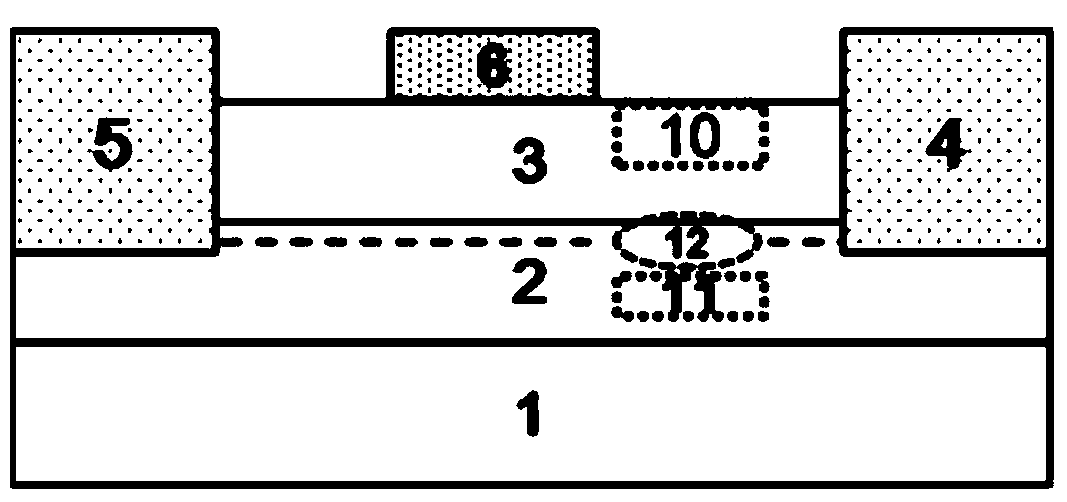

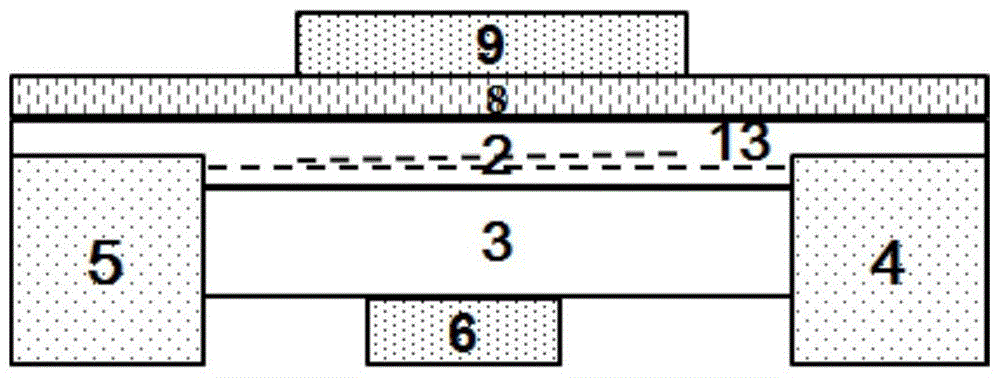

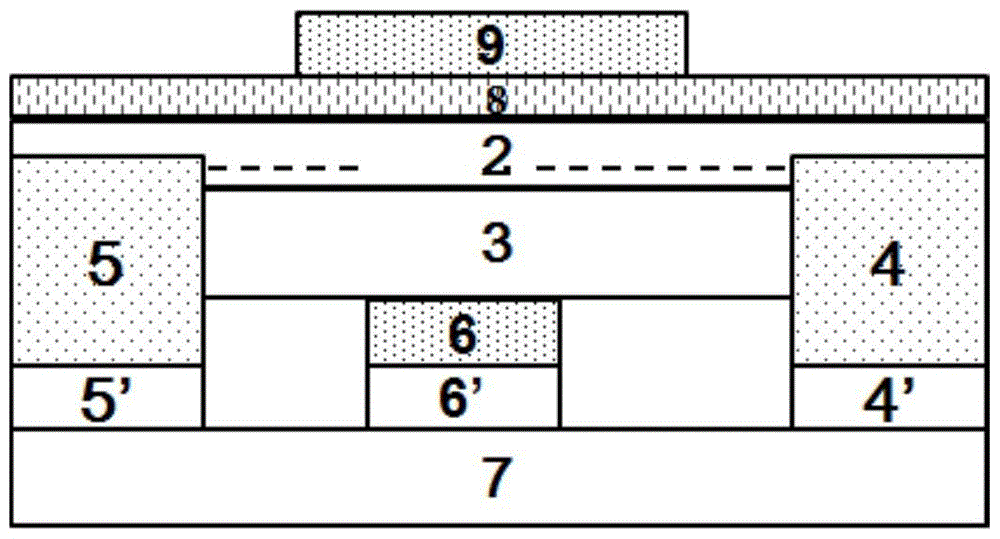

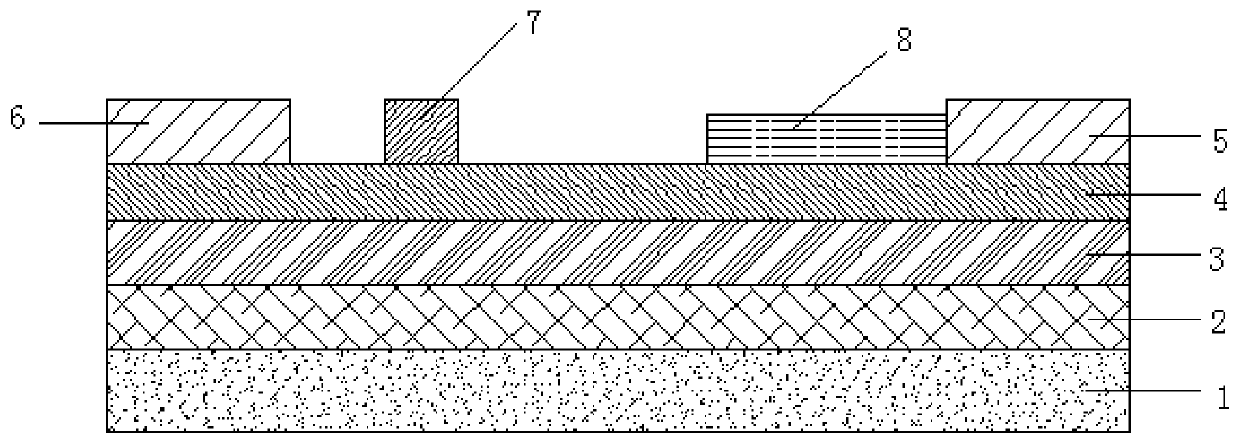

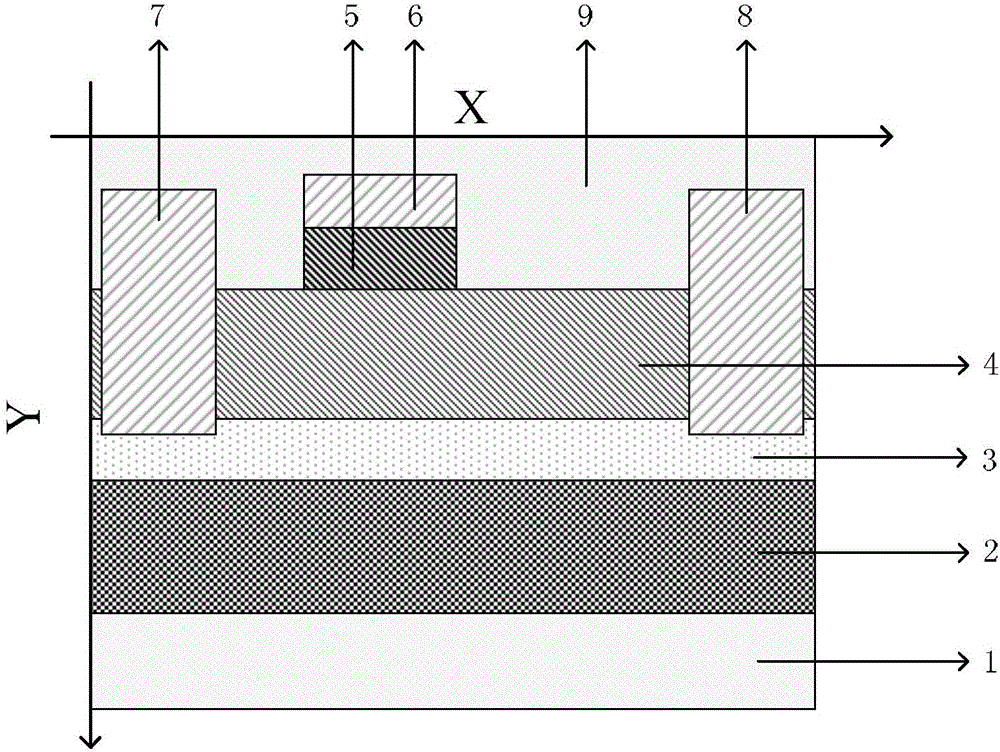

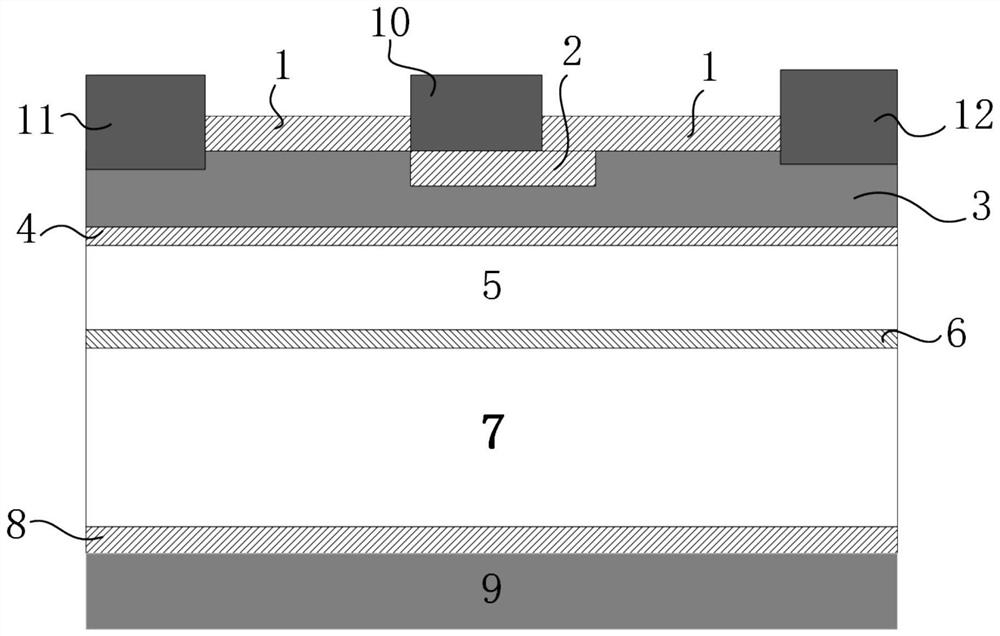

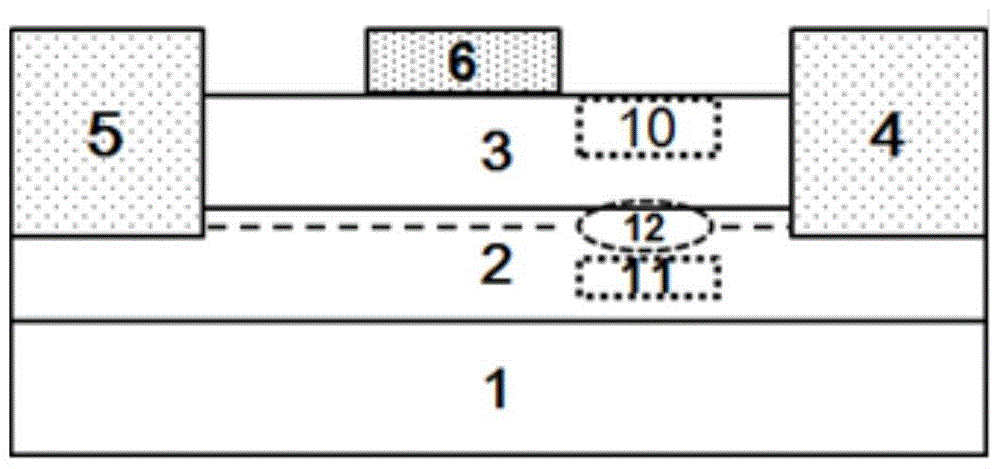

HEMT device with back surface field plate structure and manufacturing method of HEMT device

ActiveCN103715257AEffective regulationSuppression of avalanche effectsSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionDevice material

The invention discloses an HEMT device with a back surface field plate structure and a manufacturing method of the HEMT device. The device can be manufactured through a common semiconductor device machining technology. The device comprises a source electrode, a drain electrode, a heterostructure and a back field plate electrode. The source electrode and the drain electrode electrically connected through two-dimensional electron gas formed in the heterostructure, the source electrode, the drain electrode and the heterostructure form ohmic contact, the heterostructure comprises a first semiconductor layer and a second semiconductor layer which are arranged in sequence in the setting direction, the first semiconductor layer is arranged between the source electrode and the drain electrode, a grid electrode is arranged on the surface of the first semiconductor layer, Schottky contact is formed between the grid electrode and the first semiconductor layer, and the back field plate electrode is arranged on the surface of one side, far away from the first semiconductor layer, of the second semiconductor. The puncture voltage of the device can be effectively improved, and the effect of electric current collapsing can be restrained to the maximum degree.

Owner:江苏盐综产业投资发展有限公司

Crystal tube structure with high electronic shifting ratio of gallium nitrate base of double heterogenous structure and mfg. method thereof

InactiveCN1787229AControl leakageIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceGallium nitride

The invention is a double-heterostructured GaN-base high-electron migration rate transistor structure, characterized in comprising: a sapphire, silicon carbide or silicon substrate; a high resistance GaN buffer layer made on the substrate; a thin unpurposed doped GaN insert layer made on the buffer layer; a high-migration rate GaN channel layer made on the thin unpurposed doped GaN insert layer; a thin AlN insert layer made on the channel layer; a n-type doped or unpurposed doped Al-Ga-N barrier layer made on the thin AlN insert layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

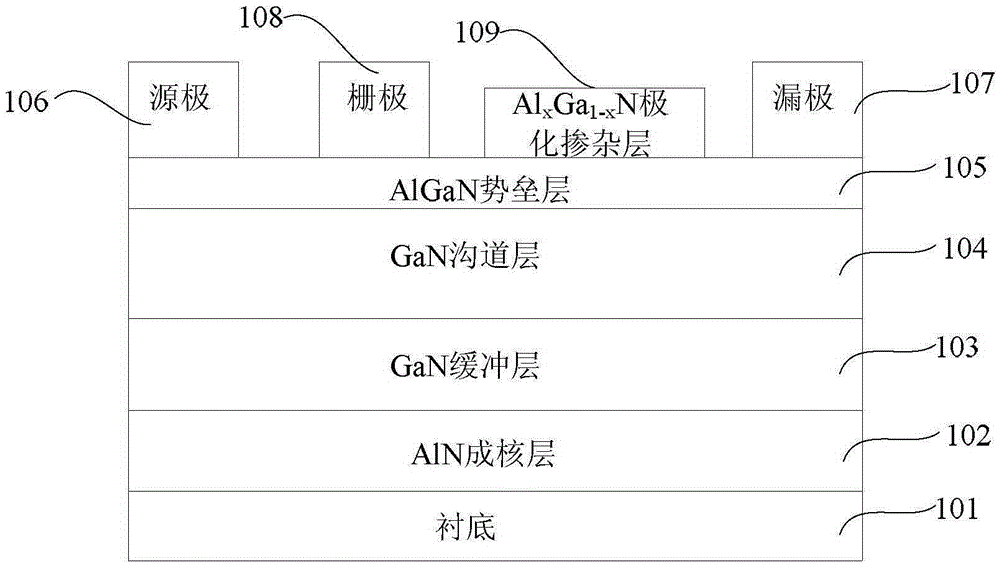

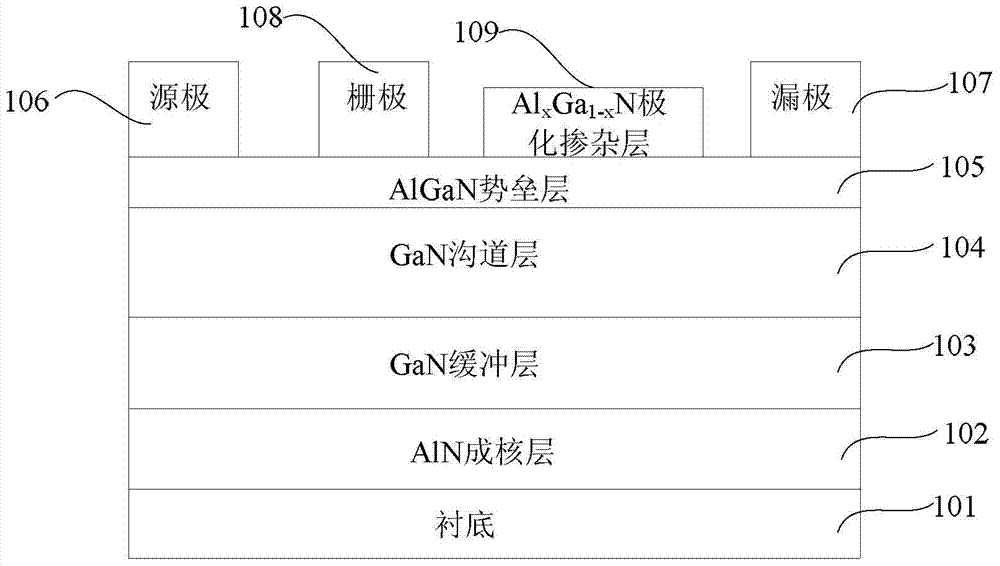

High-breakdown-voltage GaN-based high-electron-mobility transistor

ActiveCN105261643AImprove thermal stabilityImprove reliabilitySemiconductor devicesNucleationGallium nitride

The invention relates to a high-breakdown-voltage GaN-based high-electron-mobility transistor, which mainly comprises a substrate, an AlN nucleation layer, a GaN buffer layer, a GaN channel layer, a AlGaN barrier layer, a source electrode, a drain electrode and a grid electrode, wherein the above layers are successively arranged from bottom to top and the source electrode, the drain electrode and the grid electrode are formed on the AlGaN barrier layer. The high-breakdown-voltage GaN-based high-electron-mobility transistor is characterized by further comprising an AlxGa1-xN polarization doped layer positioned on the AlGaN barrier layer and between the grid electrode and the drain electrode, with the content of Al component to be gradually changed. The content of Al component in the AlxGa1-xN polarization doped layer is linearly increased from top to bottom. The three-dimensional hole gas generated caused by he gradually changing content of Al component and the two-dimensional electron gas of the channel layer compensate each other to form a charge self-balancing type super-junction structure. In this way, the charge imbalance problem is solved. Meanwhile, the breakdown voltage and the stability of equipment are improved.

Owner:南京绿能芯耀科技有限公司

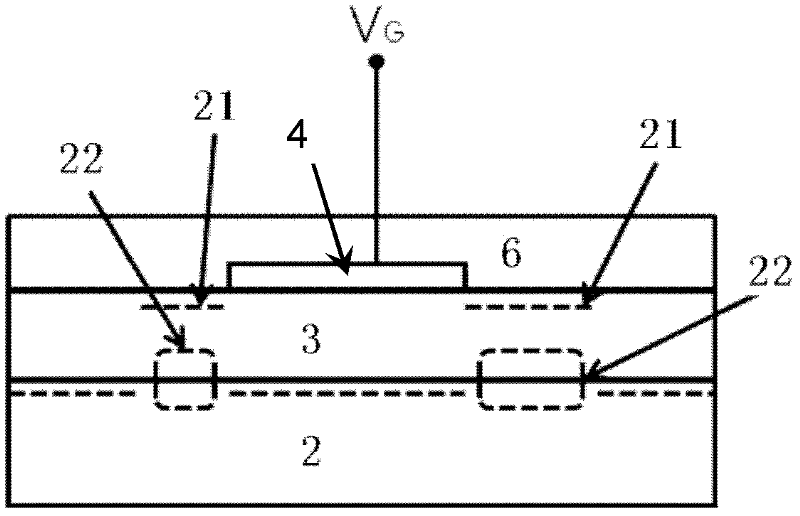

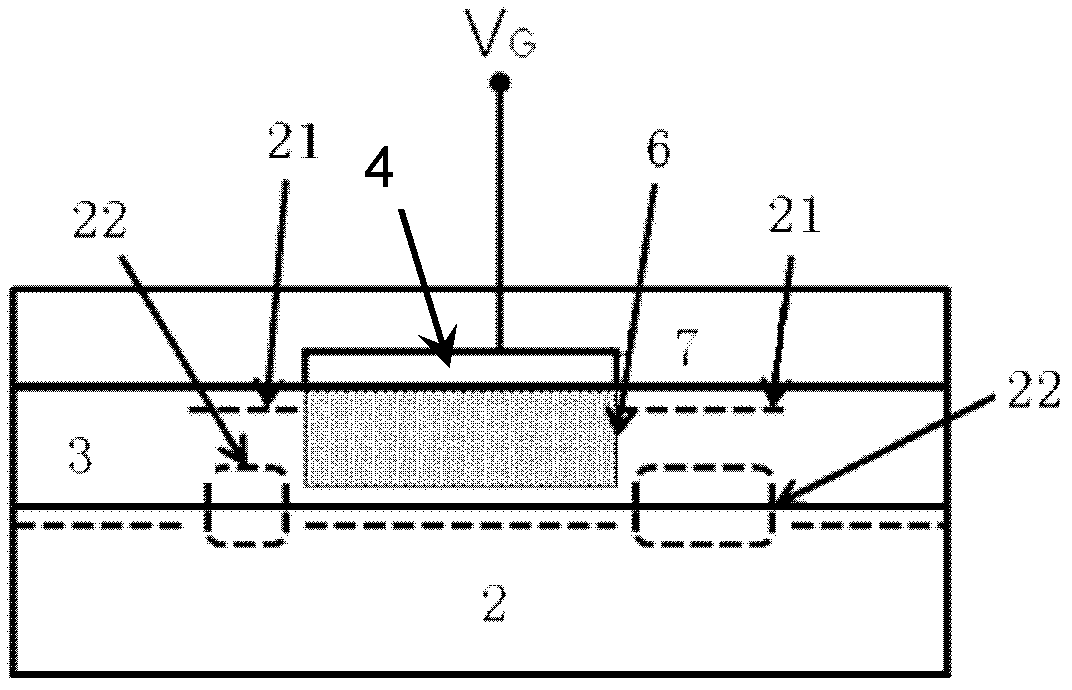

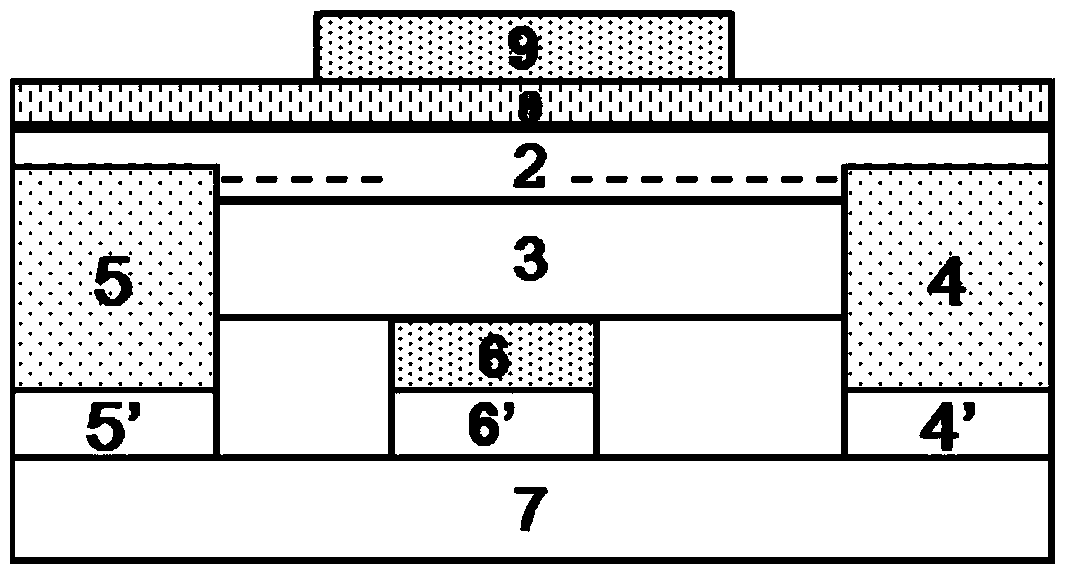

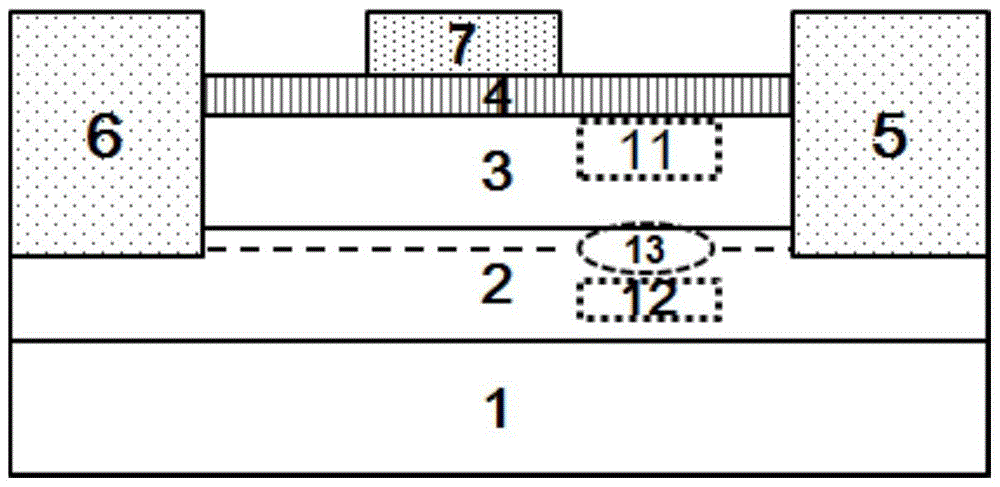

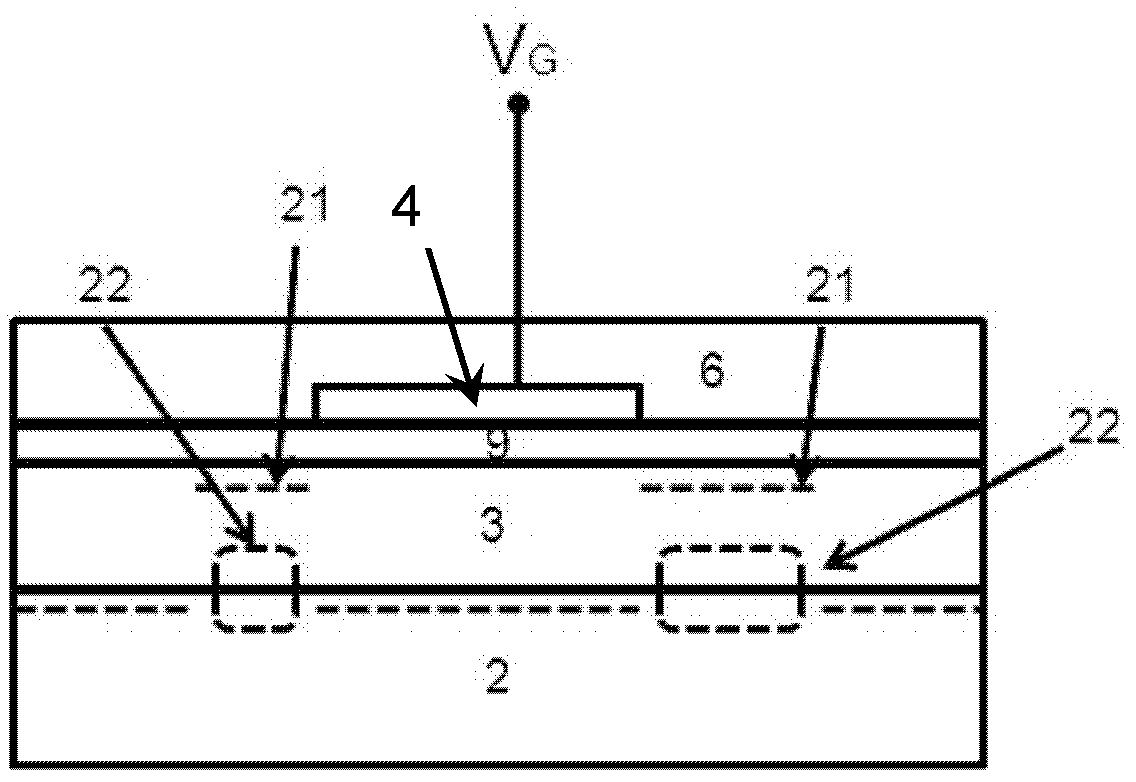

Group-III nitride HEM (High Electron Mobility Transistor) device

The invention discloses a Group-III nitride HEM (High Electron Mobility Transistor) device which comprises a source electrode, a drain electrode, a main grid, an auxiliary grid, an insulating dielectric layer and a heterojunction structure; the source electrode and the drain electrode are electrically connected through two-dimension electron gas formed in the heterojunction structure; the heterojunction structure comprises a first semiconductor and a second semiconductor; the second semiconductor is formed on the surface of the first semiconductor and is provided with a band gap wider than the first semiconductor; the first semiconductor is arranged between the source electrode and the drain electrode; the main grate is arranged on the surface of the second semiconductor near one side of source electrode and is in schottky contact with the second semiconductor; the dielectric layer is formed on the second semiconductor and the surface of the main grid and is arranged between the source electrode and the drain electrode; the auxiliary grid is formed on the surface of the dielectric layer; at least one side edge of the auxiliary grid is extended toward the direction of the source electrode or the drain electrode; meanwhile, an orthographic projection of the auxiliary grid are overlapped with two side edges of the main grate. The Group-III nitride HEM device can fundamentally and effectively inhibit 'Current Collapse Effect'.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

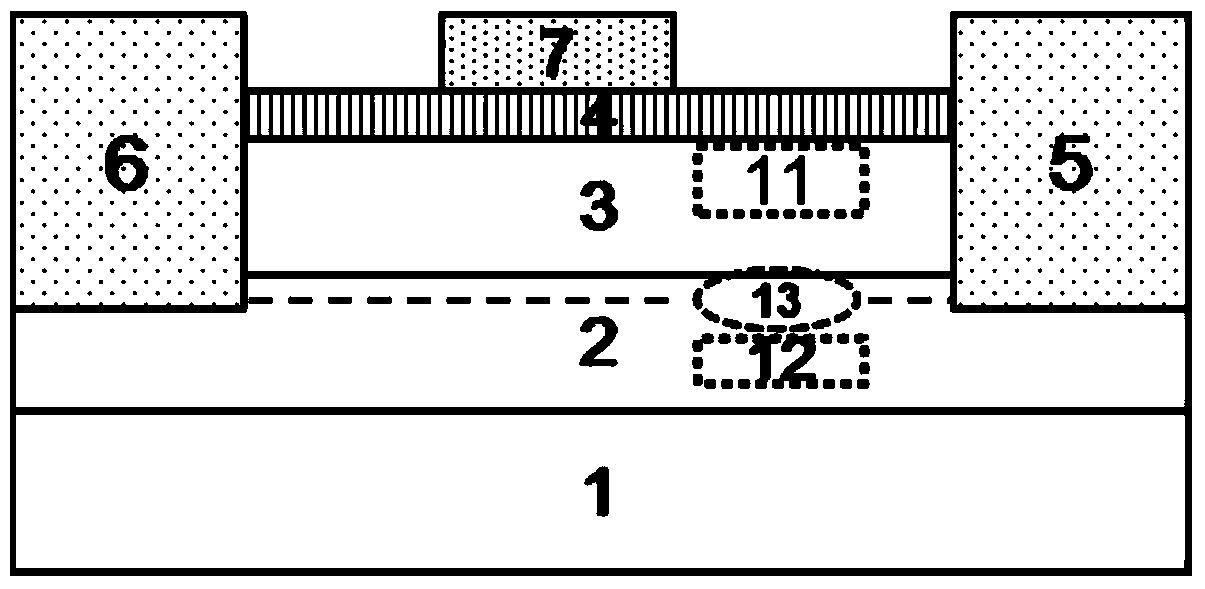

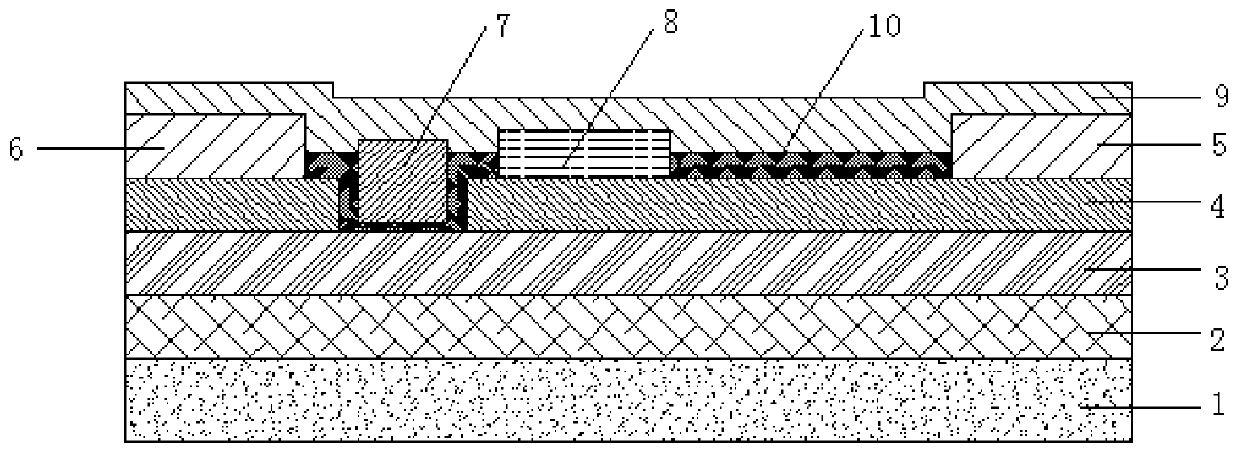

Group III nitride enhancement mode HEMT (High Electron Mobility Transistor) device

InactiveCN102427085ASuppression of avalanche effectsSemiconductor devicesElectrical conductorMedia layer

The invention discloses a group III nitride enhancement mode HEMT (High Electron Mobility Transistor) device which comprises source and drain electrodes, main and accessory grids, an insulating medium layer and a heterostructure, wherein the source and drain electrodes are electrically connected by two-dimensional electron formed in the heterostructure; the heterostructure comprises a first semiconductor and a second semiconductor; the first semiconductor is arranged between the source and drain electrodes; the second semiconductor is formed on the surface of the first semiconductor and is provided with a band gap which is wider than the first semiconductor; the main grid is arranged at one side of the surface of the second semiconductor near the source electrode and forms schottky contact with the second semiconductor, and a plasma processing area is also formed in the local area of the second semiconductor under the main grid; a medium layer is formed on the surfaces of the second semiconductor and the main grid and between the source and drain electrodes; and the accessory grid is formed on the surface of the medium layer, the edge of at least one side of the accessory grid extends to the direction of the source electrode or drain electrode, and the orthographic projection of the accessory grid is laminated with the edges of both sides of the main grid. The group III nitride enhancement mode HEMT device can effectively inhibit the current collapse effect fundamentally.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

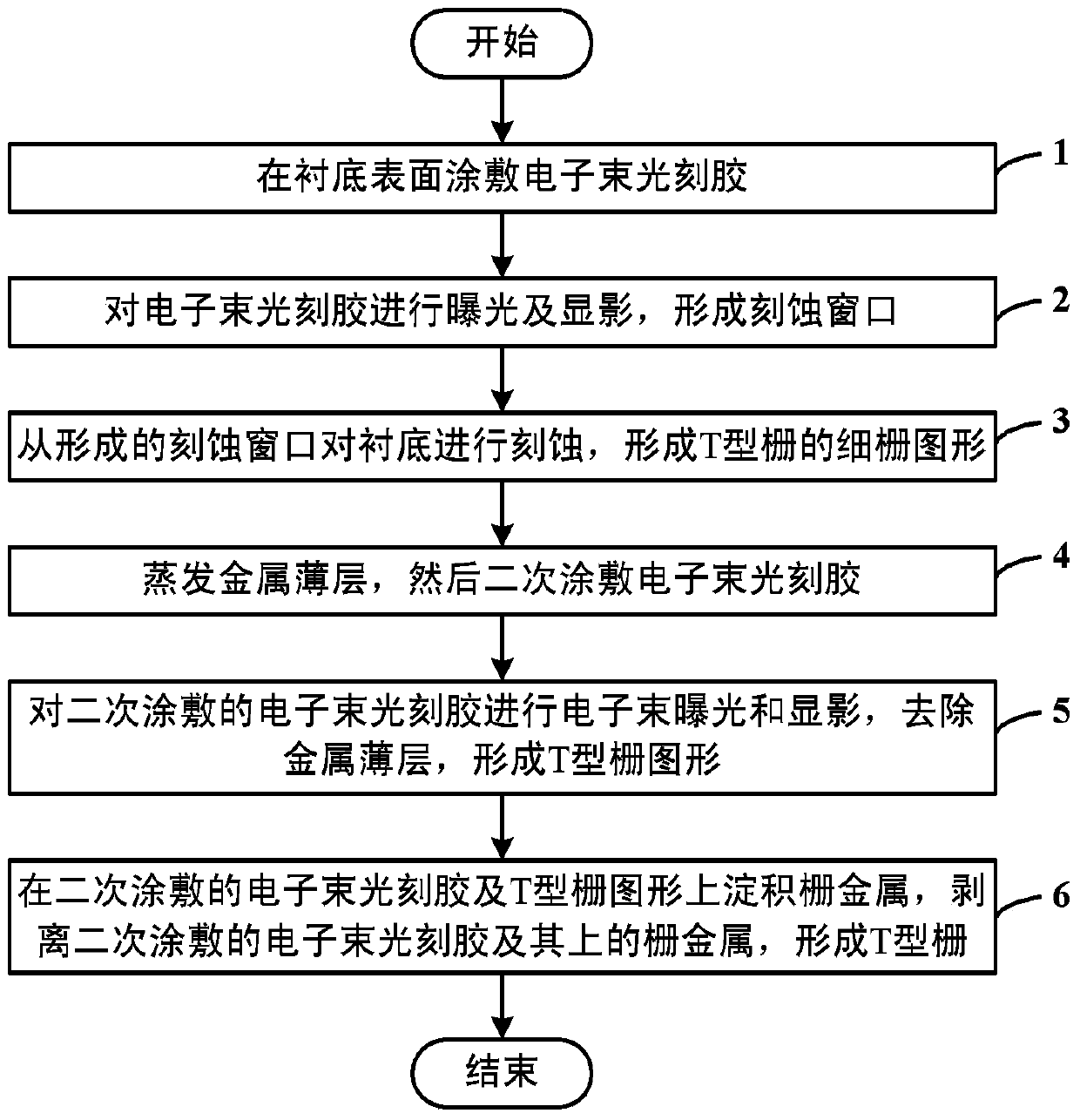

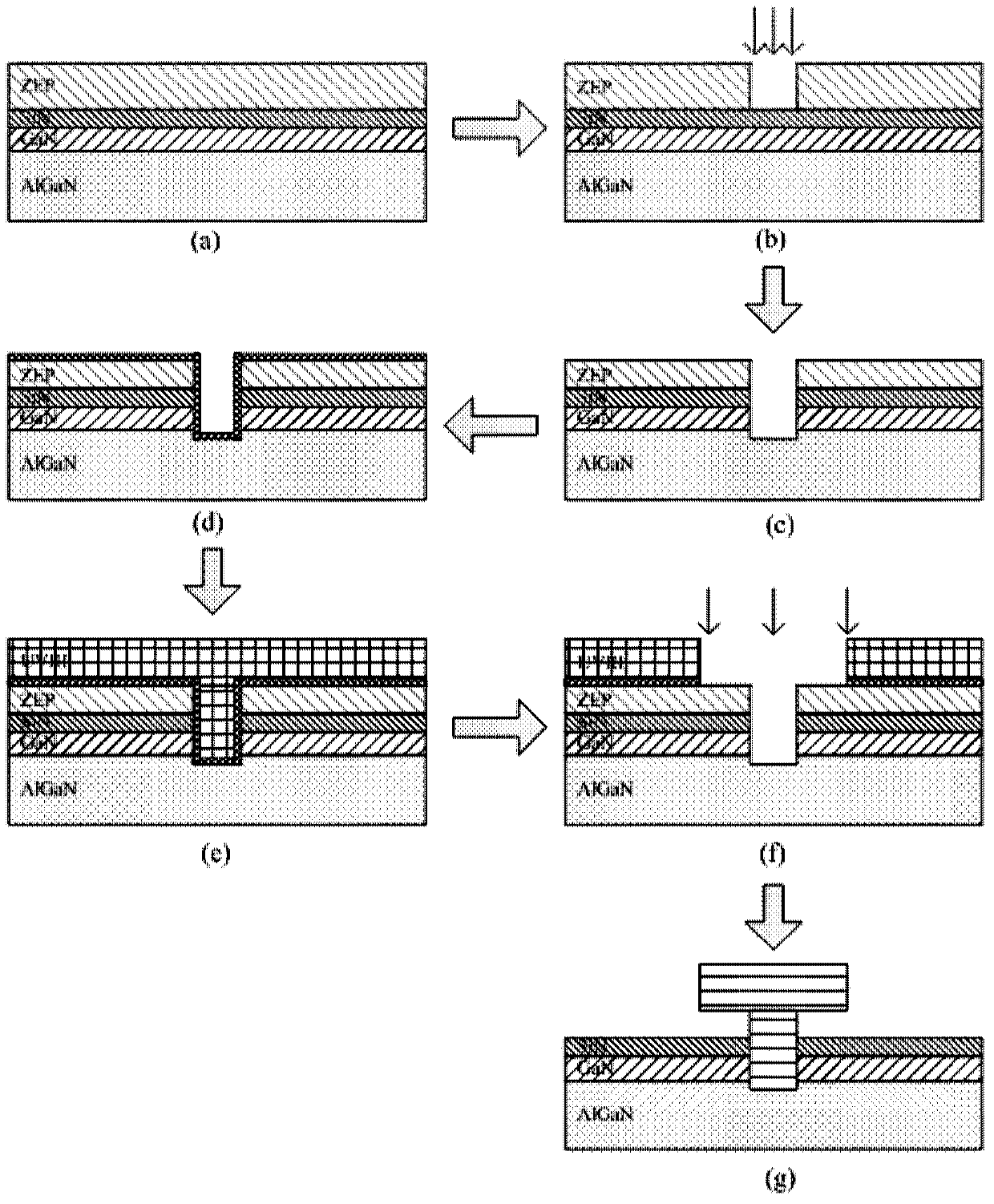

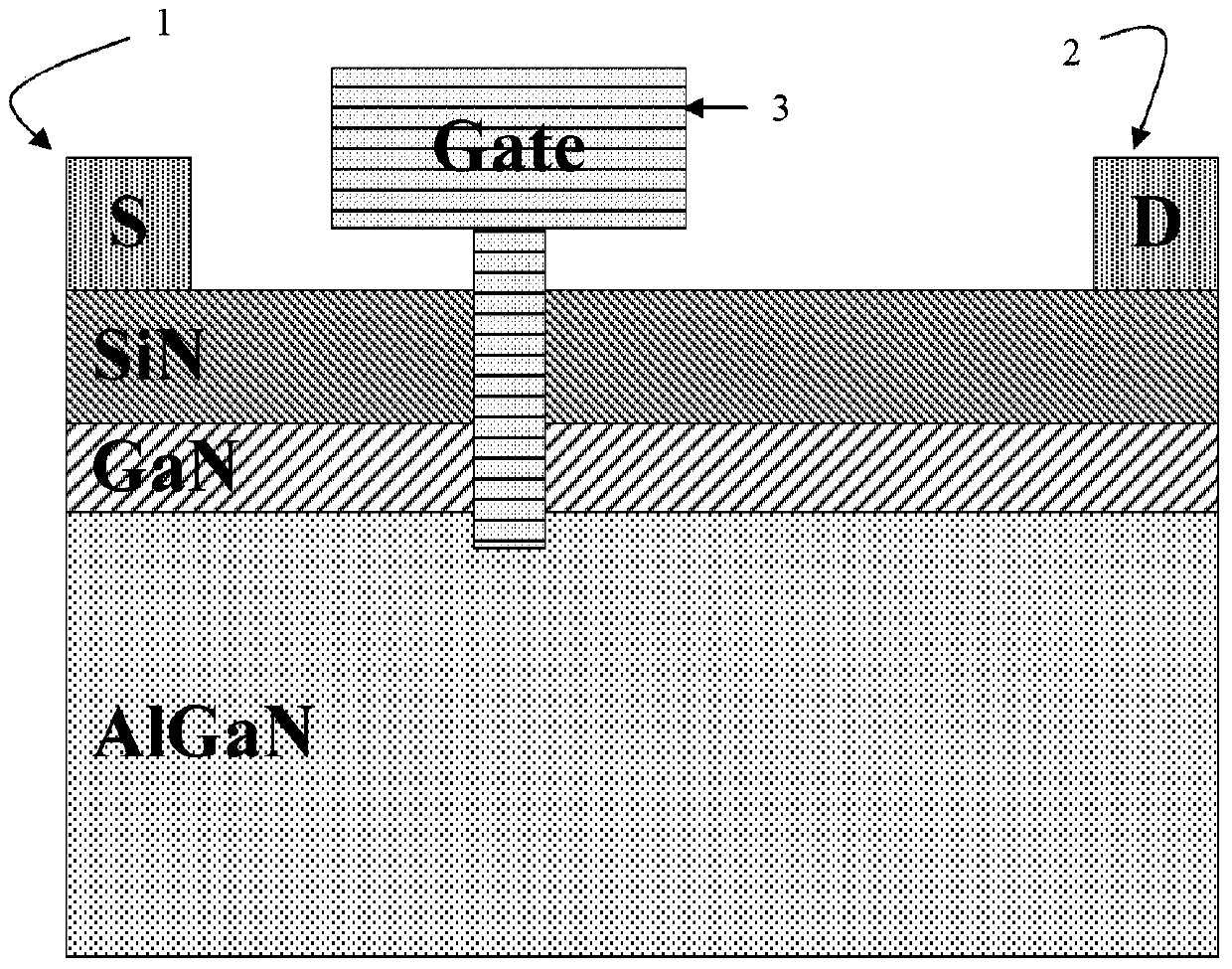

Manufacturing method of T-shaped gate of GaN-based FET (Field Effect Transistor)

InactiveCN103700583AReduce parasitic capacitanceImprove frequency characteristicsSemiconductor devicesParasitic capacitanceThin layer

The invention discloses a manufacturing method of a T-shaped gate of a GaN-based FET (Field Effect Transistor). The manufacturing method comprises the steps of coating an electron beam photoresist on the surface of a substrate; carrying out exposure and development on the electron beam photoresist, and forming an etching window; etching the substrate from the formed etching window, and forming a fine gate graph of the T-shaped gate; evaporating a metal thin layer, and then secondly coating the electron beam photoresist; carrying out electron beam exposure and development on the electron beam photoresist which is secondly coated, removing the metal thin layer, and forming a T-shaped gate graph; evaporating deposited gate metal on the electron beam photoresist which is secondly coated and the T-shaped gate graph, stripping the electron beam photoresist which is secondly coated and the gate metal on the electron beam photoresist which is secondly coated, and forming the T-shaped gate. By utilizing the manufacturing method disclosed by the invention, the current collapse is effectively restrained, the stray capacitances of a gate source and a gate drain are reduced, the gate resistance of a device is reduced, the cut-off frequency (ft) and the maximum oscillation frequency (fmax) of the device are increased, and thus the device can work in an MMW (Millimeter Wave) frequency band.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

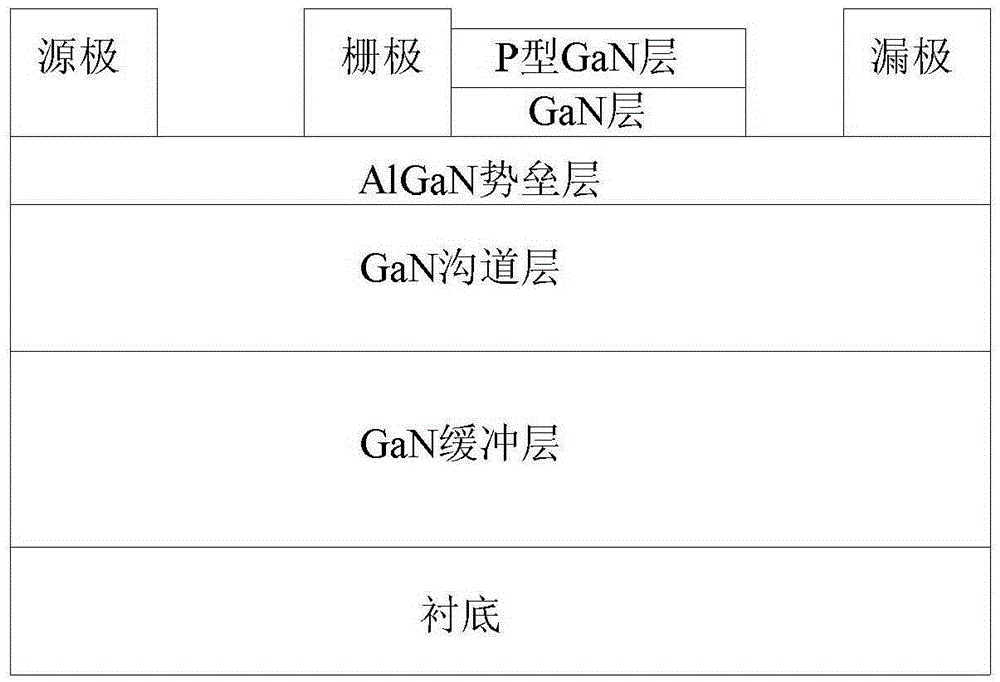

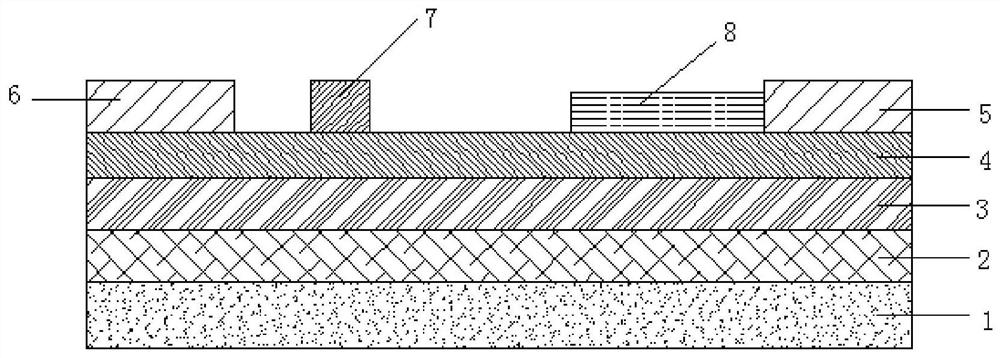

Gallium nitride power device with multi-field plate structure, and preparation method thereof

ActiveCN111370483AImprove pressure resistanceImprove breakdown resistanceEfficient power electronics conversionSemiconductor/solid-state device manufacturingElectrode insertionEngineering

The invention discloses a gallium nitride power device with a multi-field plate structure. The gallium nitride power device is sequentially provided with a substrate, a nucleating layer, a buffer layer, a first insertion layer, a first GaN layer, a second insertion layer, a second GaN layer, an AlGaN barrier layer, a passivation layer, a grid electrode field plate, a drain electrode field plate, aprotective layer, a grid electrode insertion layer, a p-type GaN grid electrode, a grid electrode metal, a source electrode metal and a drain electrode metal from bottom to top, wherein the passivation layer located on the surface of the AlGaN barrier layer is in a strip shape arranged at intervals, the grid electrode field plate and the drain electrode field plate respectively cover part of thepassivation layer, and the surfaces of the grid electrode field plate and the drain electrode field plate and the space between the grid electrode field plate and the drain electrode field plate are covered with the protective layer. According to the invention, the electric field distribution is uniform, the voltage endurance capability of the device is enhanced, the stability of grid electrode turn-on voltage and grid electrode voltage of the device is effectively improved, and the electric leakage of the device under the action of large current is effectively reduced. The preparation methodis completely compatible with a traditional process, and the preparation difficulty is low.

Owner:CHANGSHU INSTITUTE OF TECHNOLOGY

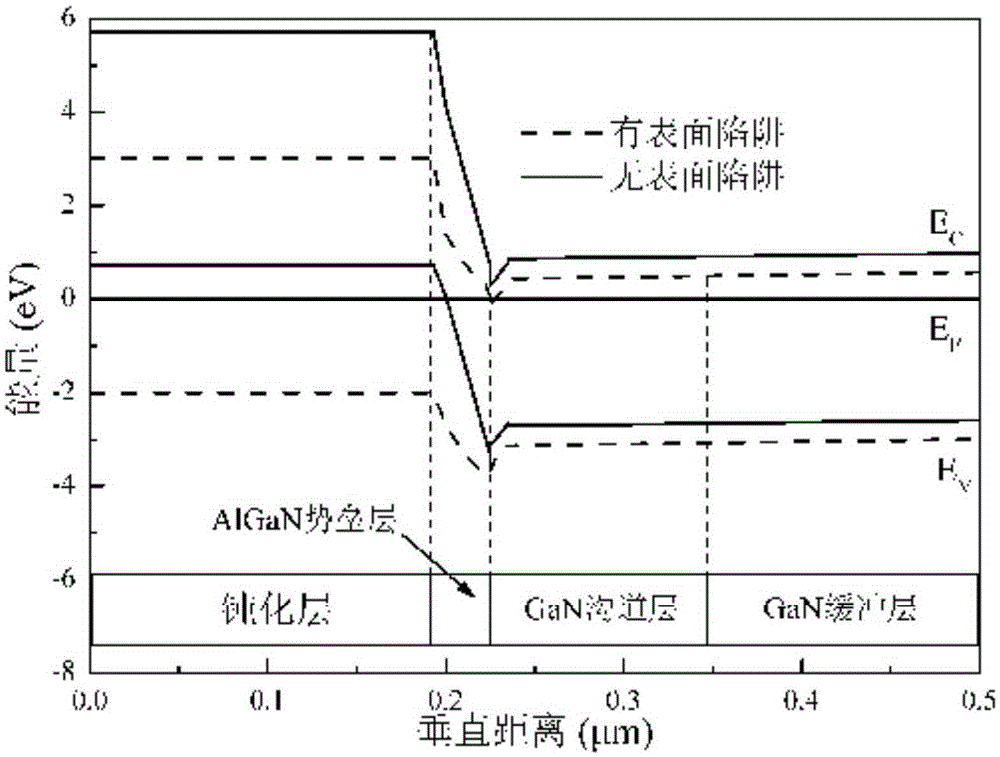

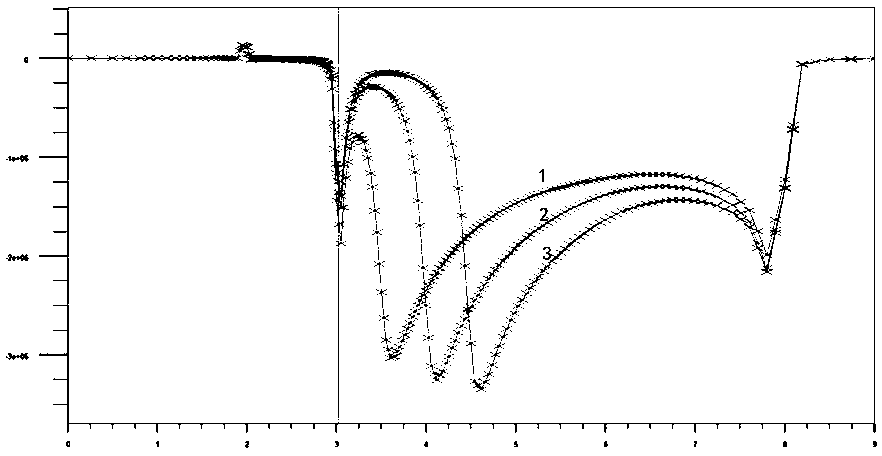

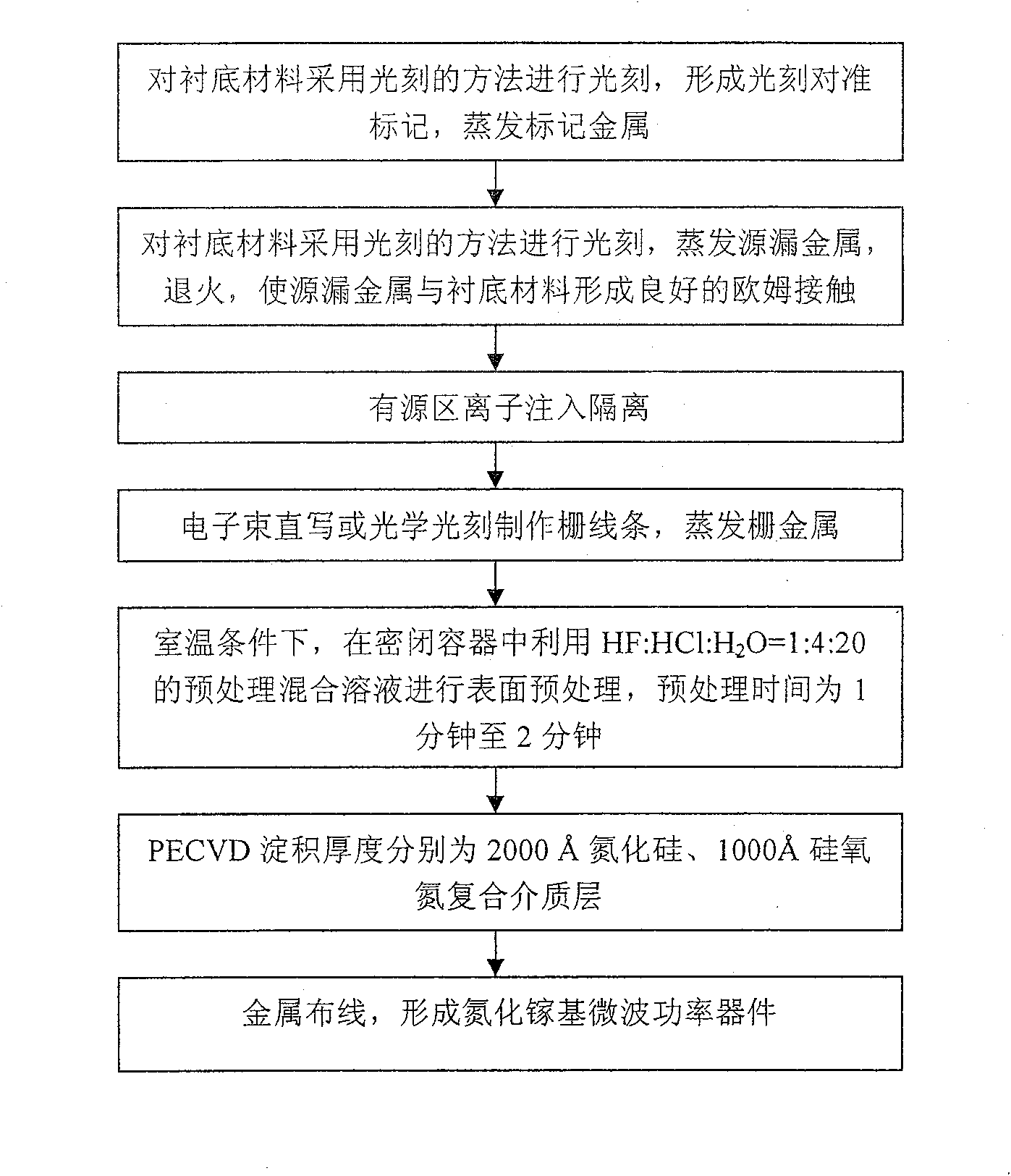

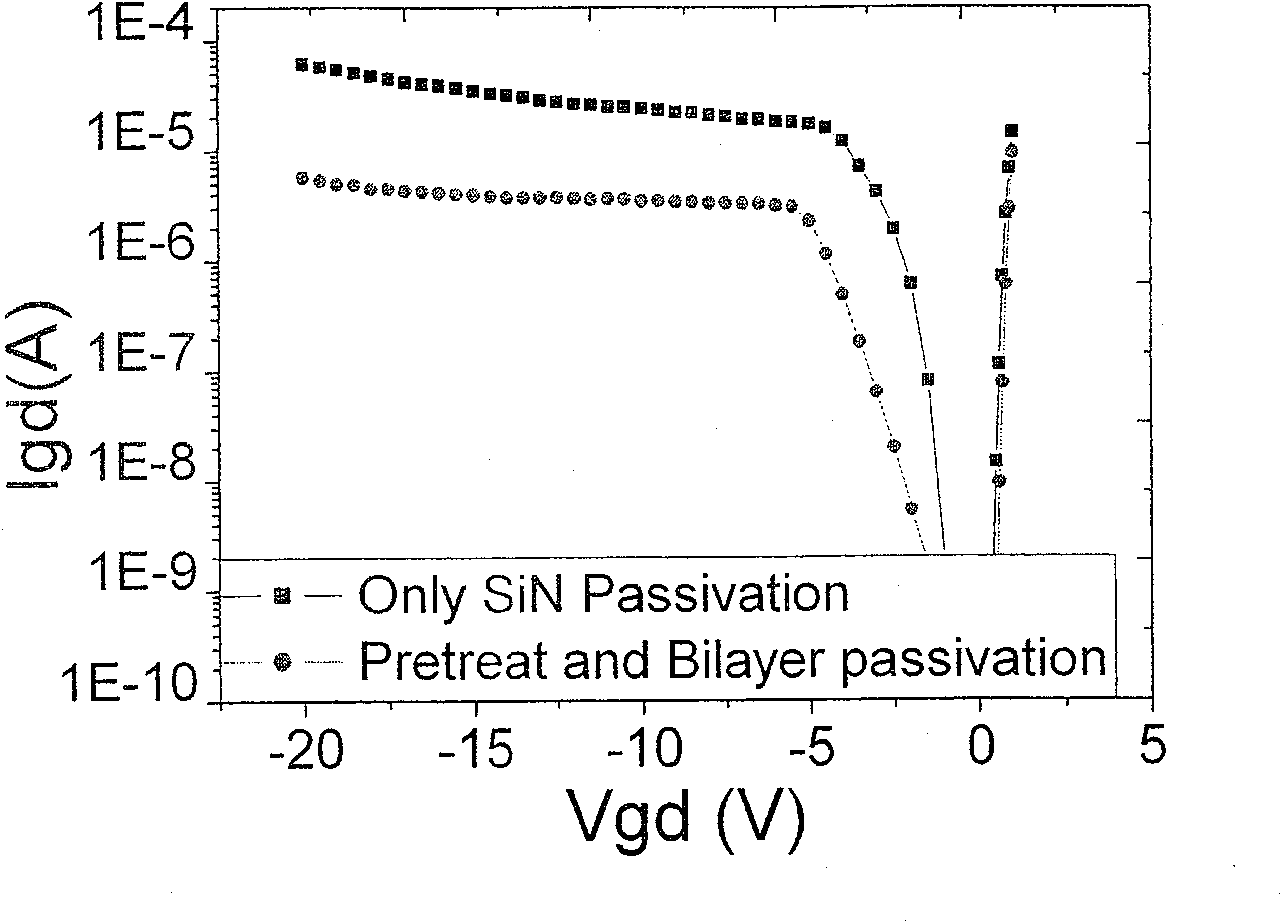

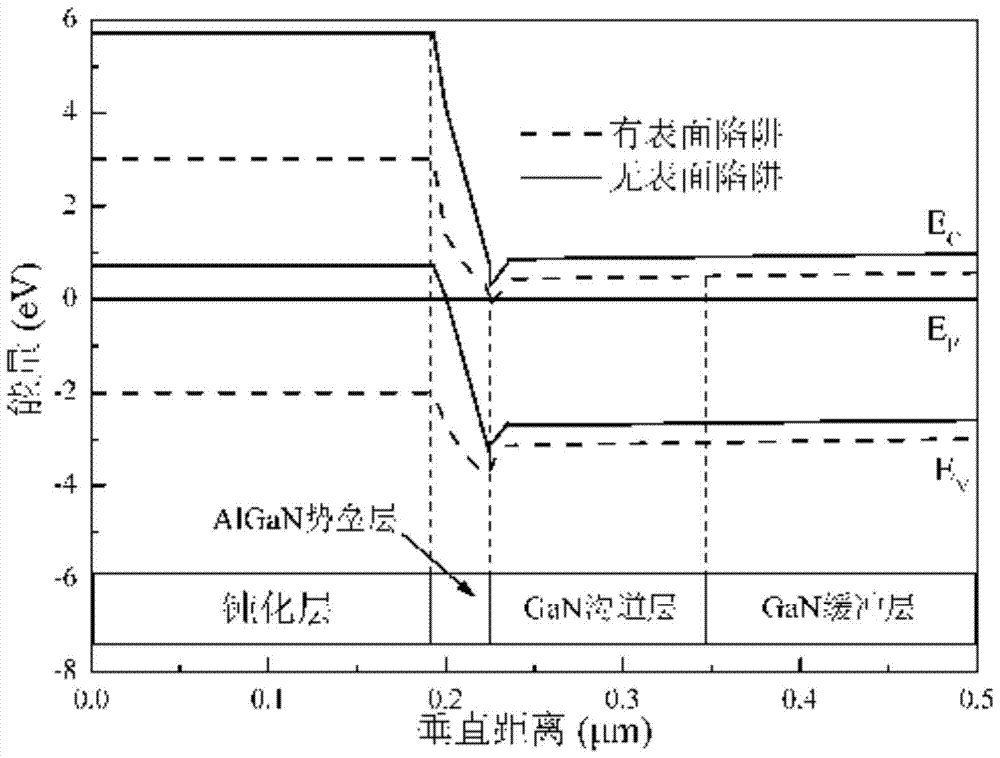

Method for improving the performance of gallium nitride based field effect transistor

InactiveCN100594591CSolve the current collapse effectSolve the collapse effectSemiconductor/solid-state device manufacturingSemiconductor materialsSurface oxidation

The invention relates to the technical field of production of wide bandgap semiconductor materials and devices and discloses a method for improving the performance of a GaN-based field-effect transistor, the method comprises: mixed pre-treatment solution is adopted to carry out the surface pre-treatment of the surface of a device before the passivation of the GaN-based field-effect transistor during the production process of the GaN-based field-effect transistor, then a compound dielectric layer of silicon nitride and oxygen-rich silicon nitride is deposited on the surface of the device afterthe surface pre-treatment, and the GaN-based field-effect transistor is passivated. The use of the method can solve a surface original oxide layer which is existed on the surface of AlGaN for a long time, eliminate the AlGaN surface state which is induced by the surface oxide layer, solve the surface state existing in an AlGaN and silicon nitride interface, the current collapse effect which is induced by the surface original oxide layer and the significant increase of the reverse gate leakage current caused by the conventional passivation and improve the stability and the reliability of GaN-based HEMT.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Structure of improving gallium nitride base high electronic mobility transistor property and producing method

InactiveCN100397655CIncrease concentrationImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceGallium nitride

A structure is for increasing performance of transistors of GaN base high electronic movability includes: a sapphire substrate, a SiC2 substrate or a silicon substrate, a high resistance semi-insulation GaN buffer layer processed on the substrate, a high movability GaN channel layer processed on the buffer layer, a thin ALN plug-in layer processed on the channel layer to increase the integrated performance of the transistor materials of GaN base high electronic movability, a n-type doped or un-purpose doped ALGaN barrier layer processed on the thin ALN plug-in layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

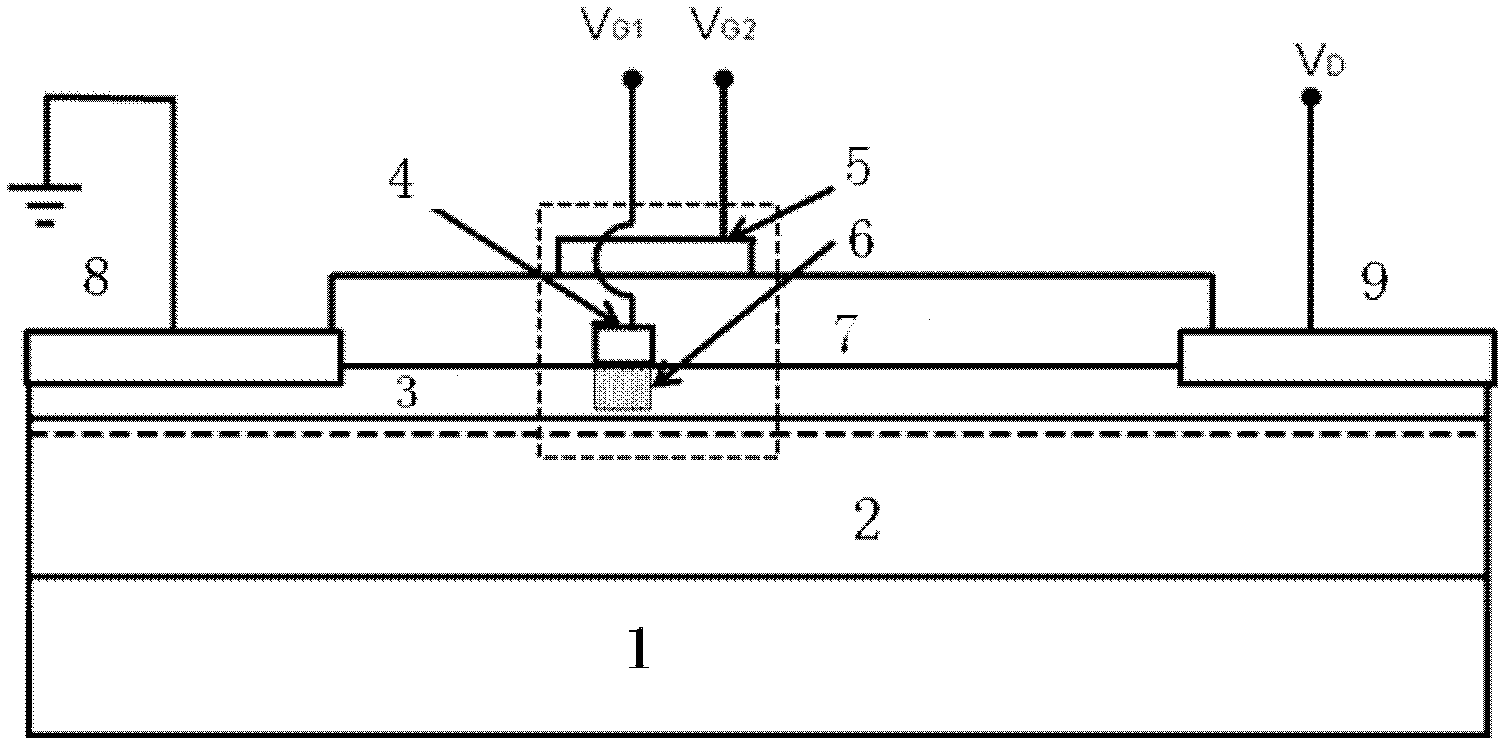

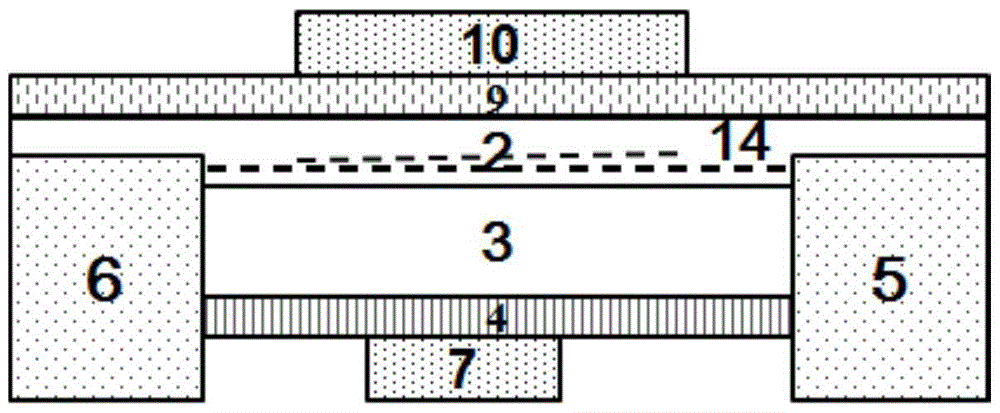

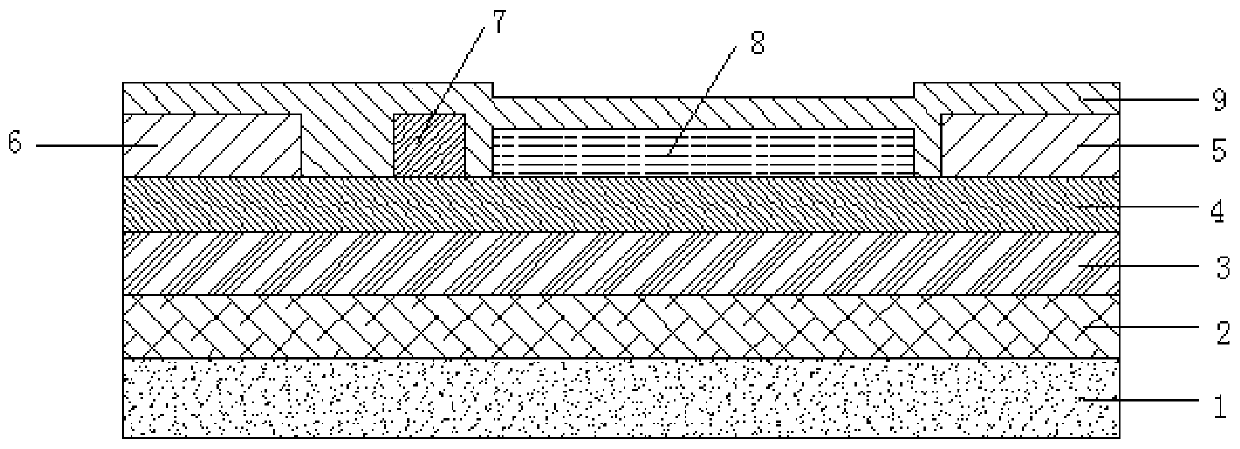

MIS-HEMT (metal insulating layer-high electron mobility transistor) device with back field plate structure and preparation method thereof

ActiveCN103730492ASimple structureEffective regulationSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionDevice material

The invention discloses an MIS-HEMT device with a back field plate structure and a preparation method thereof. The MIS-HEMT device with the back field plate structure can be manufactured through the commonly seen semiconductor device processing technology and comprises a source electrode, a drain electrode, a heterostructure and a back field plate electrode, wherein the source electrode and the drain electrode are electrically connected through two-dimensional electronic gas in the heterostructure, and the source electrode, the drain electrode and the heterostructure are of an ohmic contact mode; the heterostructure comprises a first semiconductor layer and a second semiconductor layer which are sequentially arranged in a set direction, the first semiconductor layer is arranged between the source electrode and the drain electrode, the surface of the first semiconductor layer is provided with a grid electrode, and a first insulating medium layer is arranged between the grid electrode and the first semiconductor layer to form an MIS structure; the back field plate electrode is arranged on the surface of the second semiconductor layer, which is away from the first semiconductor layer. The MIS-HEMT device with the back field plate structure can effectively increase the breakdown voltage of the device and restrain the current collapse effect to the largest extent.

Owner:SUZHOU NENGWU ELECTRONICS TECH

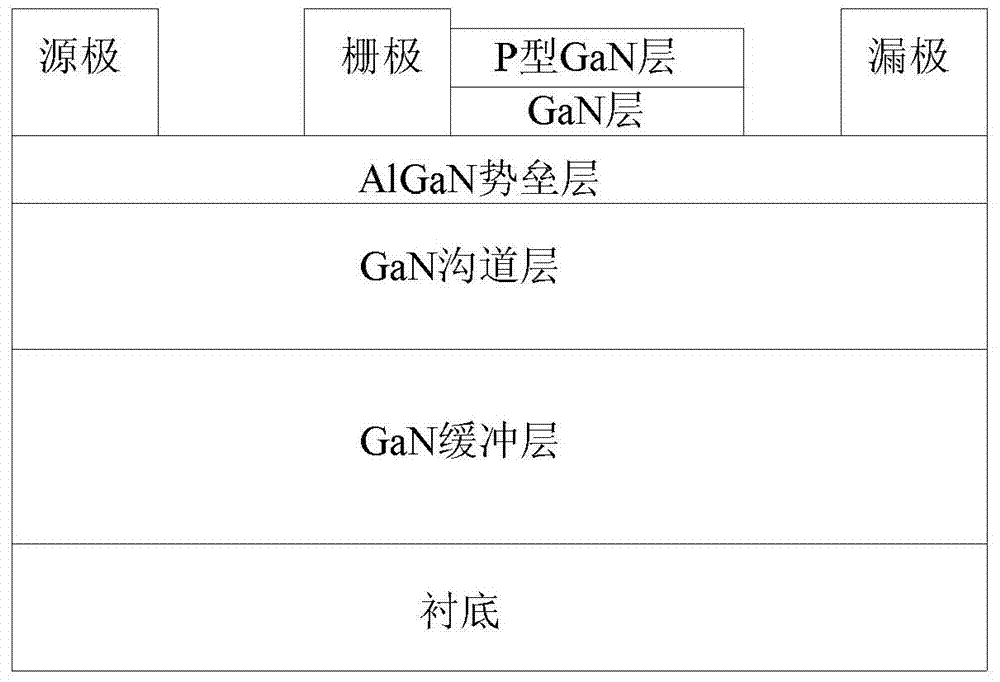

Normally-closed gallium nitride HEMT device

PendingCN108493245AIncrease output currentSuppression of avalanche effectsSemiconductor devicesElectrical conductorGallium nitride

The invention provides a normally-closed gallium nitride HEMT device. The device comprises a heterostructure as well as a source electrode, a drain electrode and grid electrode which are connected with the heterostructure, wherein the heterostructure comprises a first semiconductor layer as a channel layer; a second semiconductor layer as a barrier layer is formed on the first semiconductor layer;a p-type semiconductor layer is formed between the second semiconductor layer and the grid electrode, two-dimensional electron gas is produced between the first semiconductor layer and the second semiconductor layer and disappears right below the p-type semiconductor layer; and a dielectric layer as a passivation layer is settled on the upper surface of the heterostructure, and pre-selected metalions are injected into the dielectric layer right above a region in which the two-dimensional electron gas usually exits. By virtue of each embodiment provided by the invention, the density of the two-dimensional electron of the normally-closed HEMT device can be effectively increased.

Owner:JIANGSU CORENERGY SEMICON CO LTD

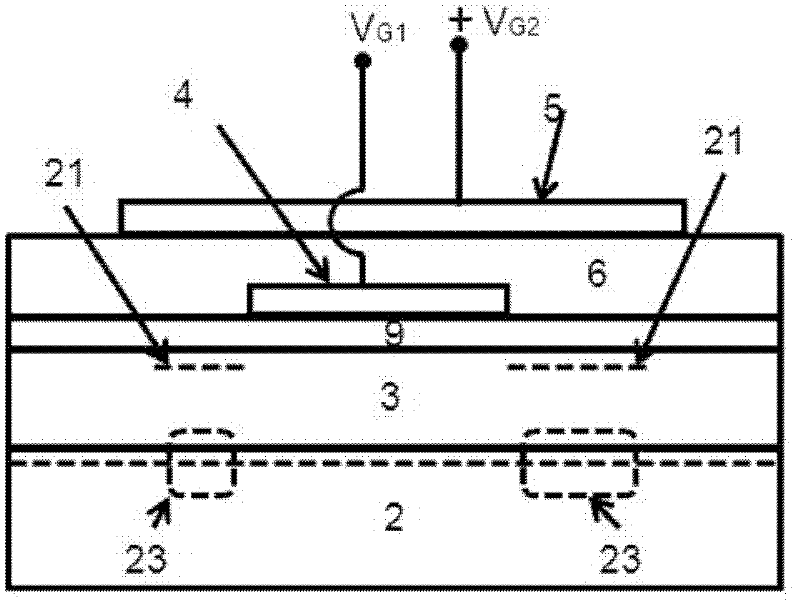

Enhanced HEMT (high electron mobility transistor) device with back field plate structure and preparation method thereof

ActiveCN103730360AInhibition of current collapse effectImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHigh-electron-mobility transistorOhmic contact

The invention discloses an enhanced HEMT device with a back field plate structure and a preparation method thereof. The enhanced HEMT device with the back field plate structure can be manufactured through the commonly seen semiconductor device processing technology and comprises a source electrode, a drain electrode, a heterostructure and a back field plate electrode, wherein the source electrode and the drain electrode are electrically connected through two-dimensional electronic gas in the heterostructure, and the source electrode, the drain electrode and the heterostructure are of an ohmic contact mode; the heterostructure comprises a first semiconductor layer and a second semiconductor layer which are sequentially arranged in a set direction, the first semiconductor layer is arranged between the source electrode and the drain electrode, and the surface of the first semiconductor layer is provided with a grid electrode; a two-dimensional electron gas depletion area is arranged in the area inside the heterostructure, which corresponds to the grid electrode; the grid electrode is in Schottky contact with the first semiconductor layer; the back field plate electrode is arranged on the surface of the second semiconductor layer, which is away from the first semiconductor layer. The enhanced HEMT device with the back field plate can effectively increase the breakdown voltage of the device and restrain the current collapse effect to the largest extent.

Owner:江苏盐综产业投资发展有限公司

Enhanced hemt device with back field plate structure and preparation method thereof

ActiveCN103730360BSimple structureEffective regulationSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorOhmic contact

Owner:江苏盐综产业投资发展有限公司

Mis-hemt device with back field plate structure and preparation method thereof

ActiveCN103730492BSimple structureEffective regulationSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorOhmic contact

The invention discloses an MIS-HEMT device with a back field plate structure and a preparation method thereof. The MIS-HEMT device with the back field plate structure can be manufactured through the commonly seen semiconductor device processing technology and comprises a source electrode, a drain electrode, a heterostructure and a back field plate electrode, wherein the source electrode and the drain electrode are electrically connected through two-dimensional electronic gas in the heterostructure, and the source electrode, the drain electrode and the heterostructure are of an ohmic contact mode; the heterostructure comprises a first semiconductor layer and a second semiconductor layer which are sequentially arranged in a set direction, the first semiconductor layer is arranged between the source electrode and the drain electrode, the surface of the first semiconductor layer is provided with a grid electrode, and a first insulating medium layer is arranged between the grid electrode and the first semiconductor layer to form an MIS structure; the back field plate electrode is arranged on the surface of the second semiconductor layer, which is away from the first semiconductor layer. The MIS-HEMT device with the back field plate structure can effectively increase the breakdown voltage of the device and restrain the current collapse effect to the largest extent.

Owner:SUZHOU NENGWU ELECTRONICS TECH

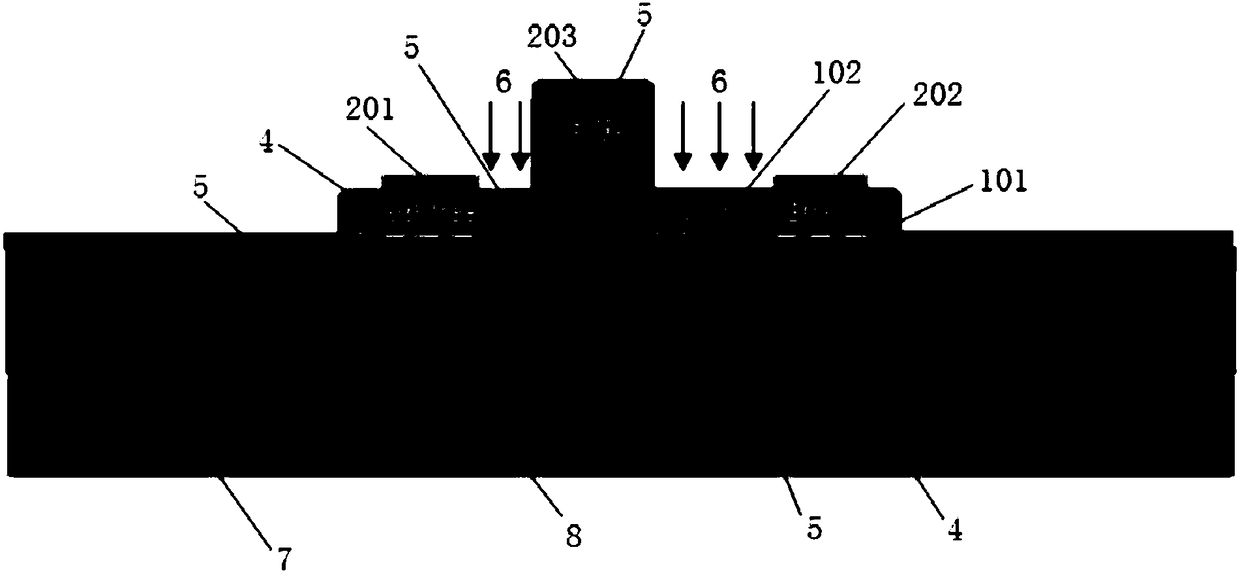

Gallium nitride transistor structure and preparation method thereof

ActiveCN110429127ASuppression of avalanche effectsAlleviate dummy gate effectSemiconductor devicesHeterojunctionGallium nitride

The invention discloses a gallium nitride transistor structure and a preparation method thereof. The gallium nitride transistor structure includes: a substrate 1; a GaN-based buffer layer 2 located onthe substrate 1; an InxAlyGa1-x-yN / GaN heterojunction epitaxial structure positioned on the GaN-based buffer layer 2; a source electrode 6 positioned at one end of the surface of the InxAlyGa1-x-yN / GaN heterojunction epitaxial structure; a drain electrode 5 positioned at the other end of the surface of the InxAlyGa1-x-yN / GaN heterojunction epitaxial structure; and a p-type oxide film and a gate 7which are located at the surface of the InxAlyGa1-x-yN / GaN heterojunction epitaxial structure. The p-type oxide film is arranged between the source electrode 6 and the drain electrode 5 at the surface of the InxAlyGa1-x-yN / GaN heterojunction epitaxial structure to obtain the GaN transistor structure of the p-type oxide intercalation to suppress the current collapse effect, and the virtual gate effect is relieved by neutralizing electrons in the hole in the p-type oxide and captured by surface traps.

Owner:安徽长飞先进半导体有限公司 +1

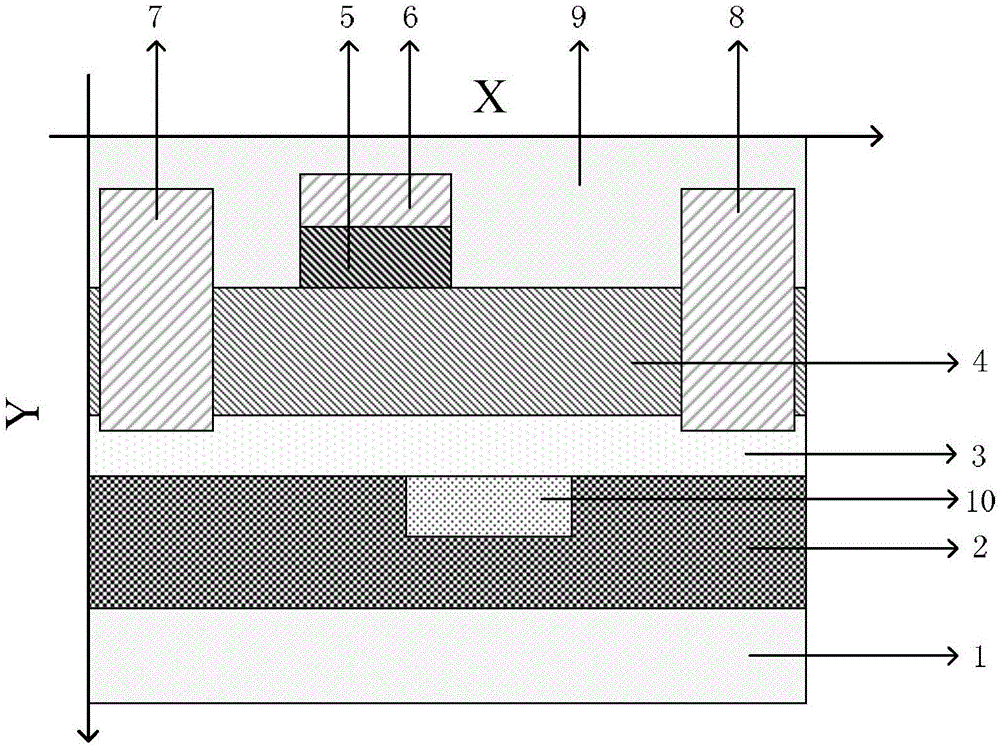

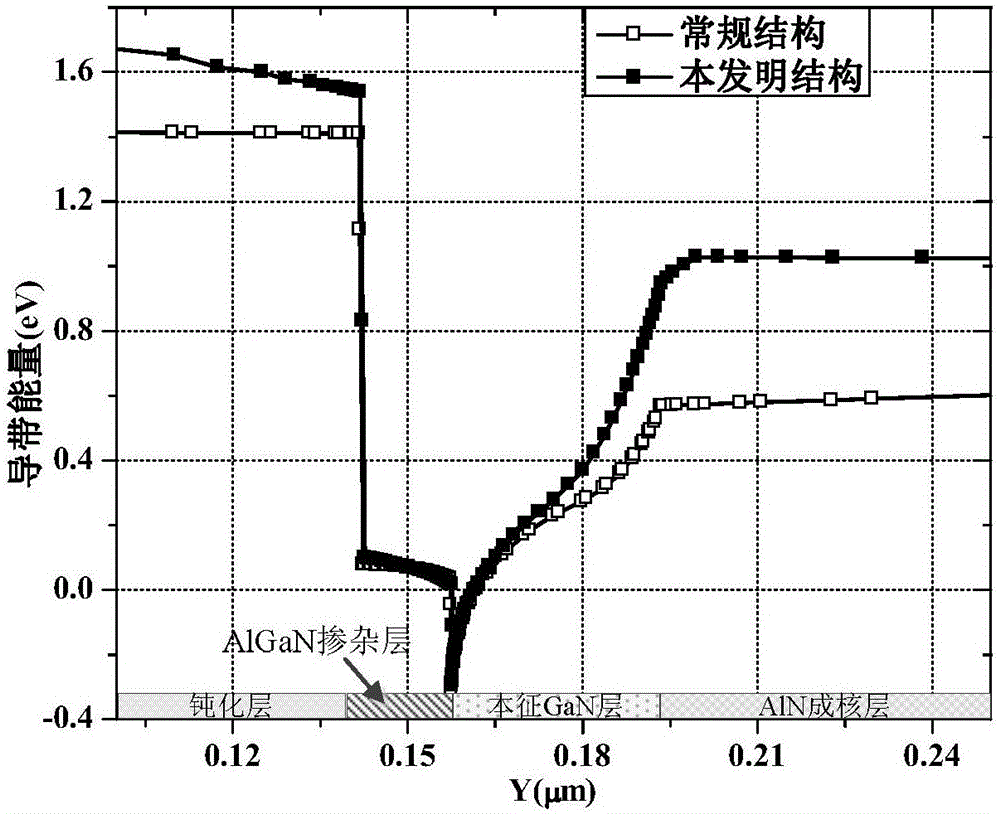

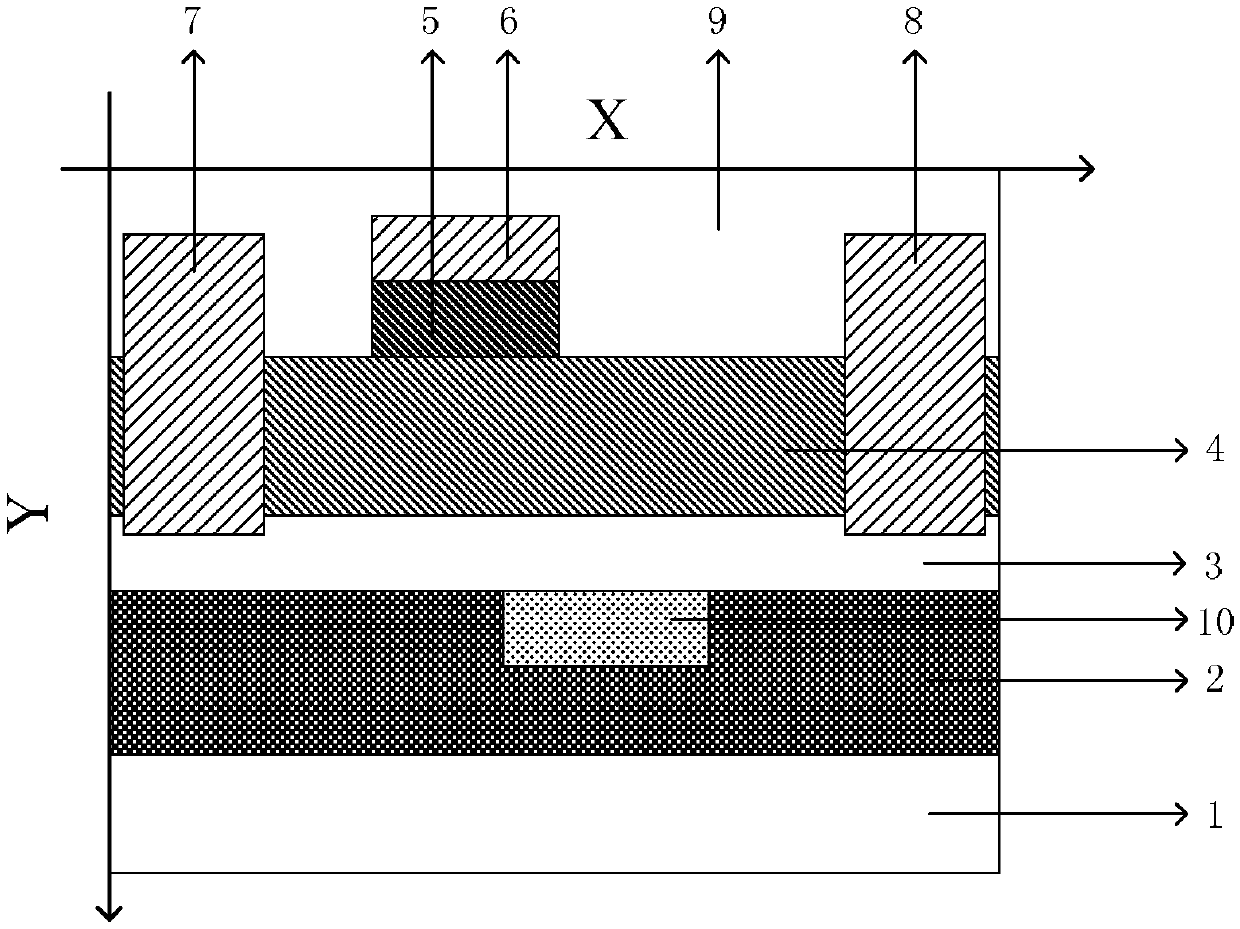

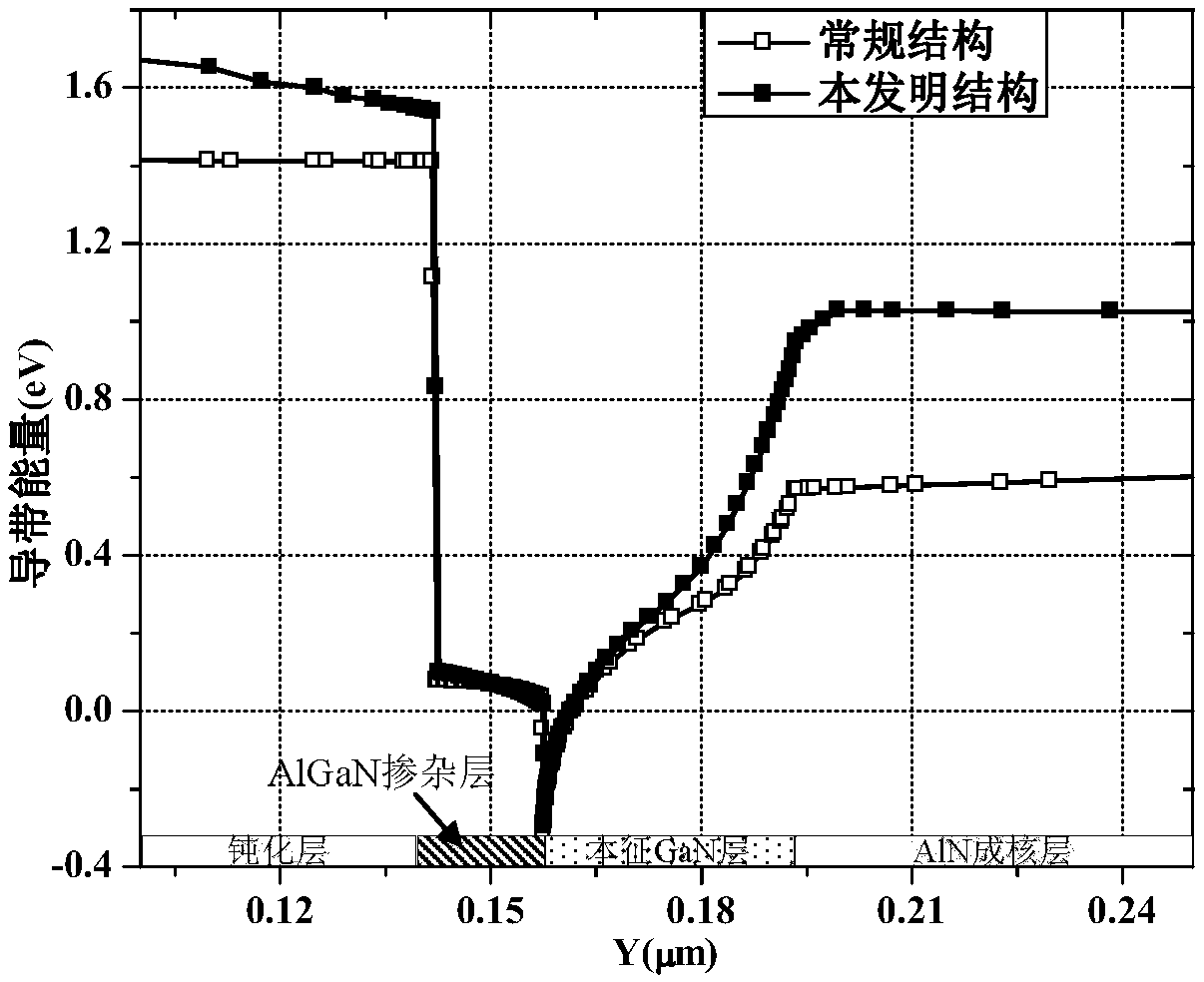

AlGaN-GaN high-electron mobility transistor with P-type buried layer

ActiveCN106206711ACurrent capacity unchangedPolarization does not affectSemiconductor devicesGate oxideElectron mobility

An AlGaN-GaN high-electron mobility transistor with a P-type buried layer comprises a Si-based substrate, wherein an AlN nucleating layer is formed on the Si-based substrate, an intrinsic GaN layer is formed on the AlN nucleating layer, an AlGaN doping layer is formed on the intrinsic GaN layer, a gate oxide layer is formed on an upper surface of the AlGaN doping layer, a gate is formed on an upper surface of the gate oxide layer, a passivation layer covers the AlGaN doping layer and the gate, a source is formed at one side of the gate, a drain is formed at the other side of the gate, the source and the drain extend form an upper part of the intrinsic GaN layer, penetrate through the AlGaN doping layer and are stopped in the passivation layer, the AlGaN-GaN high-electron mobility transistor is characterized in that a P-type AlGaN doping region buried layer is formed in the AlN nucleating layer, an upper surface of the P-type AlGaN doping region buried layer is in contact with a lower surface of the intrinsic GaN layer, a boundary of the P-type AlGaN doping region buried layer is arranged below the gate, and the other boundary of the P-type AlGaN doping region buried layer is arranged below a region between the gate and the drain.

Owner:SOUTHEAST UNIV

A gallium nitride transistor structure and its preparation method

ActiveCN110429127BSuppression of avalanche effectsAlleviate dummy gate effectSemiconductor devicesHeterojunctionElectron hole

Owner:安徽长飞先进半导体有限公司 +1

III nitride MISHEMT device

InactiveCN102403349BSuppression of avalanche effectsSemiconductor devicesElectrical conductorInsulation layer

The invention discloses an III nitride MISHEMT device, which comprises source and drain electrodes, main and secondary grids, first and second medium layers and a heterostructure; the source and drain electrodes are electrically connected through two-dimensional electron gas formed in the heterostructure; the heterostructure comprises first and second semiconductors; the first semiconductor is arranged between the source and drain electrodes; the second semiconductor is formed on the surface of the first semiconductor and is provided with a band gap wider than the first semiconductor; the first medium layer is arranged on the surface of the second semiconductor and forms a metal insulation layer semiconductor contact (MIS) along with the second semiconductor and the main grid; the second medium layer is arranged on the surfaces of the first medium layer and the main grid and forms electric isolation for the main grid and the secondary grid; the main grid is arranged at one side of the surface of the first medium layer close to the source electrode; and the secondary grid is formed on the surface of the second medium layer, and at least one side edge of the secondary grid is extended to the direction of the source electrode or the drain electrode, and meanwhile orthographic projection of the secondary grid is overlapped with the two side edges of the main grid. The ''current collapse effect'' can be substantially and effectively inhibited by the III nitride MISHEMT device.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

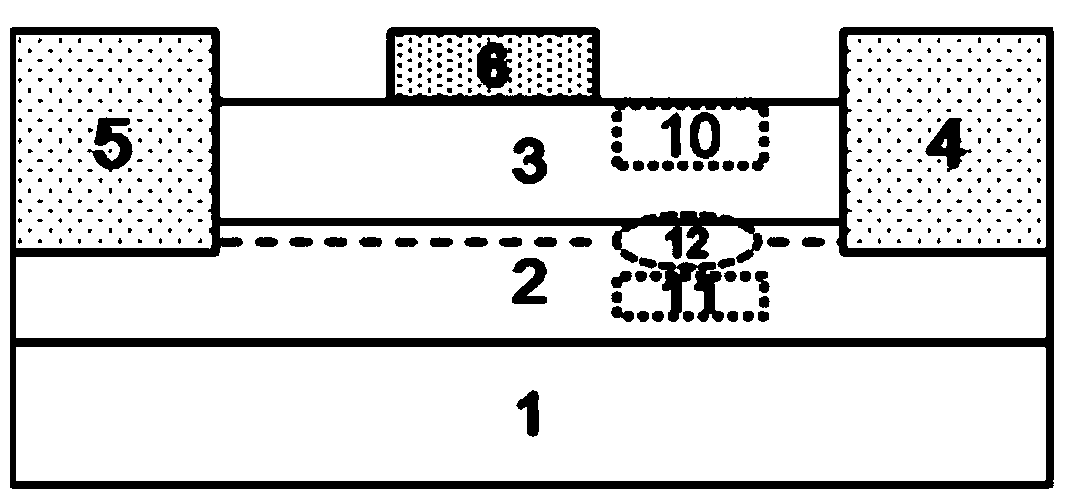

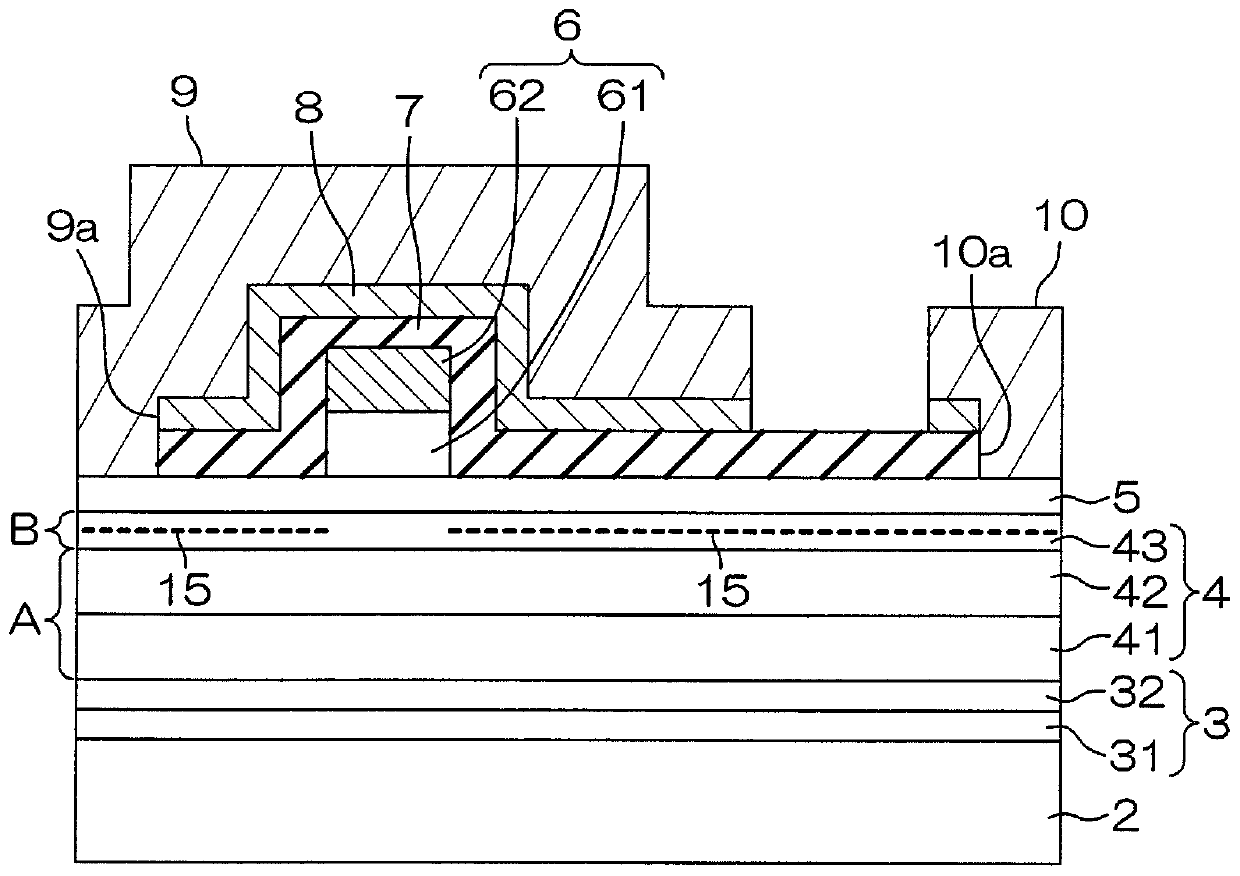

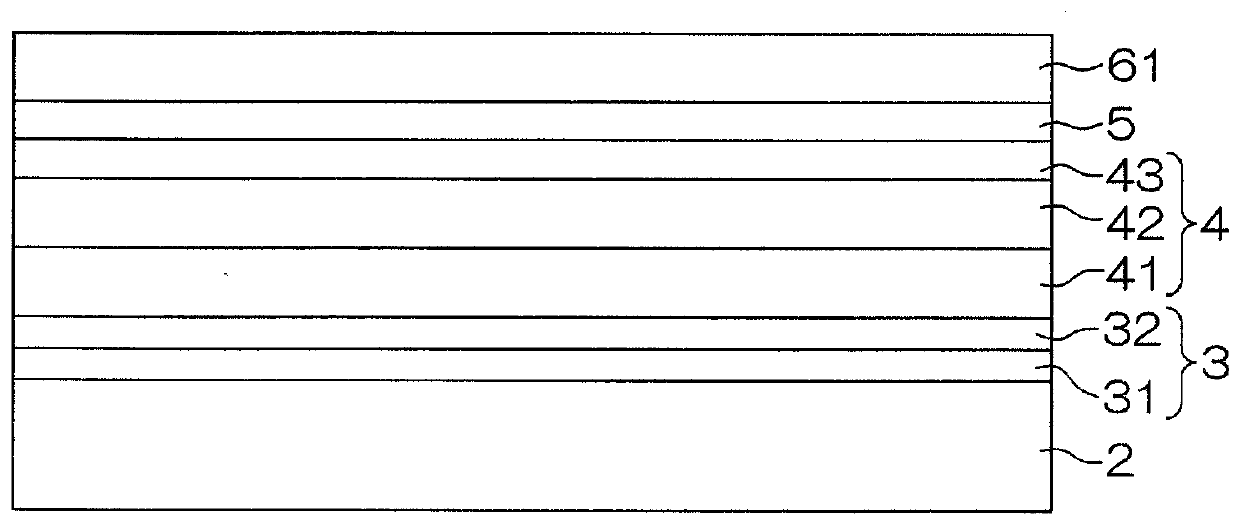

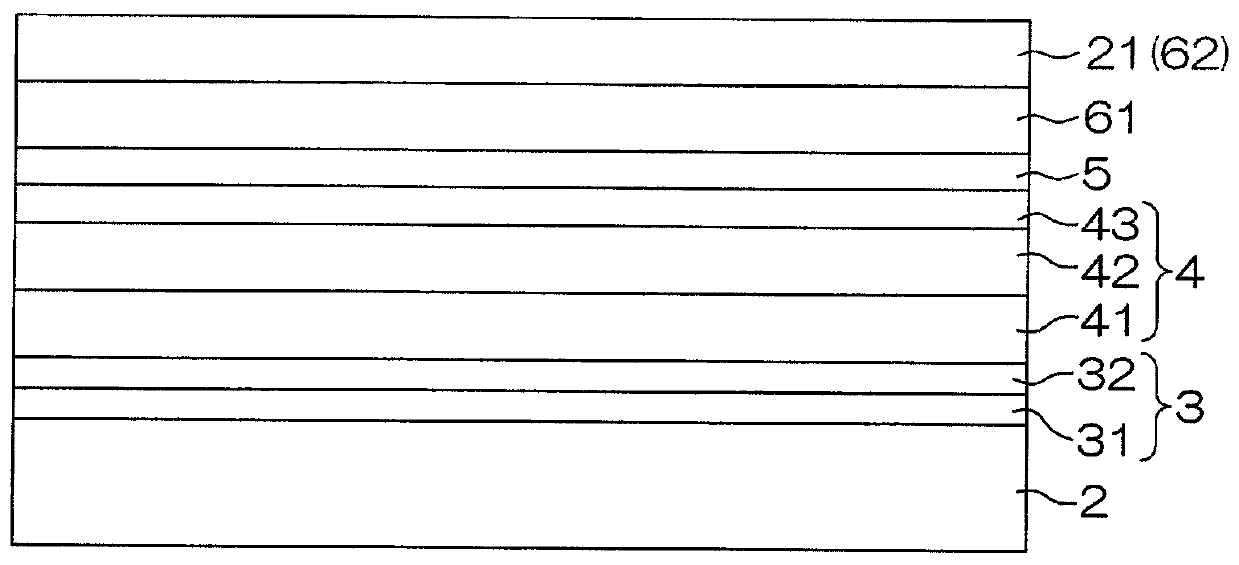

Semiconductor device

ActiveCN111373513ASuppression of avalanche effectsSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingAcceptorDevice material

A semiconductor device 1 includes a substrate 2, an electron transit layer 4 disposed on the substrate 2, and an electron supply layer 5 disposed on the electron transit layer 4. The electron transitlayer 4 includes: a conductive path forming layer 43 that is in contact with the electron supply layer 5; a first semiconductor region (first nitride semiconductor layer) 41 that contains an acceptor-type impurity; and a second semiconductor region (second nitride semiconductor layer) 42 that is disposed at a position closer to the conductive path forming layer 43 than is the first semiconductor region 41, the second semiconductor region 42 containing anacceptor-type impurity. The acceptor density of the first semiconductor region 41 is greater than the acceptor density of the second semiconductor region 42.

Owner:ROHM CO LTD

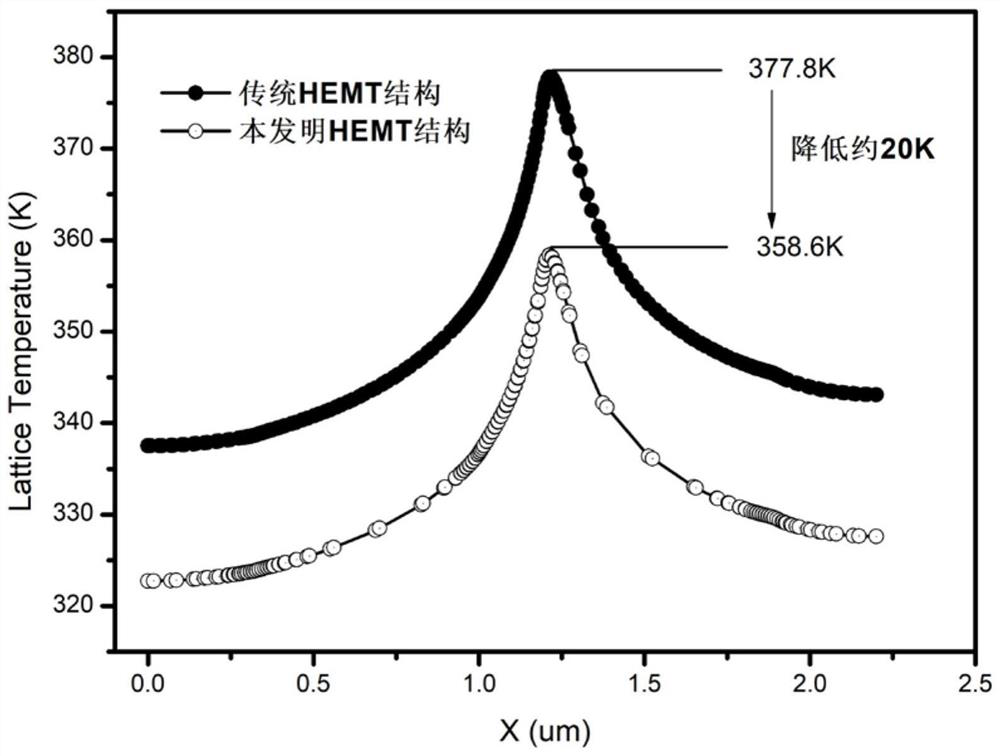

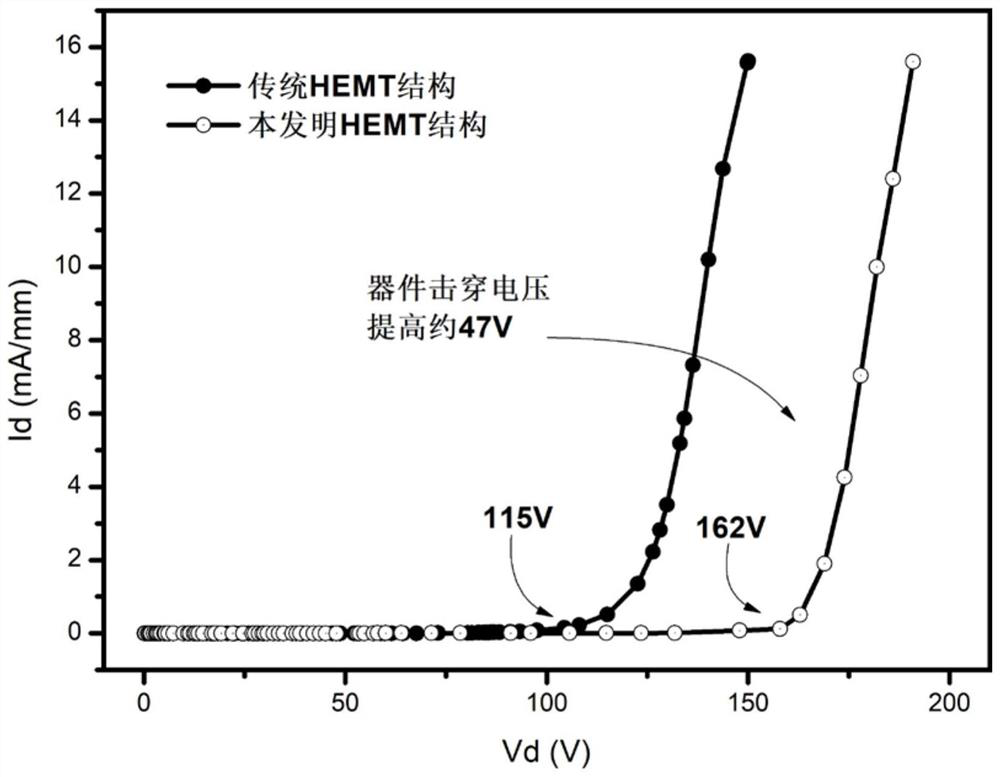

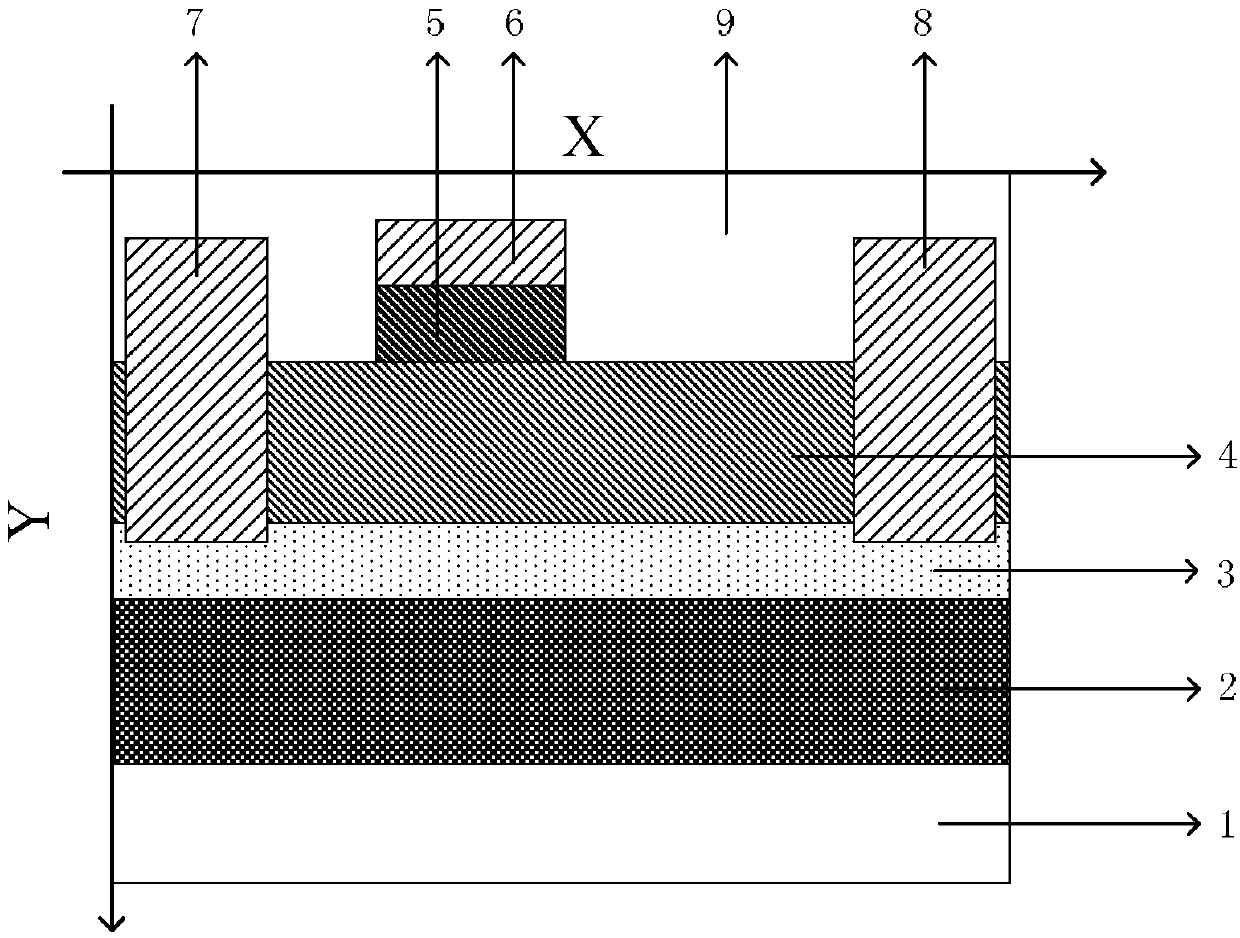

A gan heterojunction field effect transistor with low junction temperature and high withstand voltage

ActiveCN109671768BLower peak temperatureInhibit thermogenesisTransistorSemiconductor/solid-state device detailsHeterojunctionJunction temperature

The invention designs power semiconductor technology, specifically a GaN heterojunction field effect transistor with low junction temperature and high withstand voltage. The GaN heterojunction field effect transistor of the present invention mainly lowers the peak electric field of the channel by inserting an AlN region in the barrier layer, thereby achieving the purpose of increasing withstand voltage and reducing heat dissipation. In addition, the present invention uses AlN with good thermal conductivity as the passivation layer of the device, which not only helps to suppress current collapse, but also accelerates heat dissipation. The excellent effect of the invention is that the reverse withstand voltage of the device is improved, the output characteristics of the device are improved, and the channel temperature of the device is reduced, thereby suppressing the harm caused by the current collapse and the self-heating effect. The invention is especially suitable for GaN heterojunction field effect transistors with high withstand voltage capability and low channel temperature.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A p-type buried layer algan-gan high electron mobility transistor

ActiveCN106206711BSuppression of avalanche effectsCurrent capacity unchangedSemiconductor devicesGate oxideElectron mobility

An AlGaN-GaN high-electron mobility transistor with a P-type buried layer comprises a Si-based substrate, wherein an AlN nucleating layer is formed on the Si-based substrate, an intrinsic GaN layer is formed on the AlN nucleating layer, an AlGaN doping layer is formed on the intrinsic GaN layer, a gate oxide layer is formed on an upper surface of the AlGaN doping layer, a gate is formed on an upper surface of the gate oxide layer, a passivation layer covers the AlGaN doping layer and the gate, a source is formed at one side of the gate, a drain is formed at the other side of the gate, the source and the drain extend form an upper part of the intrinsic GaN layer, penetrate through the AlGaN doping layer and are stopped in the passivation layer, the AlGaN-GaN high-electron mobility transistor is characterized in that a P-type AlGaN doping region buried layer is formed in the AlN nucleating layer, an upper surface of the P-type AlGaN doping region buried layer is in contact with a lower surface of the intrinsic GaN layer, a boundary of the P-type AlGaN doping region buried layer is arranged below the gate, and the other boundary of the P-type AlGaN doping region buried layer is arranged below a region between the gate and the drain.

Owner:SOUTHEAST UNIV

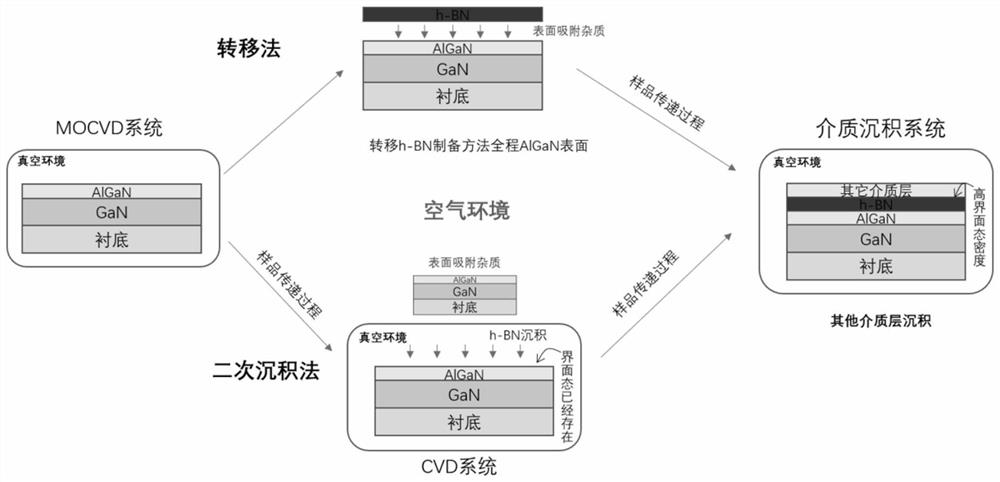

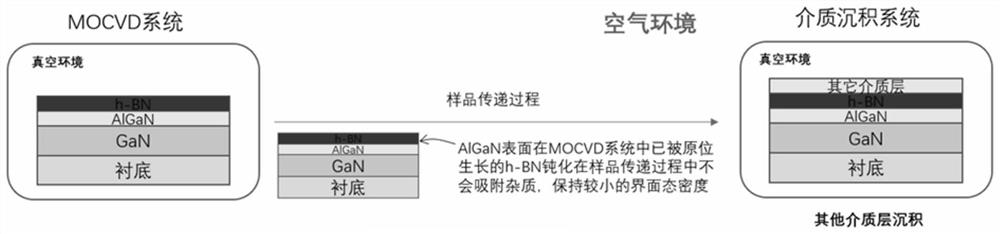

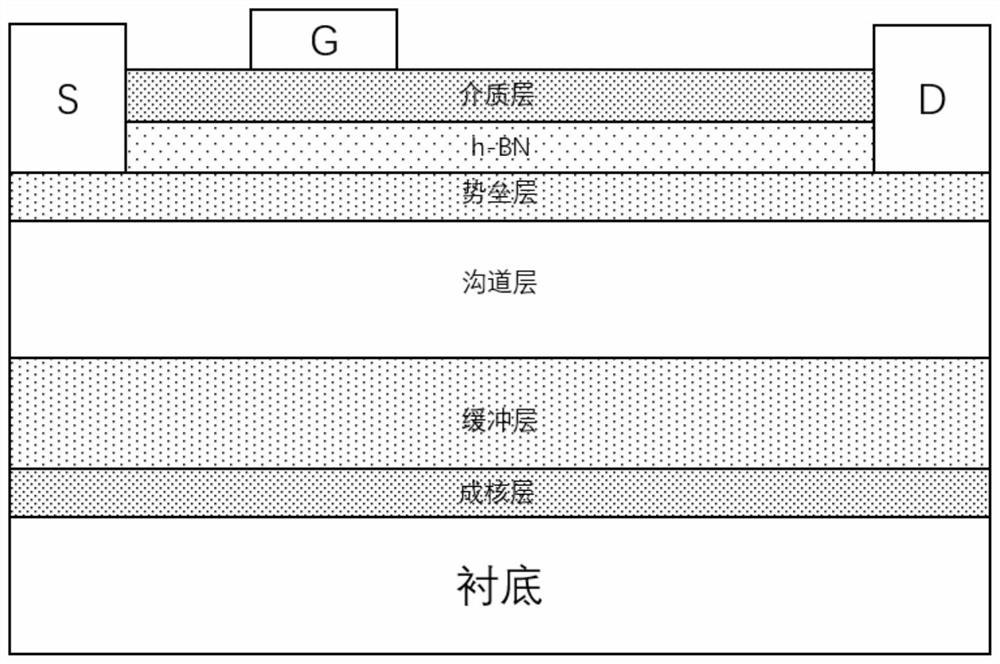

GaN MISHEMT device and manufacturing method thereof

PendingCN113594037AAvoid adsorptionImprove insulation performanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical connectionDangling bond

The invention discloses a GaN MISHEMT device and a manufacturing method thereof. The manufacturing method comprises the steps that an epitaxial structure is manufactured, the epitaxial structure comprises a channel layer and a barrier layer formed on the channel layer, and two-dimensional electron gas is formed between the AlGaN barrier layer and the channel layer; a two-dimensional material passivation layer epitaxially is grown on the barrier layer in situ; a dielectric layer is formed on the two-dimensional material passivation layer; a source electrode, a drain electrode and a grid electrode are manufactured, the source electrode and the drain electrode are arranged on the barrier layer and electrically connected through the two-dimensional electron gas, and the grid electrode is arranged on the dielectric layer and located between the source electrode and the drain electrode. According to the manufacturing method provided by the invention, after the GaN HEMT epitaxial structure is grown, the two-dimensional h-BN is grown in situ to serve as the surface passivation layer, and then the dielectric layer is deposited for the second time, so that surface damage can be blocked, surface dangling bonds can be shielded, the interface state density can be reduced, the current collapse effect can be effectively inhibited, and the device can obtain better direct current characteristics and dynamic characteristics.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

A high breakdown voltage GaN-based high electron mobility transistor

ActiveCN105261643BImprove thermal stabilityImprove reliabilitySemiconductor devicesNucleationGallium nitride

The invention relates to a high-breakdown-voltage GaN-based high-electron-mobility transistor, which mainly comprises a substrate, an AlN nucleation layer, a GaN buffer layer, a GaN channel layer, a AlGaN barrier layer, a source electrode, a drain electrode and a grid electrode, wherein the above layers are successively arranged from bottom to top and the source electrode, the drain electrode and the grid electrode are formed on the AlGaN barrier layer. The high-breakdown-voltage GaN-based high-electron-mobility transistor is characterized by further comprising an AlxGa1-xN polarization doped layer positioned on the AlGaN barrier layer and between the grid electrode and the drain electrode, with the content of Al component to be gradually changed. The content of Al component in the AlxGa1-xN polarization doped layer is linearly increased from top to bottom. The three-dimensional hole gas generated caused by he gradually changing content of Al component and the two-dimensional electron gas of the channel layer compensate each other to form a charge self-balancing type super-junction structure. In this way, the charge imbalance problem is solved. Meanwhile, the breakdown voltage and the stability of equipment are improved.

Owner:南京绿能芯耀科技有限公司

Hemt device with back field plate structure and preparation method thereof

ActiveCN103715257BEffective regulationSuppression of avalanche effectsSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorOhmic contact

The invention discloses an HEMT device with a back surface field plate structure and a manufacturing method of the HEMT device. The device can be manufactured through a common semiconductor device machining technology. The device comprises a source electrode, a drain electrode, a heterostructure and a back field plate electrode. The source electrode and the drain electrode electrically connected through two-dimensional electron gas formed in the heterostructure, the source electrode, the drain electrode and the heterostructure form ohmic contact, the heterostructure comprises a first semiconductor layer and a second semiconductor layer which are arranged in sequence in the setting direction, the first semiconductor layer is arranged between the source electrode and the drain electrode, a grid electrode is arranged on the surface of the first semiconductor layer, Schottky contact is formed between the grid electrode and the first semiconductor layer, and the back field plate electrode is arranged on the surface of one side, far away from the first semiconductor layer, of the second semiconductor. The puncture voltage of the device can be effectively improved, and the effect of electric current collapsing can be restrained to the maximum degree.

Owner:江苏盐综产业投资发展有限公司

GaN dual heterogeneity node field effect transistor structure and its making method

InactiveCN101266999BRaise the barrier heightImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerNucleation

A gallium nitride-based double heterojunction field effect transistor structure comprises a substrate, a low temperature gallium nitride layer or high temperature aluminum nitride layer formed on thesubstrate; a high insulation layer with unintentional-doped or doped gallium nitride; the high insulation layer with unintentional-doped or doped gallium nitride is formed on a low temperature galliumnucleation layer or a high temperature gallium nitride nucleation layer; a first aluminum nitride inserting layer, the first aluminum nitride inserting layer is formed on the high insulation layer with unintentional-doped or doped gallium nitride; a unintentional-doped gallium nitride channel layer, the unintentional-doped gallium nitride channel layer is formed on the first aluminum nitride inserting layer; a second aluminum nitride inserting layer, the second aluminum nitride inserting layer is formed on the unintentional-doped gallium nitride channel layer, an unintentional-doped or n-typedoped AlxInyGazN layer, the unintentional-doped or n-type doped AlxInyGazN layer is formed on the second aluminum nitride inserting layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com