Method, device and system for testing power consumption of subsystems in SOC system

A subsystem and power consumption technology, which is applied to measurement devices, electrical devices, and electrical power measurement. It can solve the problems of power consumption, difficulty, and excessive power consumption. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

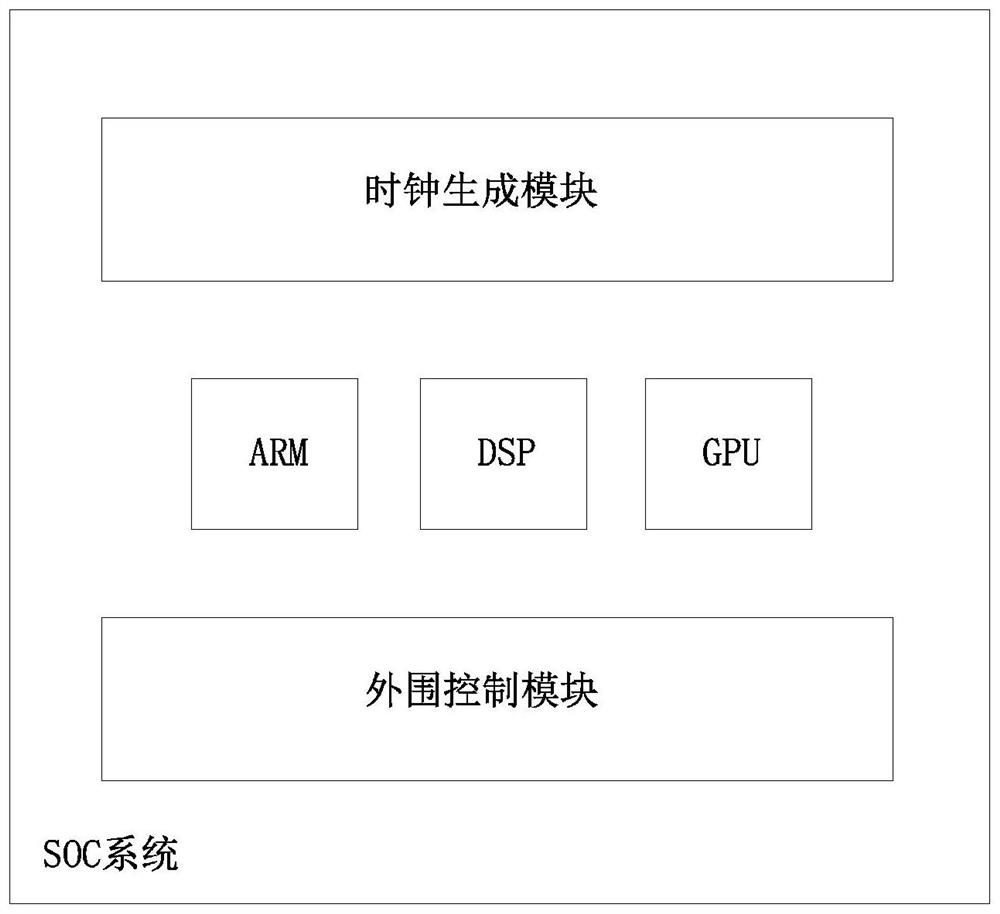

[0053] This embodiment provides a method for testing power consumption of subsystems in an SOC system.

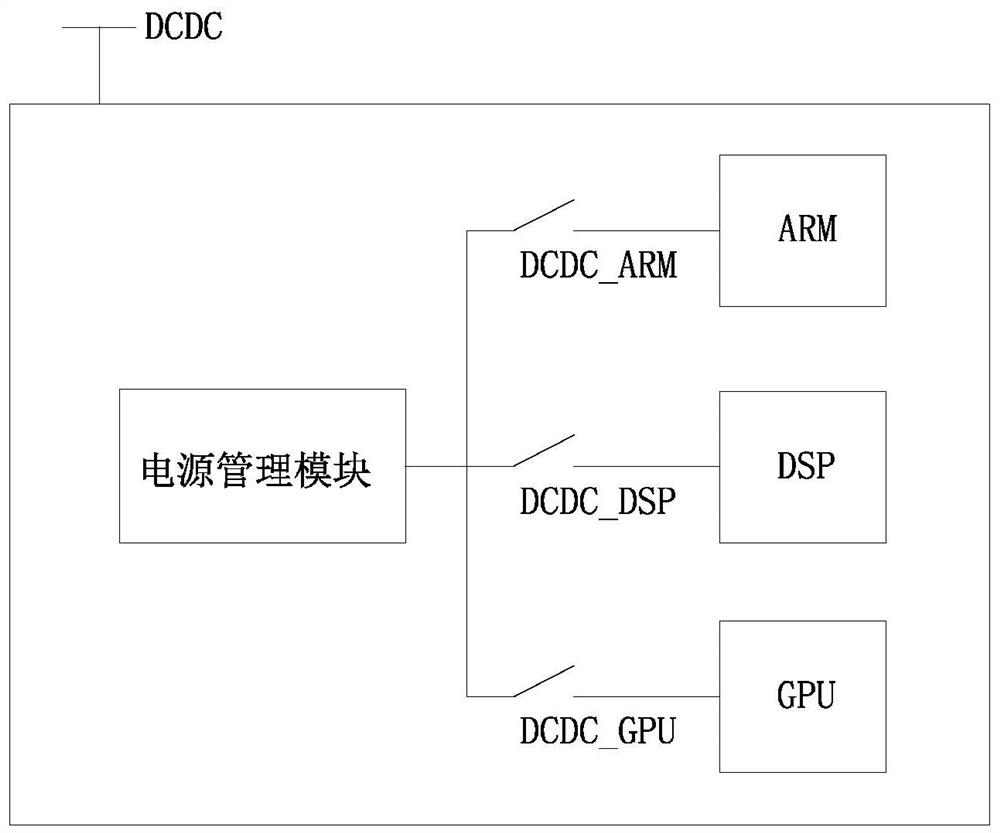

[0054] The SOC system includes multiple subsystems, and an independent DCDC power supply is set for each subsystem of the SOC system, and the DCDC power supply is correspondingly provided with a DCDC power switch. Each DCDC power switch is controlled to be turned on or off by a PMU (power management unit).

[0055] see figure 2 As shown, in this embodiment, the SOC system may include an ARM subsystem, a DSP subsystem, and a GPU subsystem. The aforementioned subsystems are sequentially provided with DCDC power supplies DCDC_ARM, DCDC_DSP, and DCDC_GPU. The DCDC_ARM controls the ARM subsystem. System power supply, DCDC_DSP control supplies power to the DSP subsystem, and DCDC_GPU controls supplies power to the GPU subsystem.

[0056] Compared with LDO (low dropout voltage regulator), the DCDC power supply has higher conversion efficiency and can handle large current.

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More