Preparation method of silicon through hole interconnection structure

An interconnection structure and through-silicon via technology, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, and electrical solid-state devices, can solve problems such as high cost, poor reliability of through-silicon via interconnection structures, and cumbersome preparation processes, and achieve good results. Reliability, reduction of preparation time and cost, effect of reduction of preparation steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0058] This embodiment provides a method for preparing a through-silicon via interconnection structure, including the following steps,

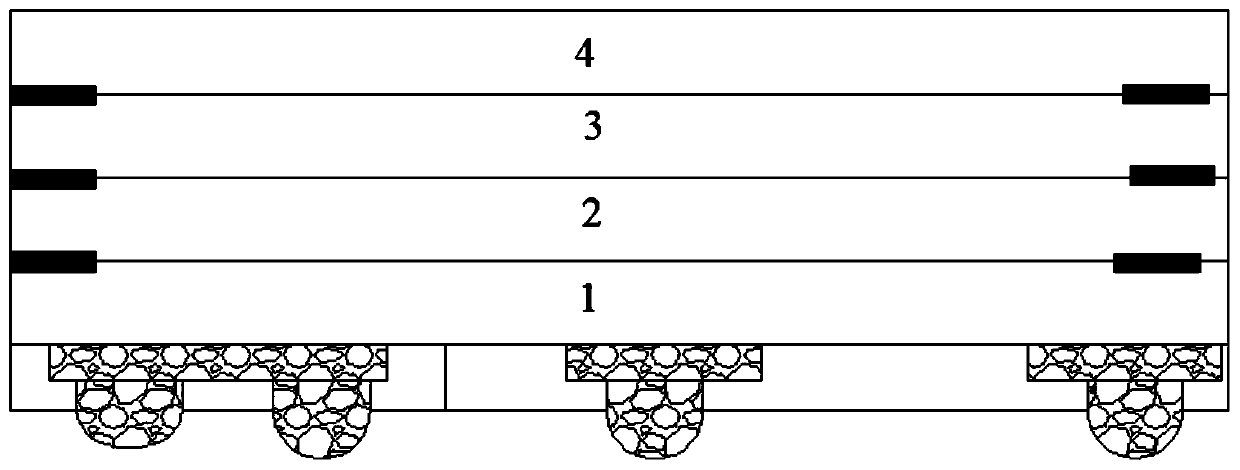

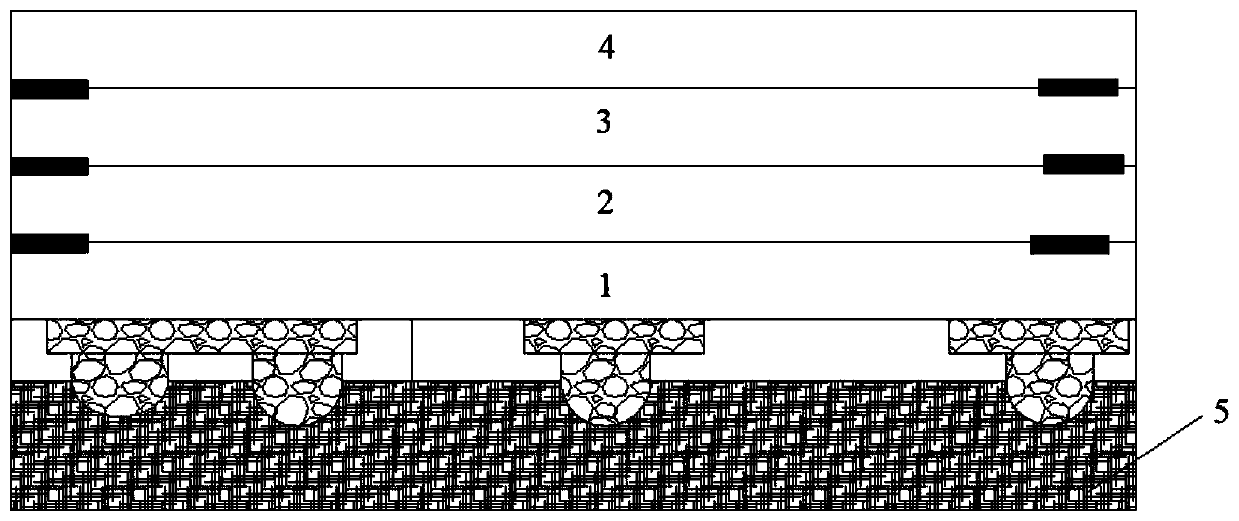

[0059] Using the mounting process, the first device, the second device, the third device and the fourth device are respectively bonded, such as figure 1 shown, and then use a temporary bonding glue to bond a carrier sheet on the bottom, such as figure 2 shown;

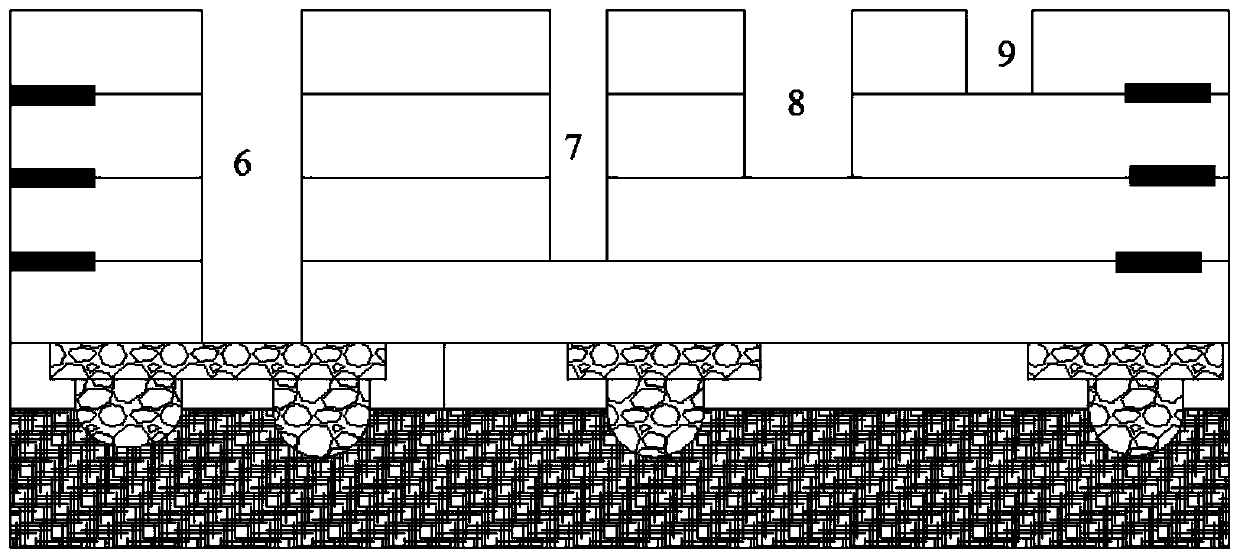

[0060] Use dry etching technology to etch to obtain 4 silicon holes (i.e. the first silicon hole 6, the second silicon hole 7, the third silicon hole 8 and the fourth silicon hole 9, the depths of which are respectively the stacked thickness of the four devices , the stacked thickness of three devices, the stacked thickness of two devices, and the stacked thickness of one device. When etching silicon holes, the etching sequence is from shallow to deep. When etching deeper holes, use dry film to The etched shallow holes are covered and protected, and then the deep holes are etched. ...

Embodiment 2

[0065] This embodiment provides a method for preparing a through-silicon via interconnection structure, including the following steps,

[0066] Bond the first device, the second device, the third device and the fourth device respectively by using the SMT process, and then use a temporary bonding glue to bond a carrier sheet on the bottom;

[0067] Use dry etching technology to etch to obtain 4 silicon holes (i.e. the first silicon hole, the second silicon hole, the third silicon hole and the fourth silicon hole, the depths of which are respectively the stacked thickness of four devices, three devices When etching silicon holes, the etching sequence is from shallow to deep. When etching deeper holes, use dry film to cover the etched holes. The shallow holes are covered and protected, and then the deep holes are etched. After the etching is completed, the holes are opened to obtain 4 silicon holes with different depths). (PCVD) deposits a silicon dioxide insulating layer, so th...

Embodiment 3

[0072] This embodiment provides a method for preparing a through-silicon via interconnection structure, including the following steps,

[0073] Using the mounting process, the first device, the second device, the third device and the fourth device are respectively bonded, such as figure 1 described, then use a temporary bonding glue to bond a carrier sheet on the bottom, such as figure 2 shown;

[0074] Use dry etching technology to etch to obtain 4 silicon holes (that is, the first silicon hole, the second silicon hole, the third silicon hole and the fourth silicon hole, the depths of which are the stacked thickness of the four devices), and then use Low-temperature chemical vapor deposition technology (PCVD) deposits an insulating layer of silicon dioxide, so that the side walls and bottom of the silicon hole contain an insulating layer, and then removes the insulating layer at the bottom of the silicon hole by using a combination of surface coating photoresist and dry etc...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Aperture | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More