Multi-layer integrated circuit layout polygon alignment and simplification processing method and device

A technology of integrated circuits and processing methods, which is applied in image data processing, 3D modeling, instruments, etc., and can solve the problem of polygon overlapping on both sides of the gap, circuit short circuit of integrated circuit layout, multi-layer integrated circuit analysis and solution time and memory. increase, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

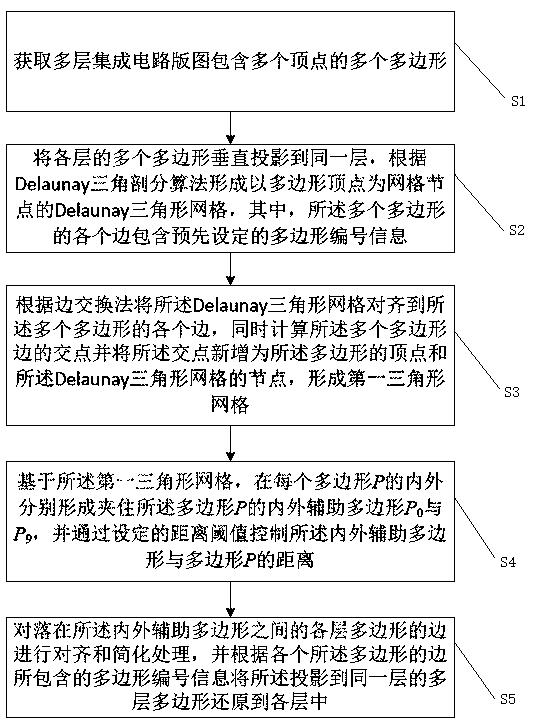

Method used

Image

Examples

Embodiment approach

[0139] As a possible implementation manner, the fourth processing module mainly includes:

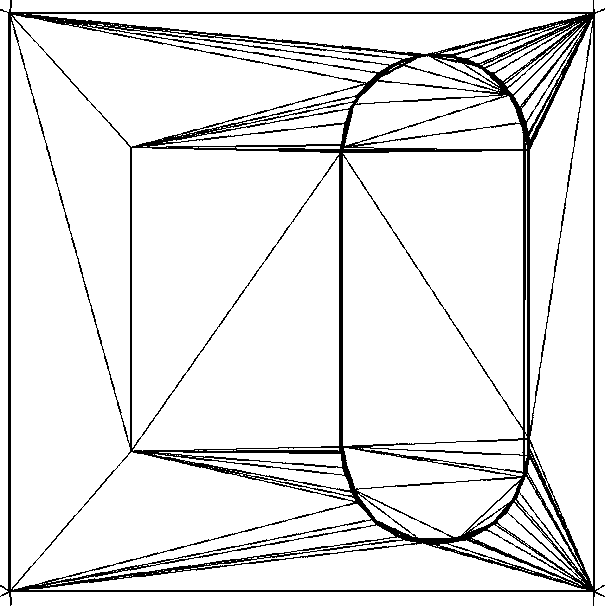

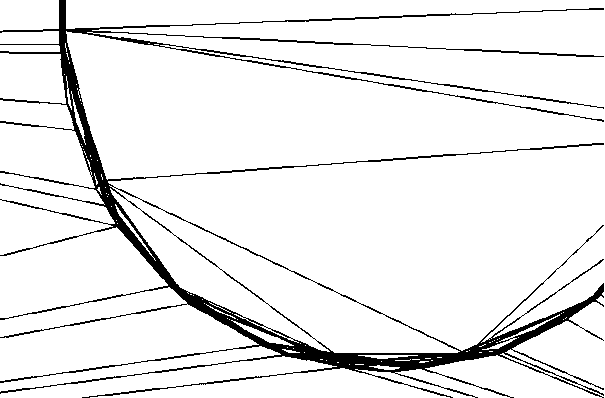

[0140] A first processing subunit, configured to align the first triangular mesh to each side of the inner and outer auxiliary polygons according to the edge exchange method to form a second triangular mesh;

[0141] The second processing subunit is used to identify the vertices of all polygons in the area clamped by the inner and outer auxiliary polygons, and define the identified vertices as being compatible with the polygon P The polygon vertices whose distance is less than a predetermined threshold;

[0142] The third processing subunit is used for each polygon, according to the identified vertices, to find the continuous identified vertices located in the polygon where the identified vertices are located, and the continuous identified vertices form a partial polygon segment or a complete polygon, is treated as the polygon P Coincident, merge the coincident partial polygon segment...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More