Power MOS device and manufacturing method thereof

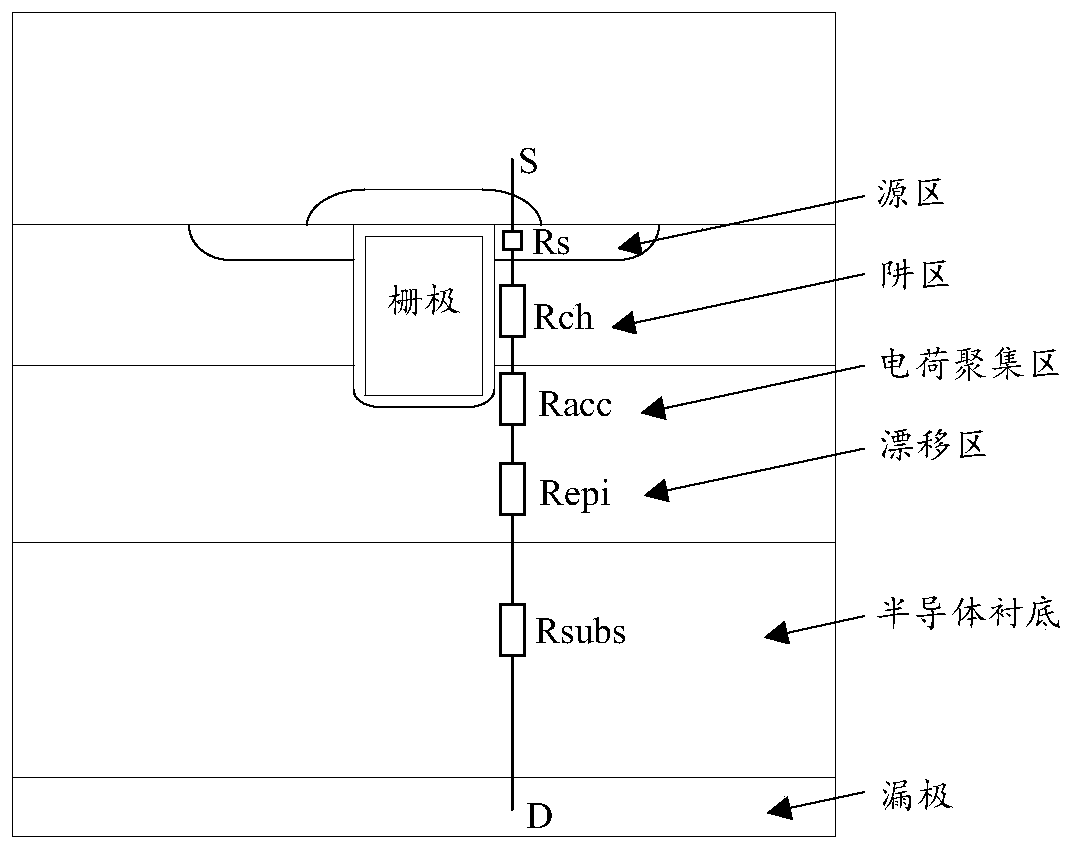

A technology of MOS devices and manufacturing methods, which is applied to semiconductor devices, electrical components, circuits, etc., can solve problems such as hindering device performance, affecting device reliability, and large on-resistance of power MOS devices, so as to improve device reliability and reduce On-resistance, the effect of improving the overall performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

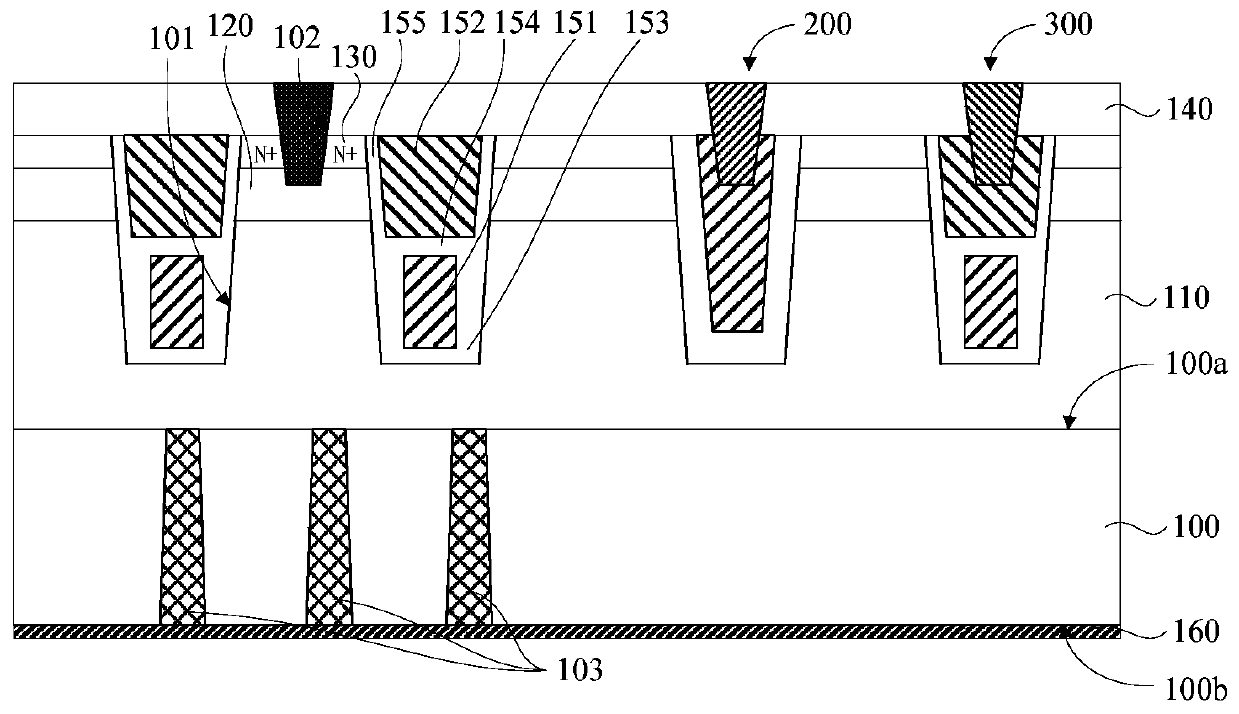

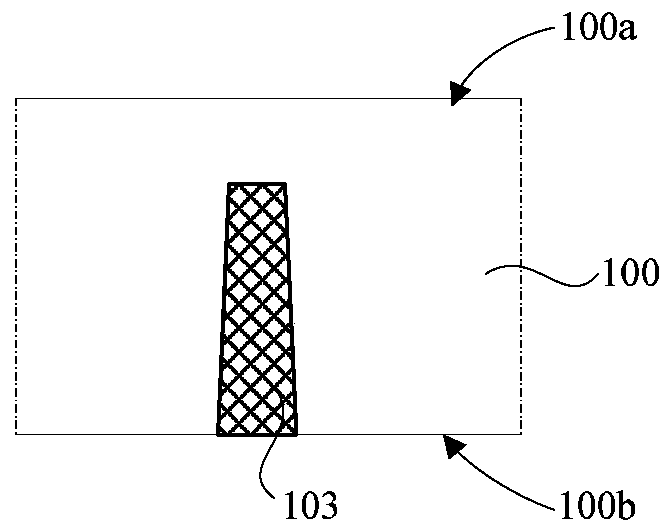

[0029] The power MOS device and its manufacturing method of the present invention will be further described in detail below with reference to the drawings and specific embodiments. The advantages and features of the present invention will become clearer from the following description. It should be noted that in the following description, many specific details and numerical values are given in order to provide a more thorough understanding of the present invention. However, it is obvious to those skilled in the art that the present invention may not require one or more In other instances, some technical features known in the art are not described in order to avoid obscuring the present invention. It should be understood that the drawings in the description are all in very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0030] The power MOS devices in the embod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More