Compiler implementation method and system supporting heterogeneous computing core architecture

An implementation method and technology of a compiler, applied in computing, code compilation, instrumentation, etc., can solve problems such as inefficiency, and achieve the effect of improving execution efficiency, instruction execution performance, and computing efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] In order to better understand the technical content of the present invention, specific embodiments are given together with the attached drawings for description as follows.

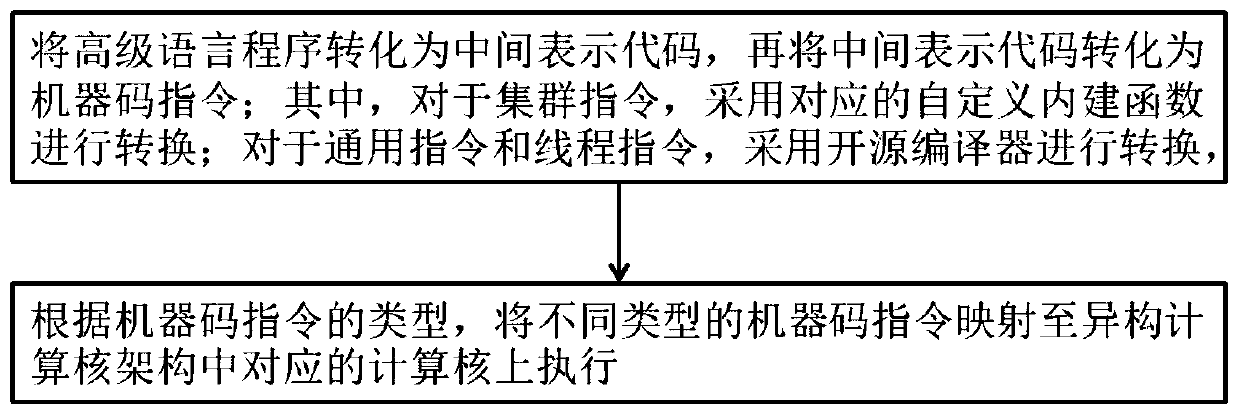

[0051] combine figure 2 , the present invention proposes a compiler implementation method supporting heterogeneous computing core architecture, the method comprising:

[0052] S1: Convert the high-level language program into intermediate representation code.

[0053] S2: Convert the intermediate representation code into machine code instructions.

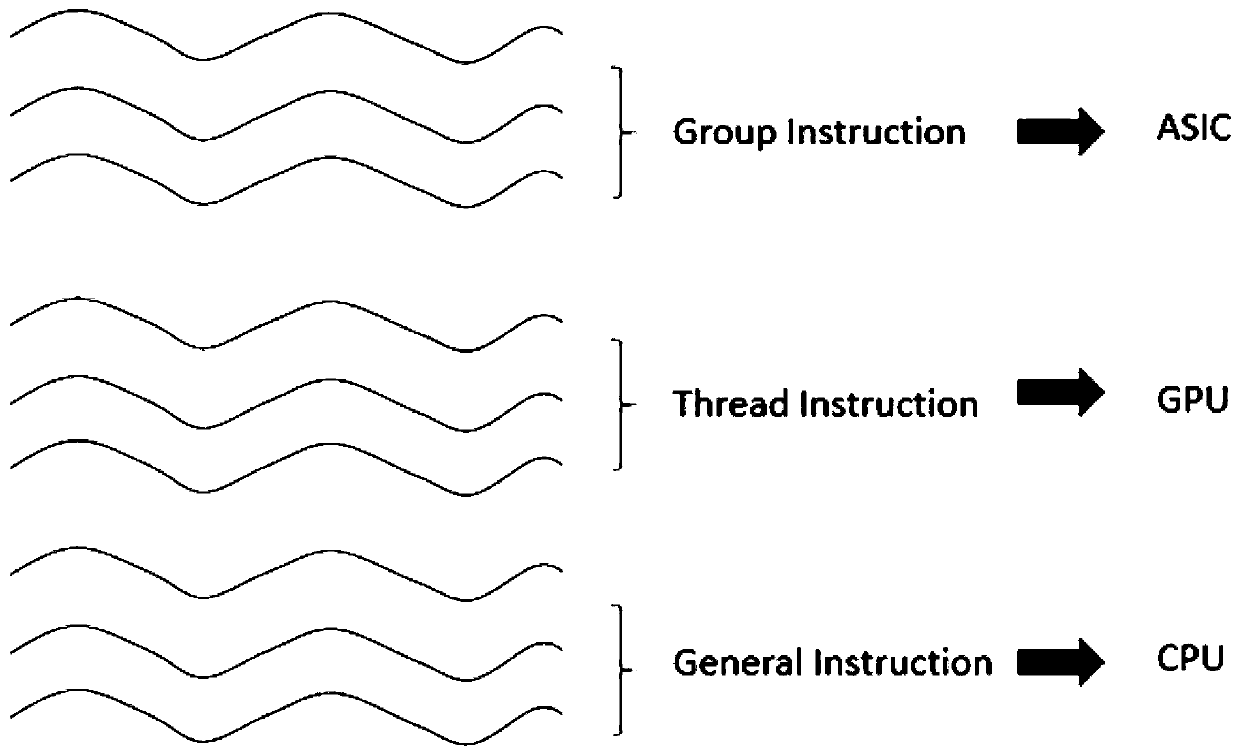

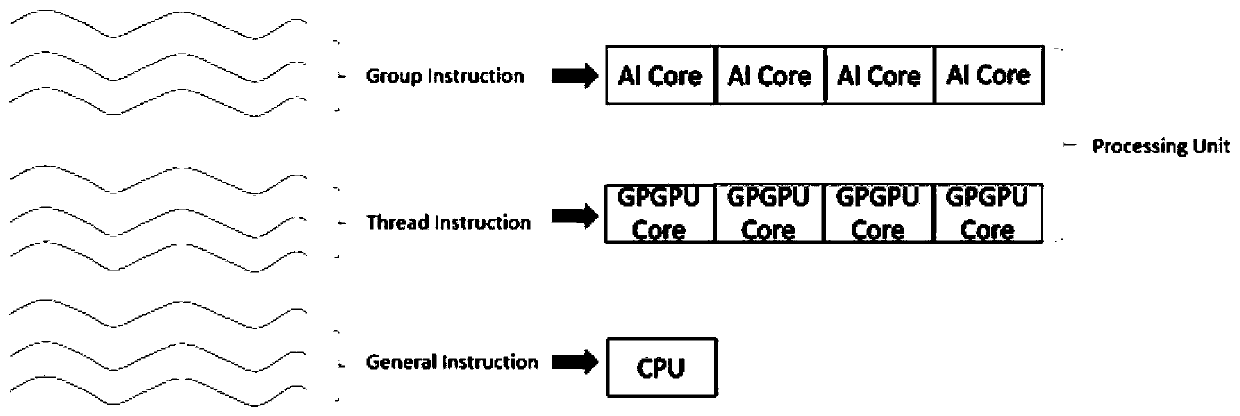

[0054] S3: According to the type of machine code instructions, map different types of machine code instructions to corresponding computing cores in the heterogeneous computing core architecture for execution. The machine code instructions include general instructions, cluster instructions and thread instructions.

[0055] in:

[0056] For cluster instructions, use the corresponding custom built-in functions for conversion; for general instructions and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More