FFT accelerator based on DSP chip

An accelerator and chip technology, applied in the field of FFT calculations, can solve the problems of limiting the application range of FFT accelerators, floating-point format does not provide support, etc., and achieve the effects of wide application range, improved execution performance, and strong flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described below in conjunction with the accompanying drawings and specific preferred embodiments, but the protection scope of the present invention is not limited thereby.

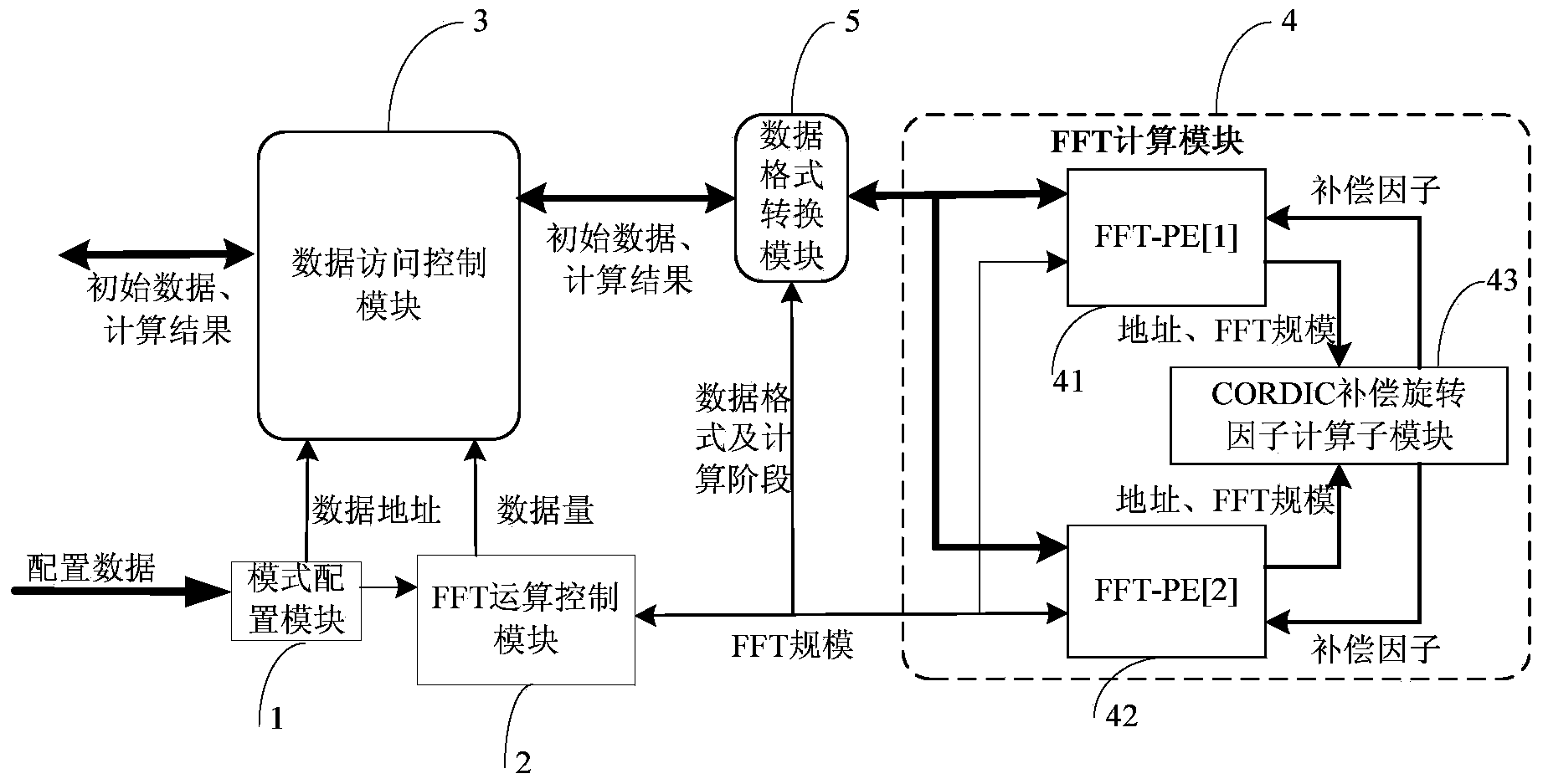

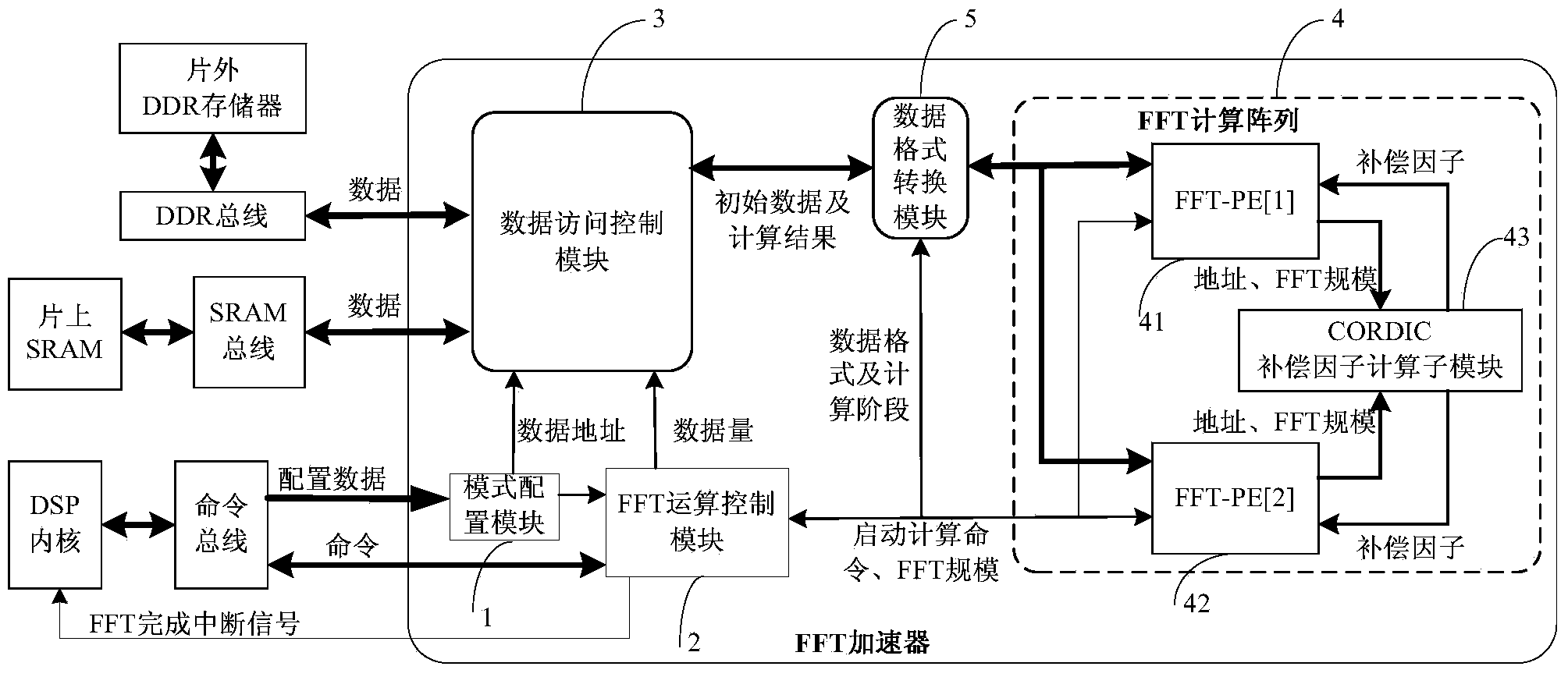

[0037] Such as figure 1As shown, the present embodiment is based on the FFT accelerator structure of the DSP chip, including:

[0038] Mode configuration module 1, used to receive data address from DSP core, operation scale N=2 k and the configuration data of the operation times M are output to the FFT operation control module 2 and the data access control module 3;

[0039] FFT operation control module 2, used to judge whether the operation scale N is greater than the threshold N 1 , if not, control the FFT calculation module 4 to carry out N-point one-dimensional FFT calculation; if yes, convert the initial calculation data into N 1 *N 2 The two-dimensional matrix of and control FFT calculation module 4 to carry out two-dimensional FFT operation, wherein N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More