Storage unit and multi-port SRAM

A storage unit and storage module technology, applied in the semiconductor field, can solve problems such as increased power consumption of writing operations, and achieve the effects of increasing reliability, avoiding writing failures, and reducing writing difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

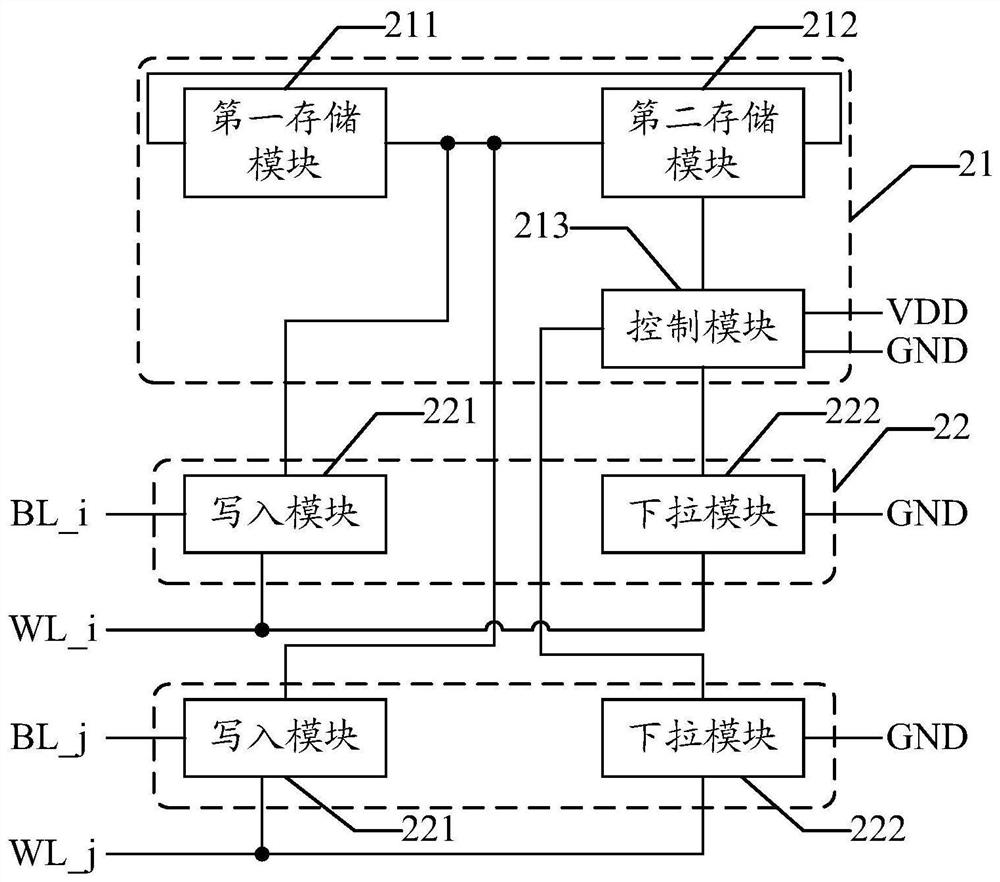

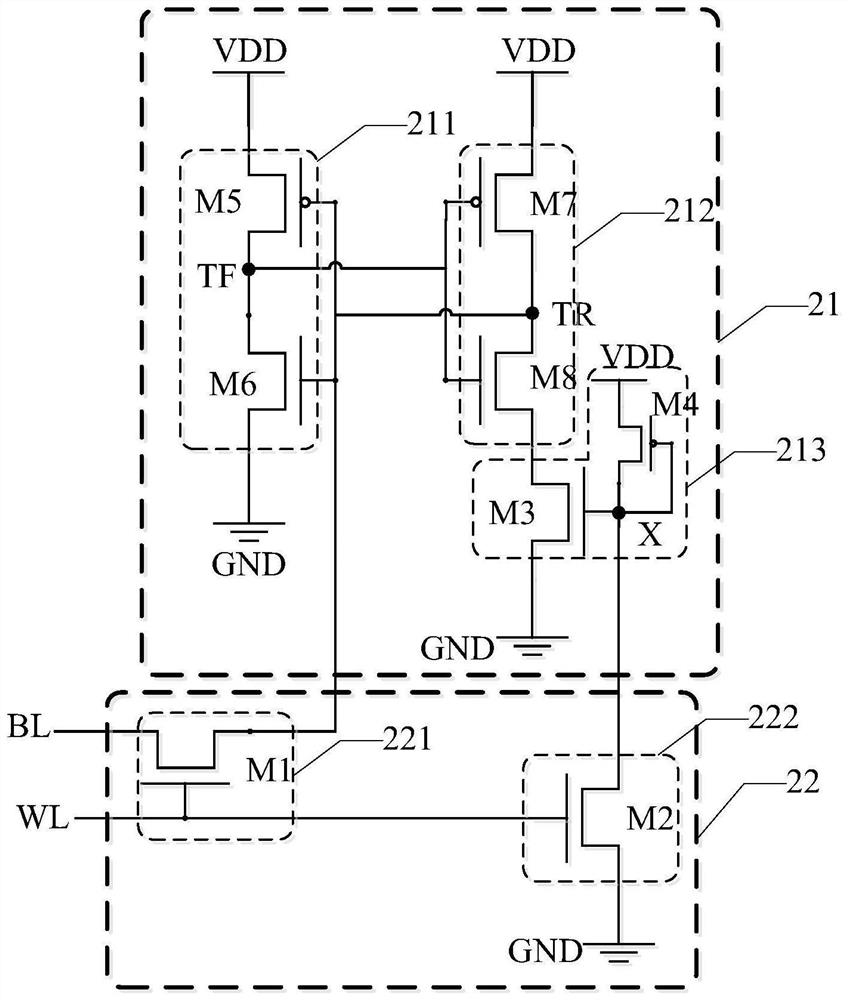

[0032] refer to figure 2 , showing a schematic structural diagram of a storage unit according to an embodiment of the present invention.

[0033] An embodiment of the present invention provides a storage unit, including: a storage circuit 21 and a plurality of writing circuits 22 .

[0034] The storage circuit 21 includes a first storage module 211, a second storage module 212 and a control module 213; the input end of the first storage module 211 is connected to the output end of the second storage module 212, and the output end of the first storage module 211 is connected to the output end of the second storage module 212. The input terminal of the second storage module 212 is connected; the control module 213 is connected to the power supply voltage terminal VDD, the ground terminal GND and the second storage module 212 respectively, and is used to control the path between the output terminal of the second storage module 212 and the ground terminal GND turn-on and turn-of...

Embodiment 2

[0077] An embodiment of the present invention further provides a multi-port static random access memory, including the above storage unit.

[0078] The multi-port SRAM includes a memory cell array, and the memory cell array includes a plurality of memory cells arranged in an array. When the multi-port SRAM includes n write ports, each memory cell includes a memory circuit 21 and n write circuits 22, the pin of each write port is connected to the word line WL and the bit line BL corresponding to each memory cell, for example, the pin of write port i is connected to the word line corresponding to each memory cell The line WL_i is connected to the bit line BL_i, and the pin of the write port j is connected to the word line WL_j and the bit line BL_j corresponding to each memory cell.

[0079] For the specific description of the storage unit, reference may be made to the description of Embodiment 1, which is not repeated in this embodiment of the present invention.

[0080] In ad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More