Custom lead frame from standard plus printed lead frame portion

A technology of metal leads and metal traces, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problems of time-consuming, high LF design cost, etc., and achieve the effect of reducing quantity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] Example embodiments are described with reference to the drawings, wherein like reference numerals are used to indicate similar or equivalent elements. The illustrated ordering of acts or events should not be considered limiting, as some acts or events may occur in different orders and / or concurrently with other acts or events. Furthermore, some of the illustrated acts or events may not be required to implement a methodology in accordance with the present disclosure.

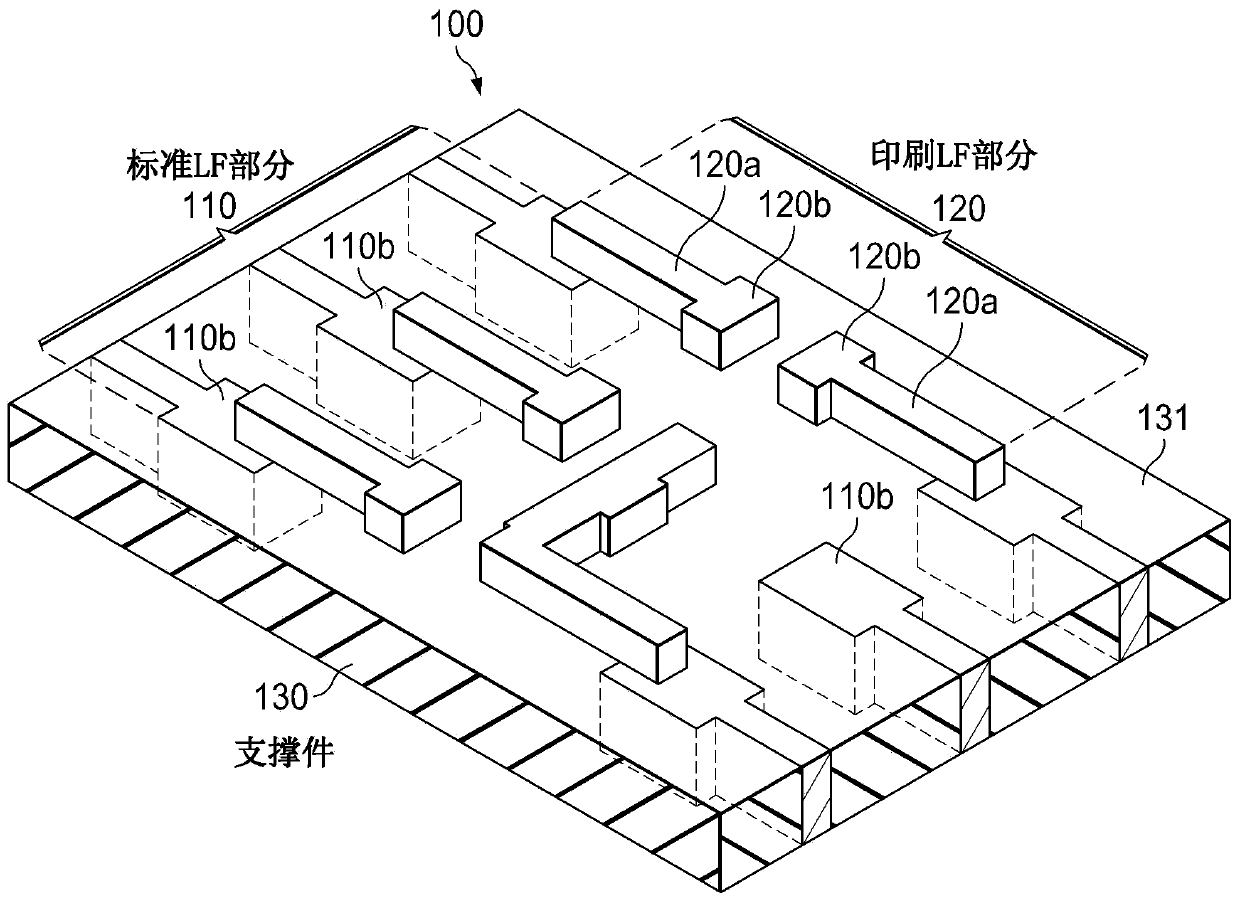

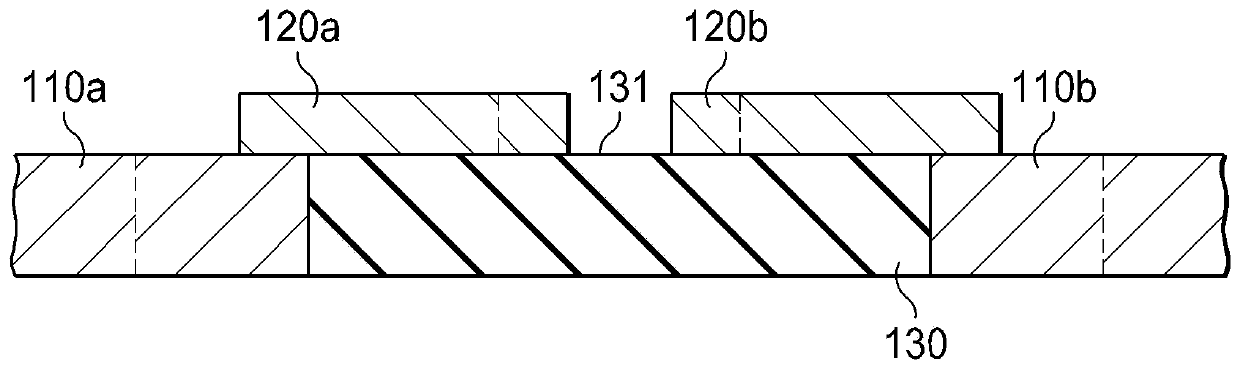

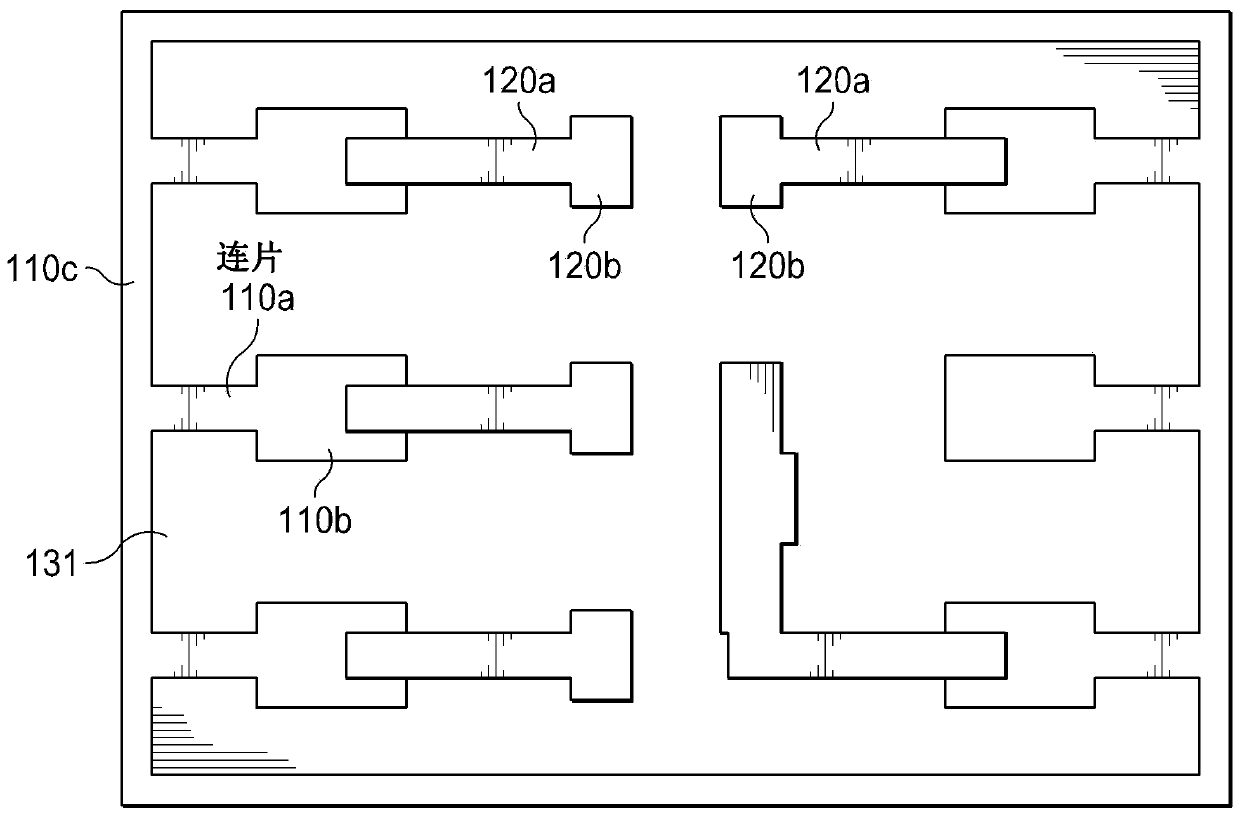

[0013] figure 1 A simplified example custom LF 100 is shown showing its standard LF portion 110 with leads 110b on at least two sides, and a printed LF portion 120 coupled to the leads 110b of the standard LF portion 110 according to an example embodiment. There is usually some designed overlap between traces 120a of printed LF portion 120 and leads 110b to reflect manufacturing tolerances to ensure connections are reliably provided. Custom LF 100 is typically part of a custom LF strip comprising multipl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More