Wafer-level packaging structure and wafer-level packaging method

A technology of wafer-level packaging and packaging methods, which is applied in the direction of electrical components, electric solid-state devices, circuits, etc., can solve the problems of high technical difficulty, high cost of wafer-level packaging, and low space utilization, and achieve low technical difficulty, Avoid packaging technology, the effect of efficient use of space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

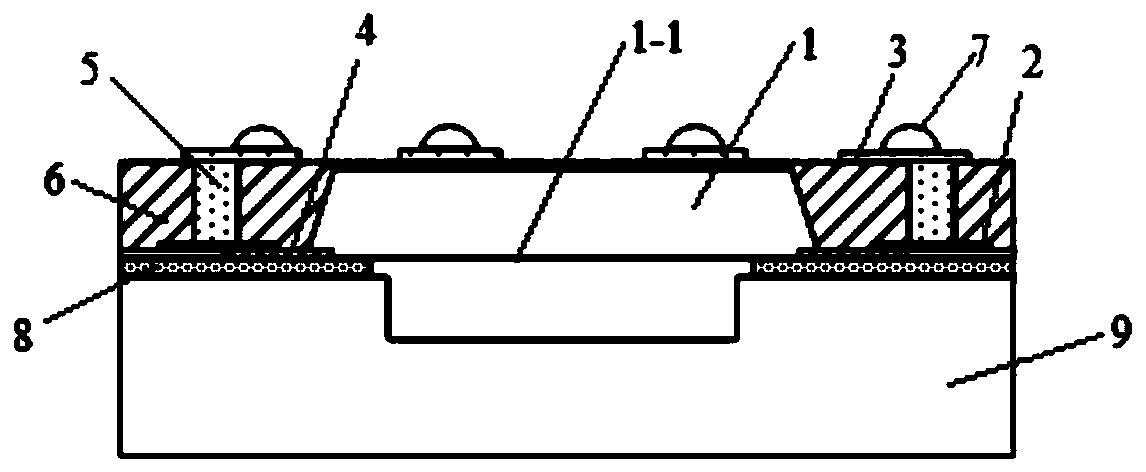

[0041] This embodiment provides a wafer-level packaging structure, see figure 1 , comprising, a plastic encapsulation layer 6, a first wafer 1, a carrier 9, a conductive metal pillar 5, a first redistribution layer 2 and a second redistribution layer 3;

[0042] The first wafer 1 is covered in the plastic encapsulation layer 6, the front surface 1-1 of the first wafer is arranged opposite to the carrier, the carrier is bonded to the front of the first wafer through the bonding layer 8, and there is a groove in the carrier , the groove is arranged opposite to the front surface 1-1 of the first wafer; the conductive metal pillar 5 is arranged through the plastic sealing layer 6, and the first end of the conductive metal pillar is arranged in the plastic sealing layer, and the second end is exposed on one side of the plastic sealing layer; The first redistribution layer 2 is electrically connected to the first end 5-1 of the conductive metal pillar 5 and the front surface of the ...

Embodiment 2

[0046] This embodiment provides an improved scheme for wafer-level packaging structure, see figure 1, comprising, a plastic encapsulation layer 6, a first wafer 1, a carrier 9, a conductive metal pillar 5, a first redistribution layer 2, a second redistribution layer 3, a first pad 4 and a second pad 7;

[0047] The first wafer 1 is covered in the plastic encapsulation layer 6, the front surface 1-1 of the first wafer is arranged opposite to the carrier, the carrier is bonded to the front of the first wafer through the bonding layer 8, and there is a groove in the carrier , the groove is arranged opposite to the front of the first wafer; the conductive metal post 5 is arranged through the plastic encapsulation layer 6, and the first end of the conductive metal post is arranged in the plastic encapsulation layer, and the second end is exposed on the side of the plastic encapsulation layer; the first heavy The wiring layer 2 is electrically connected to the first end 5-1 of the ...

Embodiment 3

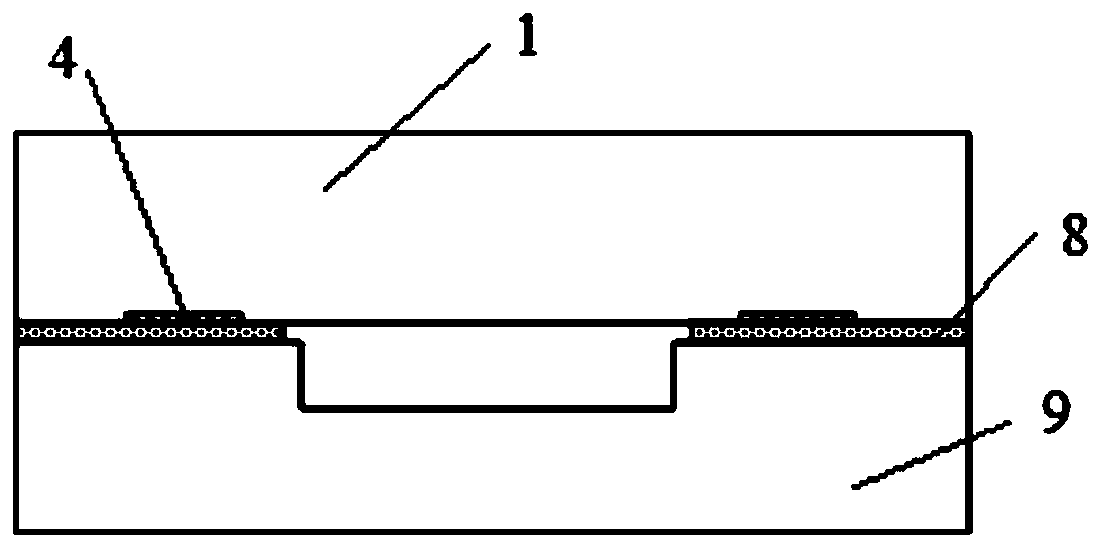

[0051] This embodiment provides a packaging method for a wafer-level packaging structure, the flow chart of which is shown in Figure 2A-Figure 2F , including the following steps,

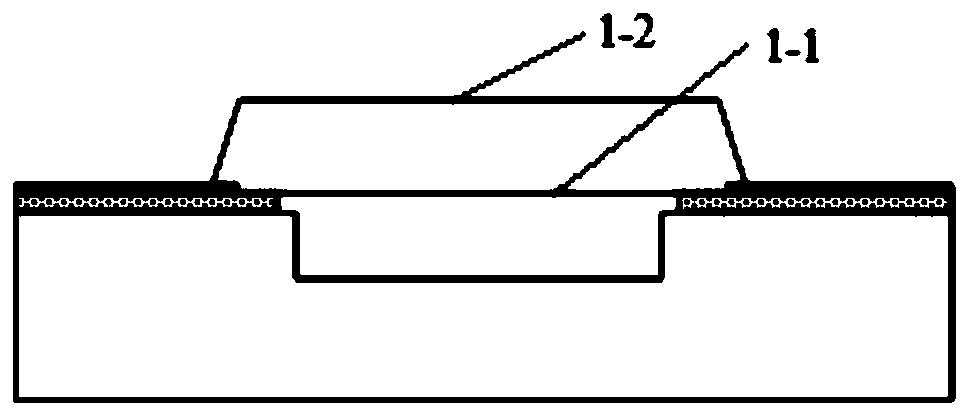

[0052] The first wafer 1 is flip-chip setup, with the front side 1-1 facing down, see Figure 2A , the front of the first wafer is bonded to the carrier 9 through the bonding layer 8, and after mechanical cutting, the back of the first wafer is grooved to form an opening, see Figure 2B , exposing part of the first pad 4;

[0053] The opening is redistributed to form the first redistribution layer 2, see Figure 2C , the top view rendering of the first rewiring layer is shown in image 3 ;

[0054] Through the electroplating process, conductive metal pillars 5 are formed on the first rewiring layer 2, and the plastic sealing layer 6 is formed after filling with glue, see Figure 2D , and then thinning the plastic encapsulation layer, so that the second end 5-2 of the conductive metal post is e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More