A device and method for accurately diagnosing cbit array faults in batches

An open circuit fault, array technology, applied in the direction of measuring devices, measuring electricity, measuring electrical variables, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0118] In an embodiment of the present invention, step S21 may be performed for the diagnosis of a small number of non-adjacent power supply pin VCC channel resources in the cBit array.

[0119] Step S21: For the first type of pin channel resources, the level of the power supply pin VCC does not change, and the level output of all 0 -> all 1 -> all 0 is output by changing the level of its surrounding channels, that is, the level pulse matrix method is used to Diagnose failure of power supply pin VCC channel resource.

[0120] The specific diagnostic result is reflected in step S31, that is, for the first type of pin channel resources, the read value of the unit in the read register corresponding to the VCC channel of the power supply pin is always 1, indicating that the channel is normal; the corresponding position of the VCC channel of the power supply pin The read value is always 0, which means the channel is normally low or an open circuit fault; the read value of the corre...

Embodiment 2

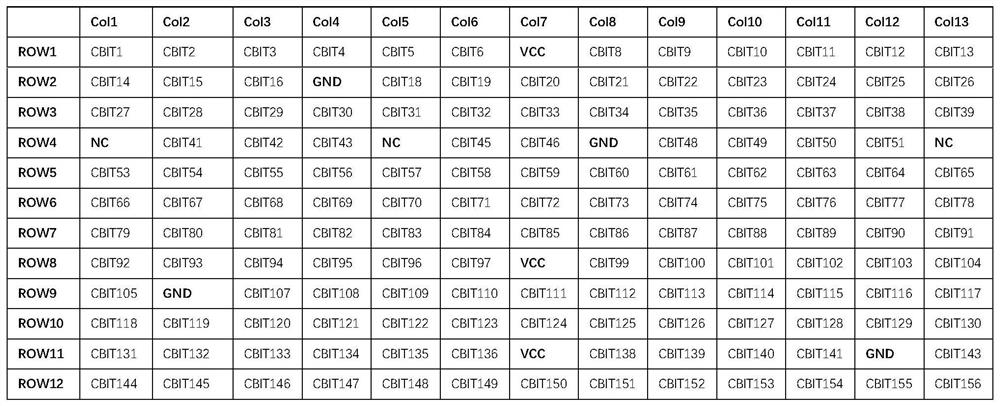

[0129] In the embodiment of the present invention, for the fourth type of pin channel resources, output all 0 -> all 1 -> all 0 diagnosis, specifically include the following steps:

[0130] Step S51: Control all the fourth-type pin channel resources to output all 0s, and obtain and judge whether all 0s are obtained from the data reading control CPLD; control all the fourth-type pin channel resources to output all 1s, and read the data from the control CPLD Obtain and determine whether all 1s are present; control all fourth-type pin channel resources to output all 0s, and obtain and determine whether all 0s are obtained from the data reading control CPLD. The effect of outputting all 0 is as follows

[0131] Table 3 shows:

[0132] Col1 Col2 Col3 Col4 Col5 Col6 Col7 Col8 Col9 Col10 Col11 Col12 Col13 ROW1 0 0 0 0 0 0 0 0 0 0 0 0 0 ROW2 0 0 0 0 0 0 0 0 0 0 0 0 0 ROW3 0 0 0 0 0 0 VCC 0 0 0 0 ...

Embodiment 3

[0138] In the embodiment of the present invention, step S23 can be executed for fault diagnosis such as a short circuit of the fourth type of pin channel resource, which specifically includes the following steps:

[0139] Step S231: Set Row=1, Col=1 to 1, and other positions to 0; the result is as follows

[0140] Table 5 shows:

[0141] Col1 Col2 Col3 Col4 Col5 Col6 Col7 Col8 Col9 Col10 Col11 Col12 Col13 ROW1 1 0 0 0 0 0 0 0 0 0 0 0 0 ROW2 0 0 0 0 0 0 0 0 0 0 0 0 0 ROW3 0 0 0 0 0 0 VCC 0 0 0 0 0 0 ROW4 0 0 0 0 0 0 0 0 0 0 0 0 0 ROW5 0 0 0 0 0 0 0 0 0 0 0 0 0 ROW6 0 0 0 GND 0 0 0 0 0 0 0 0 0 ROW7 0 0 0 0 0 0 0 0 NC 0 0 0 0 ROW8 0 0 0 0 0 0 0 0 0 0 0 0 0 ROW9 0 0 0 0 0 0 0 0 0 0 0 0 0 ROW10 0 0 0 0 0 0 0 0 0 0 0 0 0 ROW11 0 0 0 0 0 0 0 0 0 0 0 0 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More