PCIE exchange chip port configuration system and method

A technology for switching chips and configuring systems, which is applied in transmission systems, digital transmission systems, data switching networks, etc., and can solve problems such as difficult to find PCIE switching chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

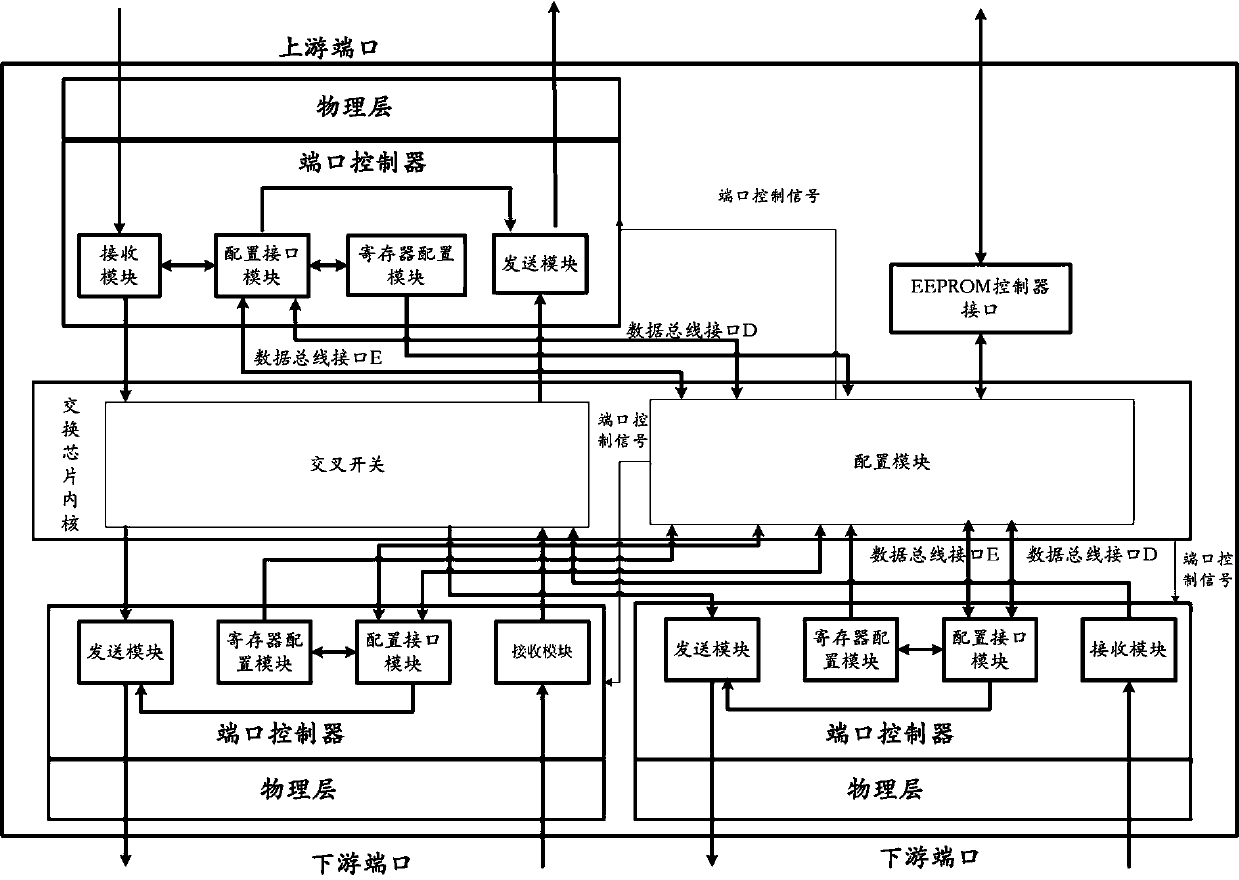

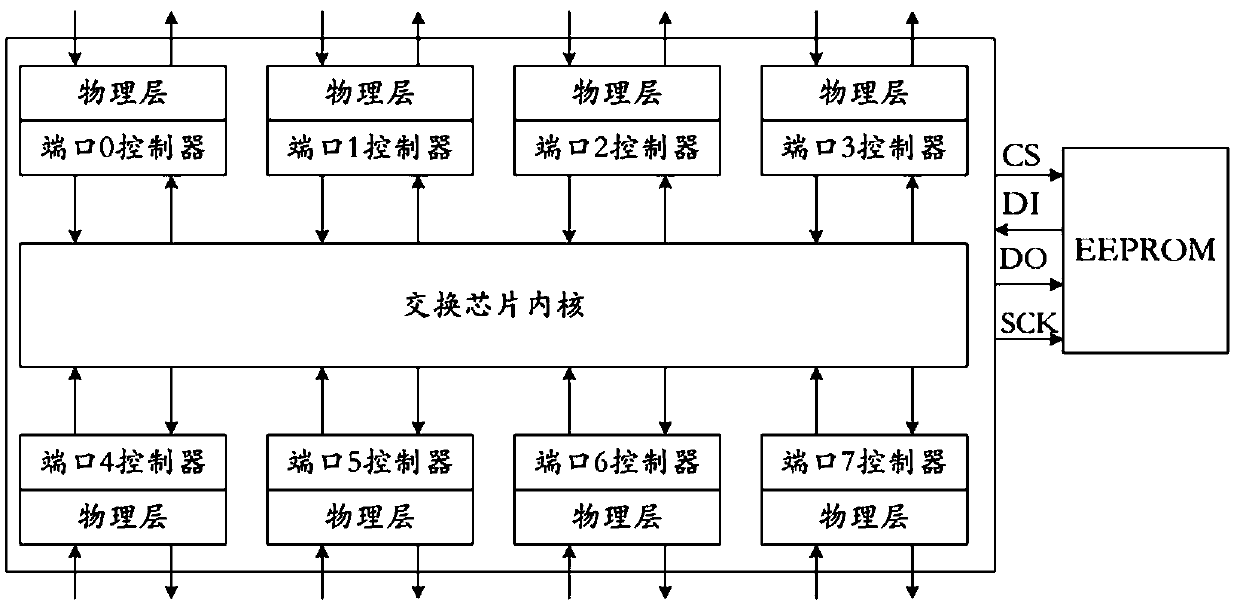

[0078] figure 1 For the PCIE switch chip port configuration system structural representation according to the present invention, as figure 1 As shown, the PCIE switch chip port configuration system of the present invention mainly includes a switch chip core, a port controller, and an EEPROM controller interface module. In this system, a piece of EEPROM is externally connected to the PCIE switch chip, and it is initialized and loaded through the external EEPROM. In general, the PCIE switch chip port configuration system has n ports, where n is a natural number not less than three, and each port receives data from the external PCIE link through its entry-side physical layer and port controller input side, and the received data It is directly processed by the port controller, and the receiving port controller can also forward the received data packet to the switch chip core according to the situation, and then forwarded by the switch chip core to the port controller of other por...

Embodiment 2

[0098] The detailed processing flow of the port configuration implementation mechanism of the PCIE switch chip port configuration system is as follows:

[0099] Power on the PCIE switch chip, read the configuration information from the external EEPROM, and send it to the configuration module.

[0100] In this step, during the power-on process of the PCIE switch chip, if it is judged that there is an external EEPROM chip, and the first byte read from the EEPROM is 5Ah, it means that the EEPROM is not empty, and the EEPROM controller interface module is connected from the external Read the configuration information of each port configuration register in the EEPROM and send it to the configuration module.

[0101] The configuration module receives the configuration information from the interface of the external EEPROM controller, according to the configured port number, sends it to the configuration interface module in the port controller of the corresponding port through the dat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More