Chip packaging structure and manufacturing method thereof

A technology of chip packaging structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts, semiconductor devices, etc., can solve problems affecting the quality of semiconductor devices, achieve compact packaging structure and improve product yield , Guarantee the effect of quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

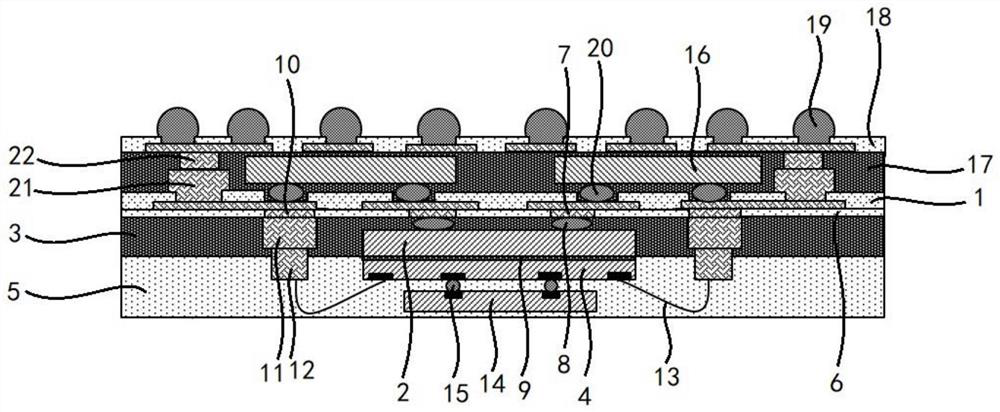

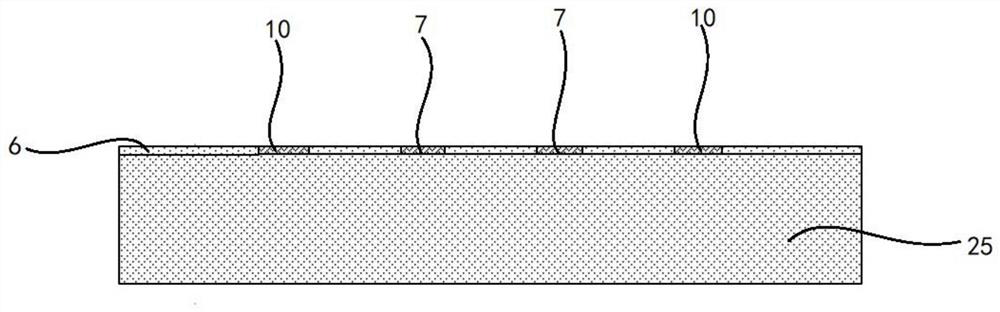

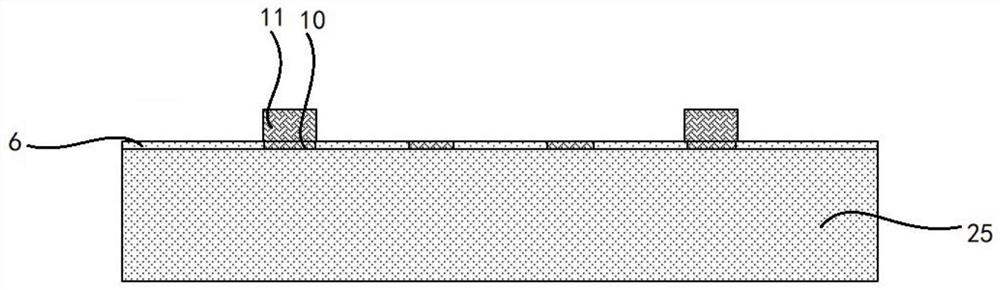

[0105] As an embodiment of the present invention, before making the first plastic package 3, it also includes:

[0106] Making a first conductive column 11 on the dielectric layer 6, the first conductive column 11 is encapsulated by the first plastic package 3;

[0107] After making the first plastic package 3, it also includes:

[0108] A first opening 23 is opened on the first plastic package 3 to expose the end surface of the first conductive column 11 facing away from the dielectric layer 6;

[0109] Make the second conductive post 12 at the first opening 23, so that the second conductive post 12 is electrically connected to the first conductive post 11, and the end face of the second conductive post 12 on the side away from the first conductive post 11 is higher than the first plastic package 3 ;

[0110] Conductive wires 13 are fabricated to connect the second chip 4 and the second conductive pillars 12 .

[0111] The manufacturing method of the chip package structure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com