High-throughput-rate LDPC decoding algorithm and architecture for 5G terminal

A high-throughput, decoding algorithm technology, applied in the field of high-throughput LDPC decoding algorithms and architectures, can solve problems such as impracticality and complex decoding steps, and achieve low implementation complexity, high throughput, The effect of small loss of decoding performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

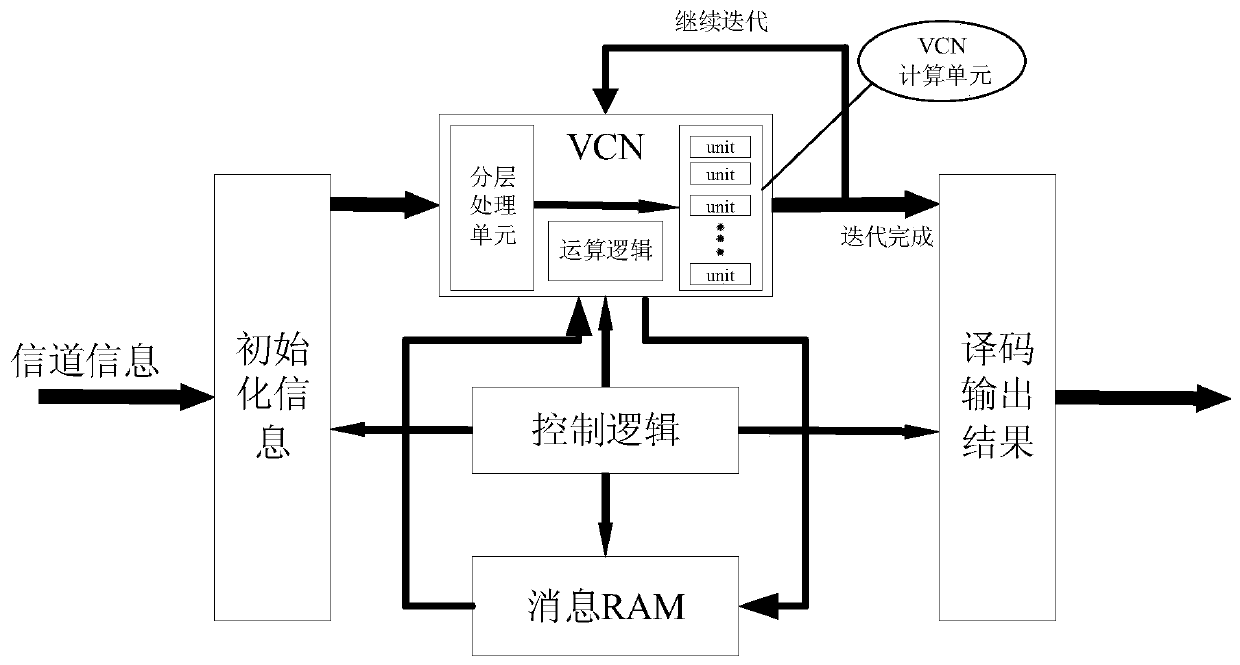

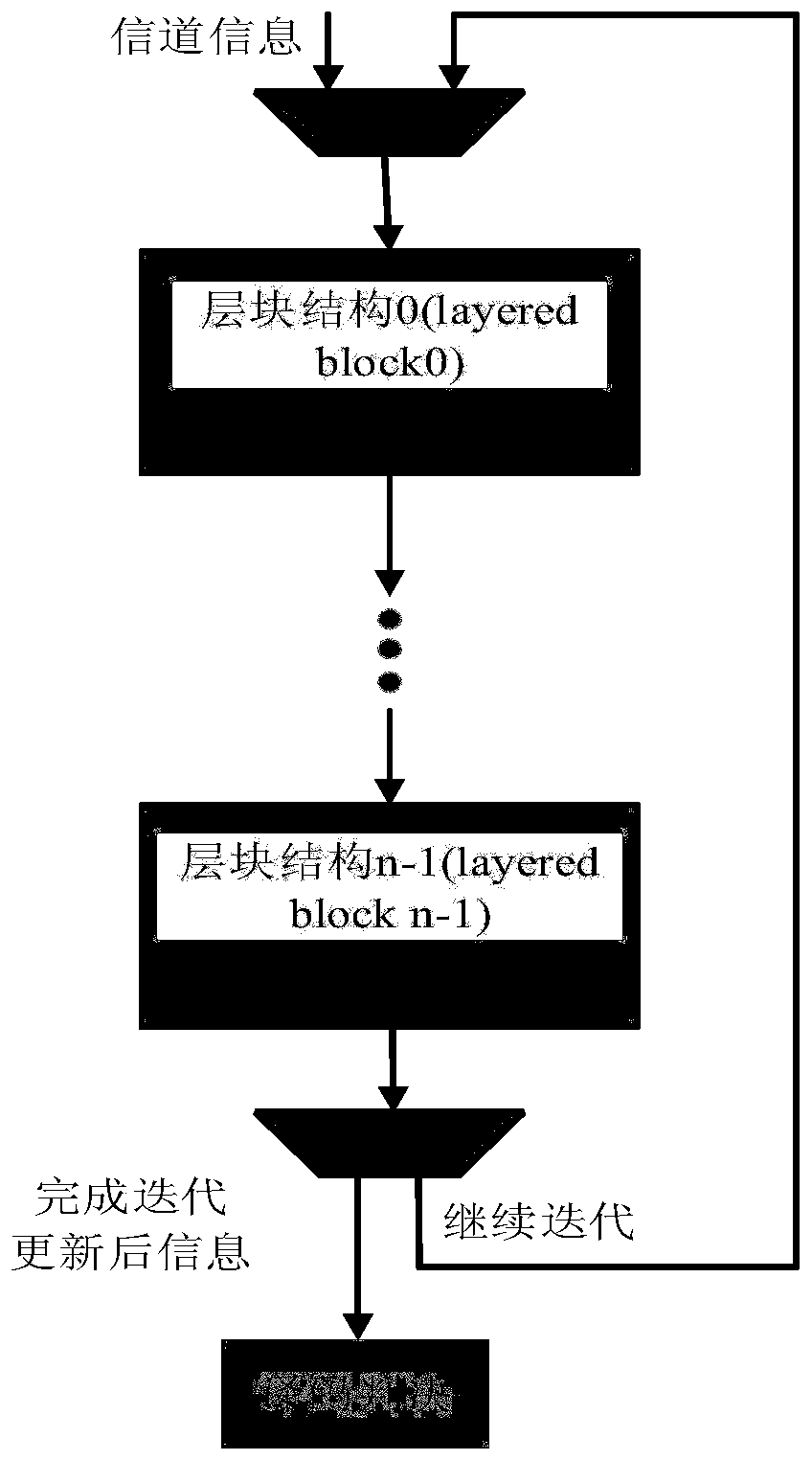

[0044] figure 2 A brief architecture for the 5G terminal decoder, such as figure 2 As shown, it is a brief structure of the 5G terminal decoder. Under the control of the control logic module, the channel information enters the decoder. After related processing, the calculation unit in the VCN module is used to update the node. The inherent The information and the intermediate information in the node update process are stored in the message RAM, and finally the decoding result is output. In the VCN module, node update is mainly performed, that is, the realization of the layered scheduling minimum sum decoding algorithm in the present invention, and other calculation processes.

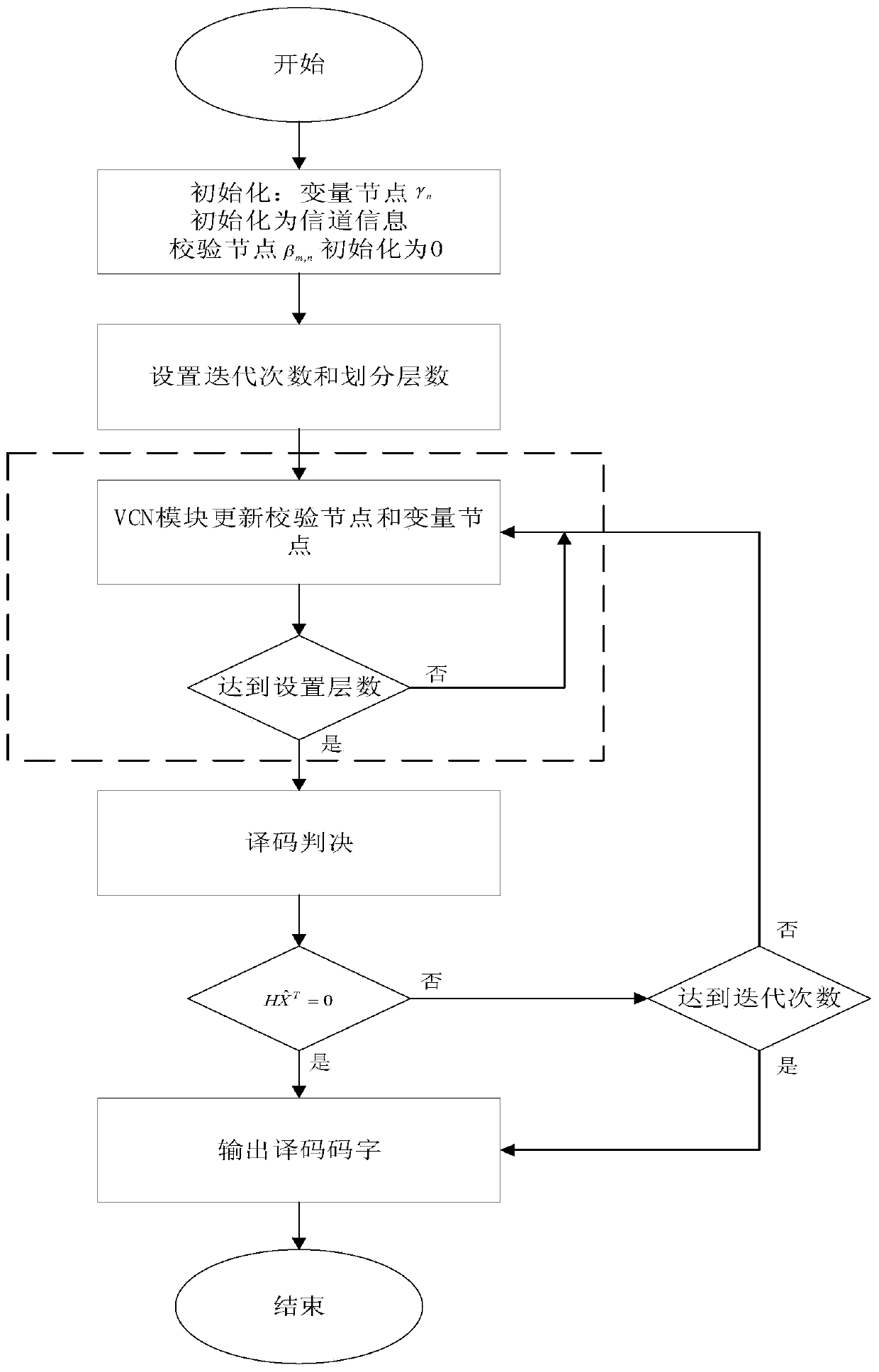

[0045] figure 1 It is the LDPC hierarchical scheduling minimum sum decoding algorithm flow. In the decoding process, the main steps are: initialize variable nodes ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More