Fan-out type wafer level packaging structure and manufacturing method thereof

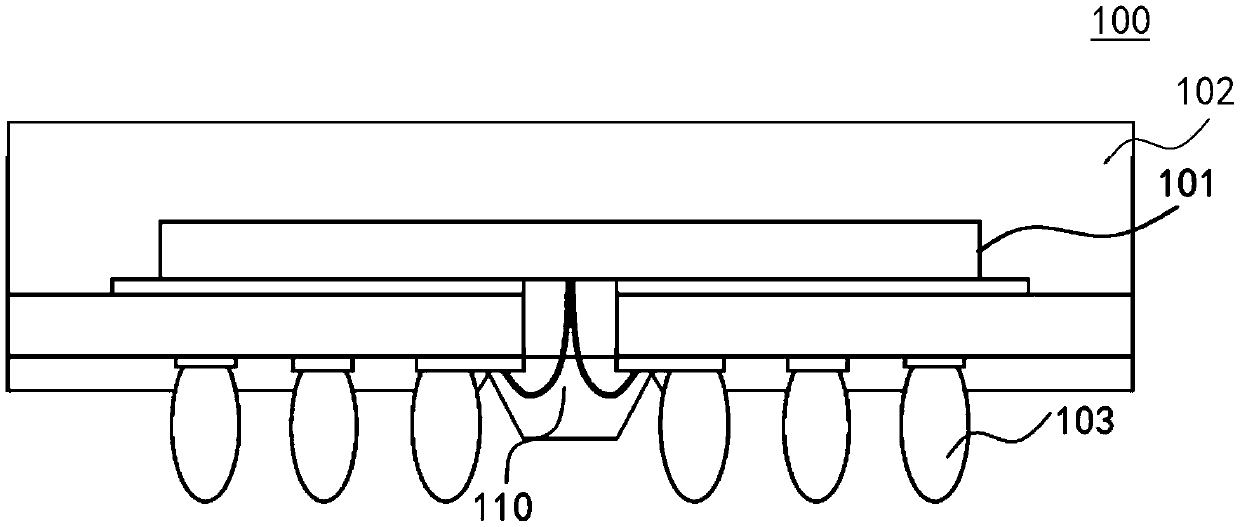

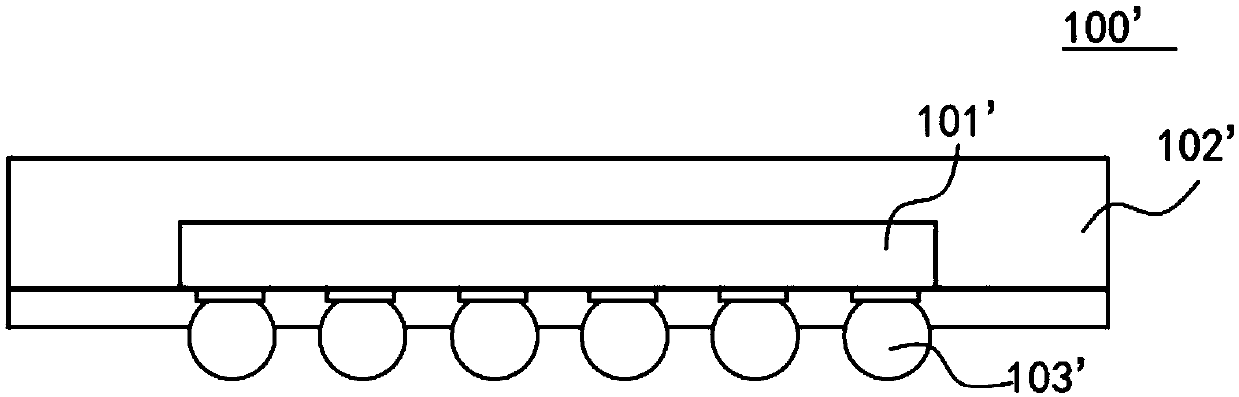

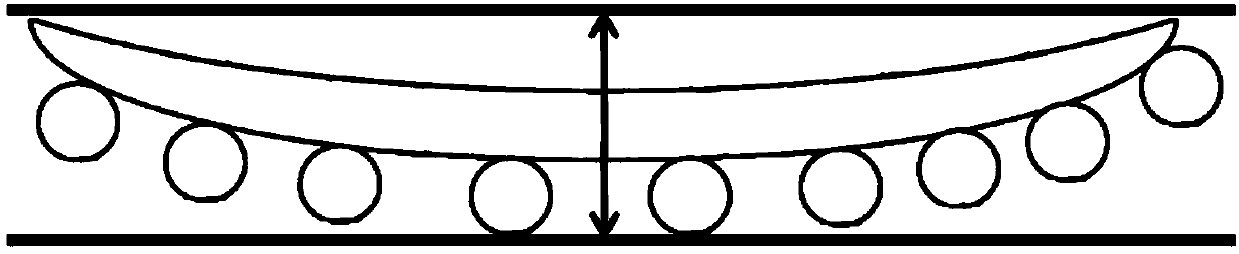

A technology of wafer-level packaging and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problem that the structure is easy to warp and increase the difficulty of the ball pin process of the redistribution layer , large differences in thermal expansion coefficients, etc., to reduce the difficulty of the process, reduce the size of the package structure, and reduce the warpage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The following is a specific example to illustrate the implementation of the "manufacturing method of fan-out wafer level packaging structure" and "fan-out wafer level packaging structure" disclosed in the present invention. Those skilled in the art can learn from this specification The disclosed content understands the advantages and effects of the present invention. The present invention can be implemented or applied through other different specific embodiments, and various modifications and changes can be made to the details in this specification based on different viewpoints and applications without departing from the concept of the present invention. The following embodiments will further describe the relevant technical content of the present invention in detail, but the disclosed content is not intended to limit the protection scope of the present invention.

[0024] The invention provides a method for manufacturing a fan-out wafer level packaging structure. see ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More