On-chip distributed interconnection bus system and multi-core processor

An interconnected bus and distributed technology, applied in the field of data transmission, can solve the problems of system performance degradation, ring bus structure advantages are not guaranteed, etc., to achieve the effect of improving arbitration efficiency, reducing collisions, and increasing data transmission rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

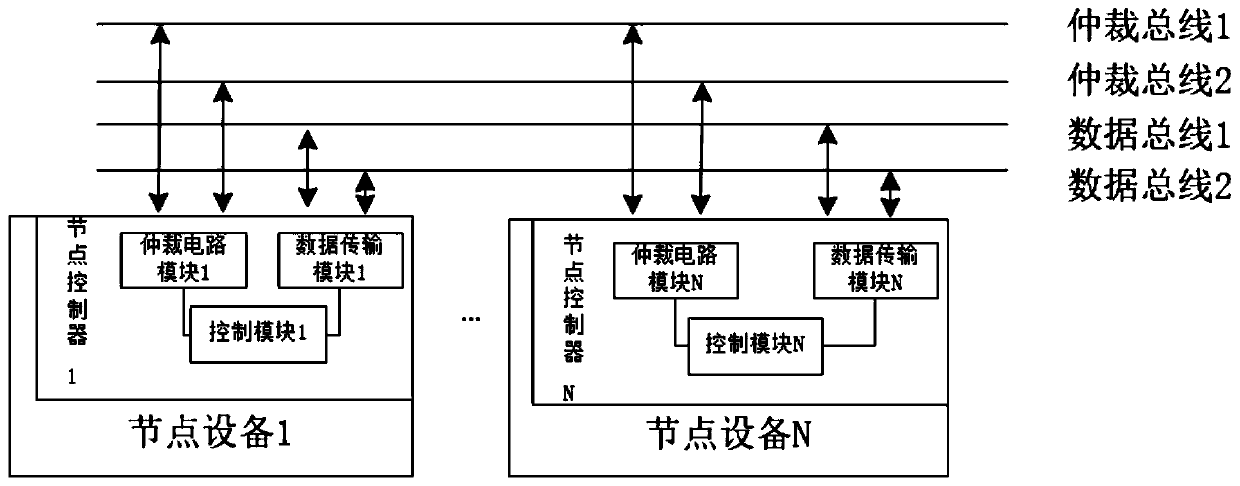

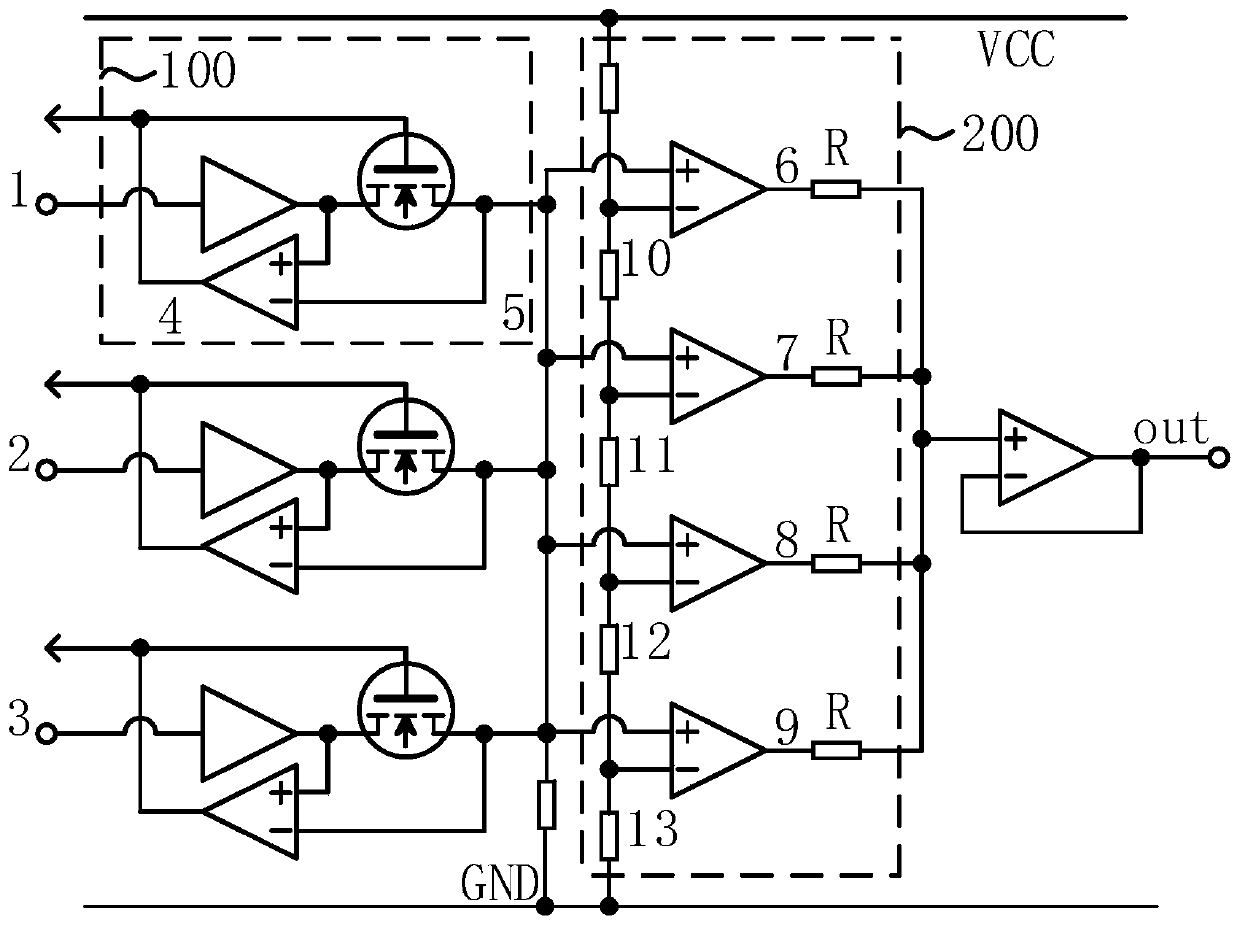

[0042] Please refer to figure 1 and Figure 4 , the on-chip distributed interconnect bus system includes:

[0043] At least two sets of data buses transmit data to be sent by node devices through data frames;

[0044] At least one group of arbitration buses transmits multi-ary symbols of node devices through arbitration frames, the multi-ary symbols including different voltage amplitude states separated by a plurality of thresholds;

[0045] a node controller, located in the node device, the node controller is respectively connected with two sets of data buses and an arbitration bus, and is used for outputting the multi-digit symbols or the data to be sent of the node device;

[0046] The node controller compares the multi-symbol voltage with the multi-symbol voltage on the arbitration bus, and if the multi-symbol priority is higher than the multi-symbol priority on the arbitration bus, then The binary symbol is output to the arbitration bus, and the data to be sent is sent...

Embodiment 2

[0104] Please refer to Figure 5-Figure 7 , the difference between the second embodiment and the first embodiment is:

[0105] Also includes a bus repeater connected to the two groups of data buses and the arbitration bus, the bus repeater includes a node controller, a secondary arbitration bus with the same functional structure as the arbitration bus, and the two groups of data buses. Two sets of secondary data buses with the same functional structure, the node controller can be connected to the bus repeater through the secondary arbitration bus and the two sets of secondary data buses;

[0106] Specifically, the bus repeater further includes a secondary bus control module and a cache module, the secondary bus control module includes an arbitration control module and a data transmission module, the arbitration control module is connected to the secondary arbitration bus, so the data transmission module is connected to the secondary data bus;

[0107] The secondary data bus ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More