Processor core verification method and system based on synchronous execution and medium

A technology of processor core and verification method, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., to achieve the effects of easy implementation, accurate positioning, and reduced impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

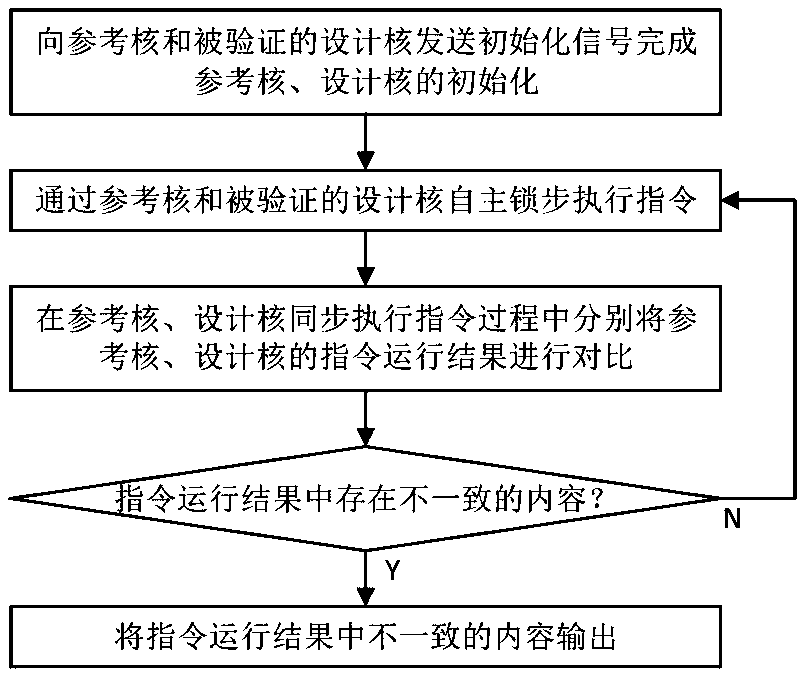

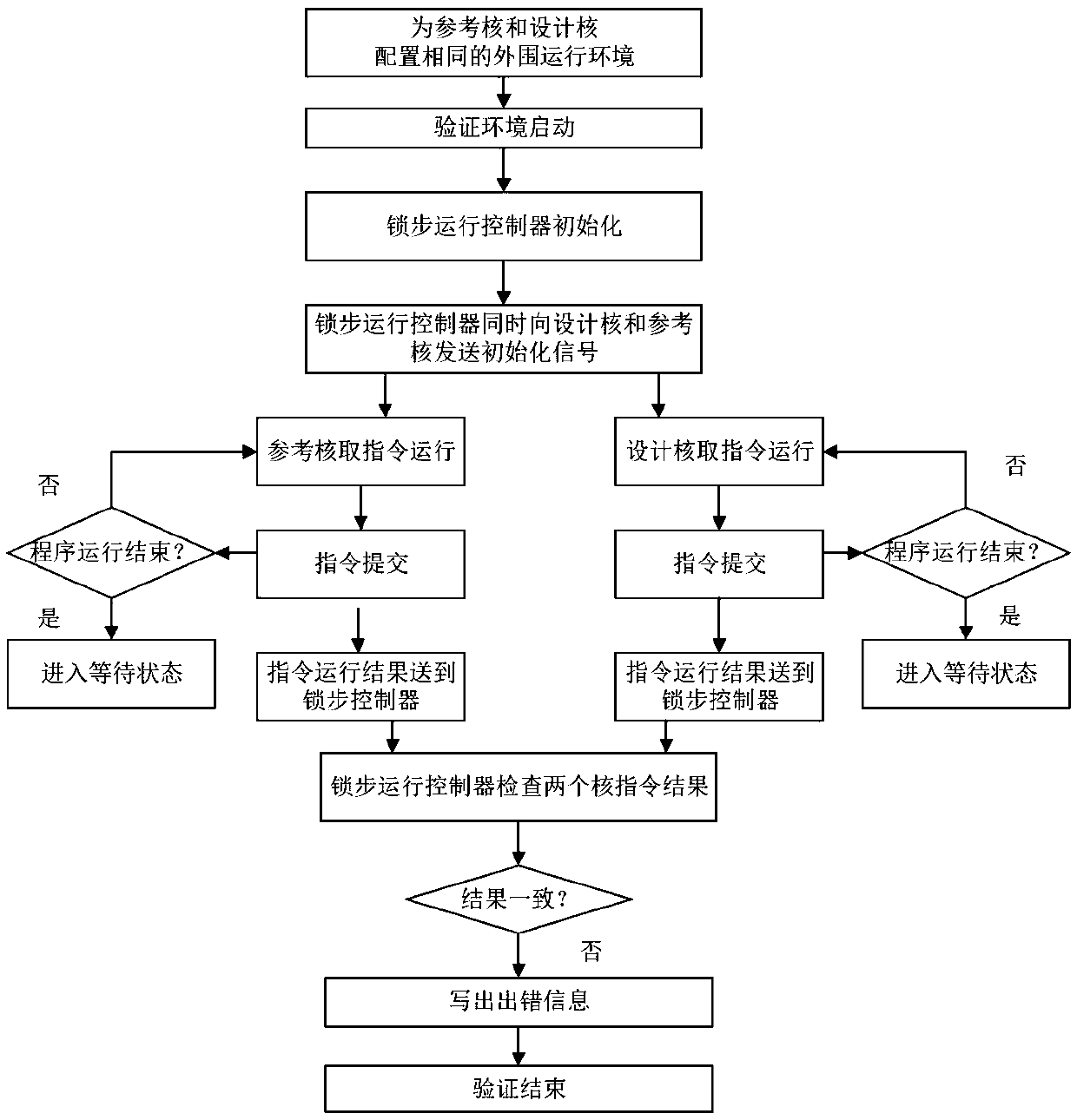

[0030] Such as figure 1 As shown, the implementation steps of the processor core verification method based on synchronous execution in this embodiment include:

[0031] 1) Send an initialization signal to the reference core and the verified design core to complete the initialization of the reference core and the design core;

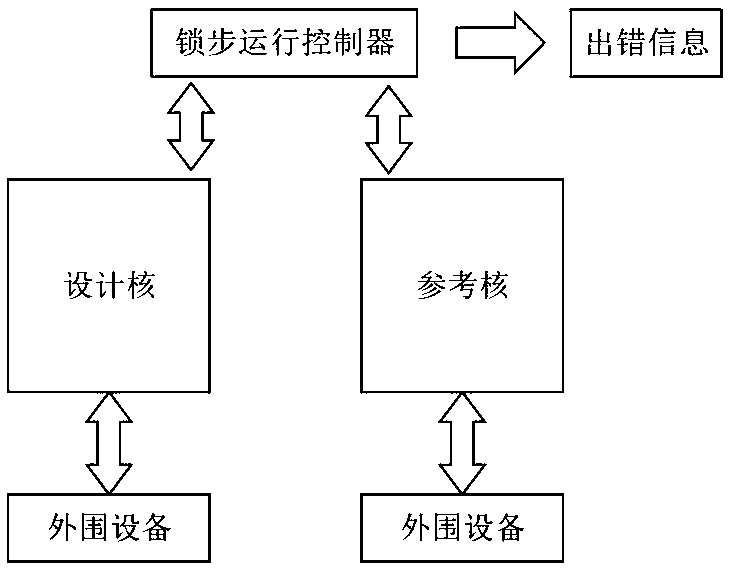

[0032] 2) The reference core and the verified design core execute instructions in lockstep, and compare the instruction operation results of the reference core and the design core during the synchronous execution of instructions by the reference core and the design core, and compare the inconsistencies in the instruction operation results content output. The definitions of design cores and reference cores involved in this embodiment are explained as follows:

[0033] Design core: It is a design that needs to be verified. This design core is a fully functional processor core that can fetch instructions for execution, read data from the main memory, perf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More