Visual brain-computer interface method based on field-programmable gate array local noise optimization

A technology of brain-computer interface and gate array, which is applied in the field of visual brain-computer interface based on field programmable gate array local noise optimization, can solve problems such as visual fatigue, refresh rate limitation, and limited frequency of display paradigm stimulation, and reduce visual fatigue , reduce implementation costs, and improve stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

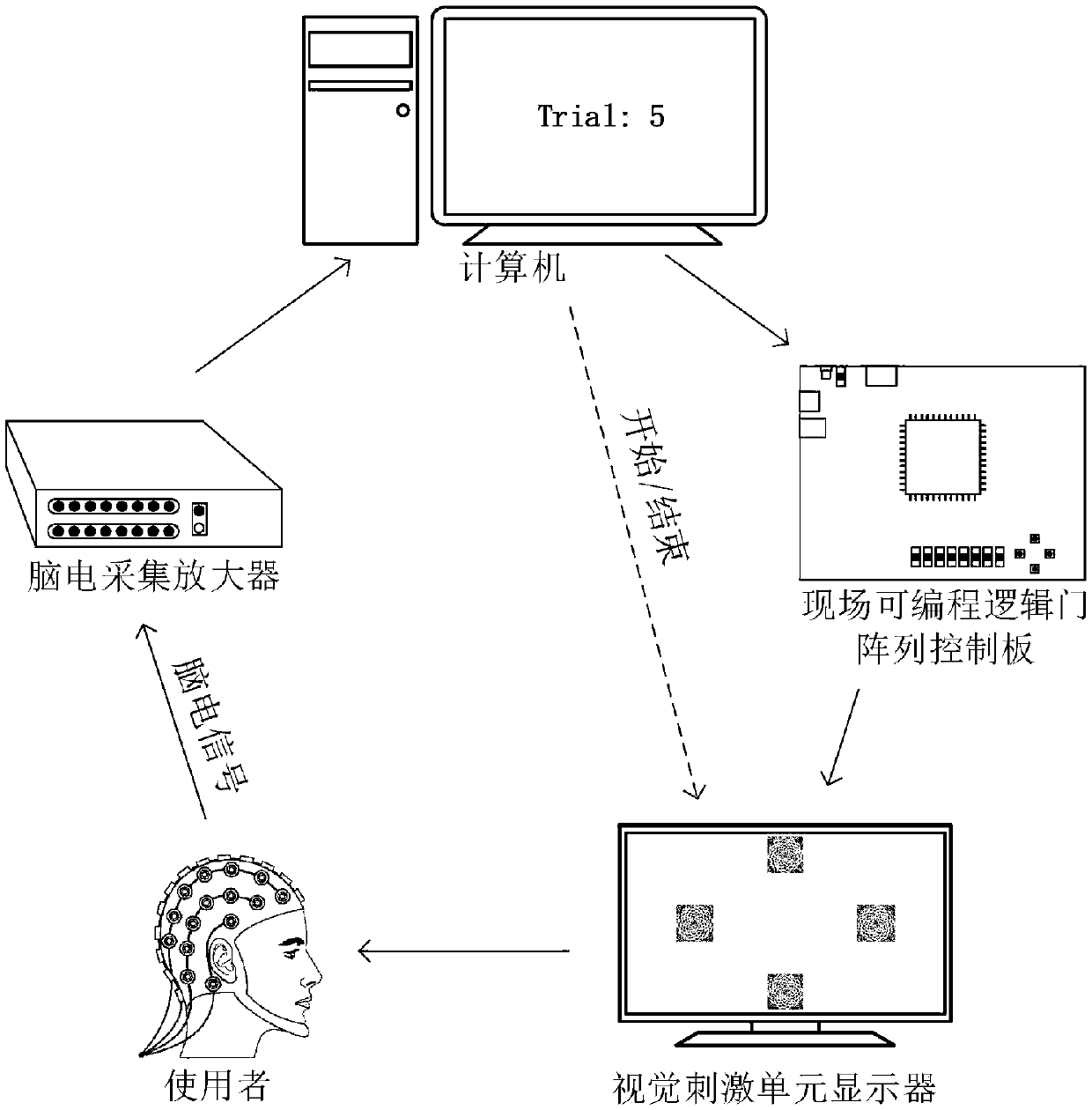

[0054] refer to figure 1 , a visual brain-computer interface method based on field programmable gate array local noise optimization, comprising the following steps:

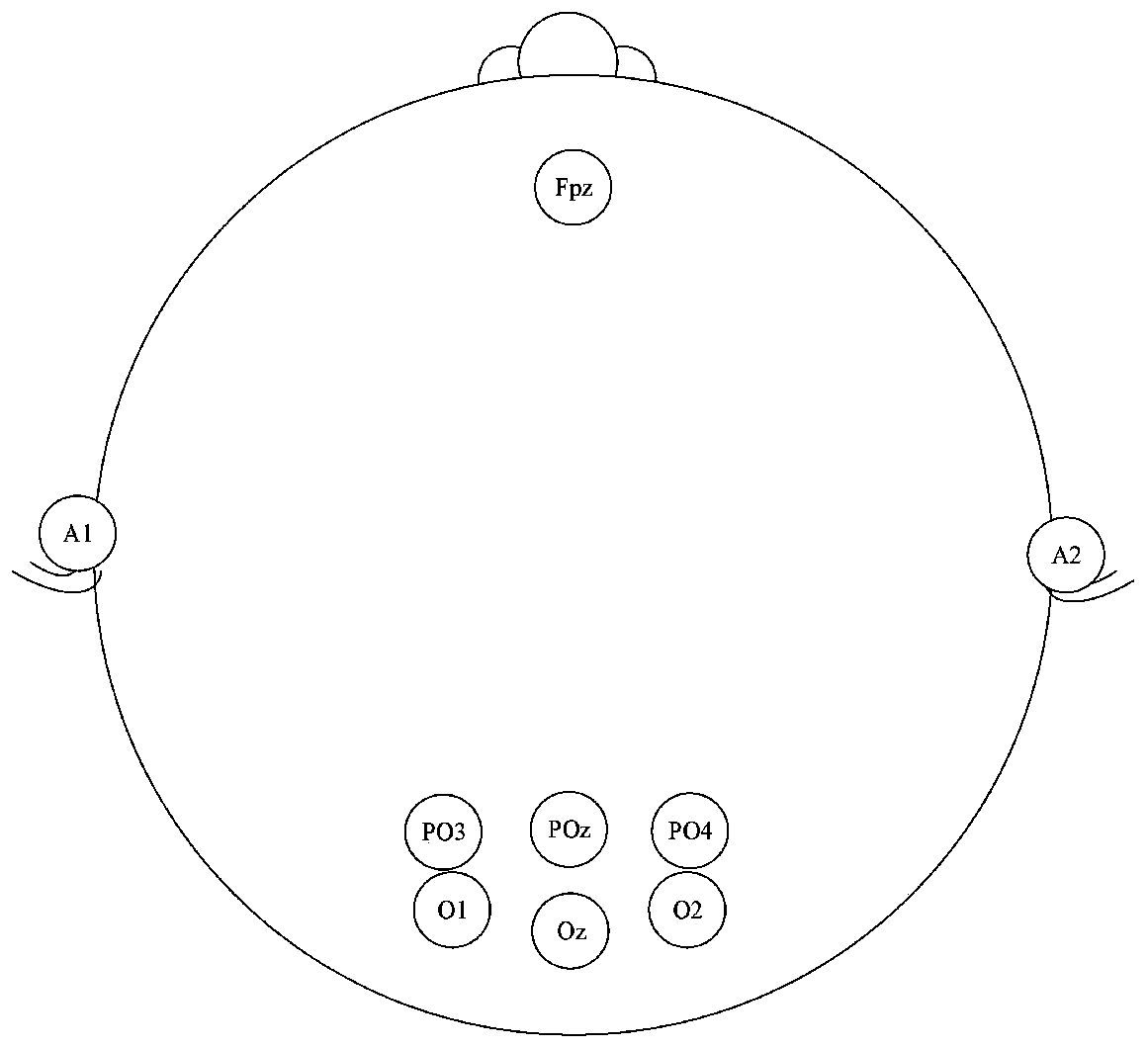

[0055] Step 1, such as figure 2 As shown, according to the international standard lead 10-20 system, the EEG signal measurement electrodes are placed on the PO3, POz, PO4, O1, Oz and O2 positions of the visual occipital area of the user's head through the EEG cap, and the Fpz on the forehead The ground electrode is placed at the position, and the reference electrode is placed at any ear lobe position A1 or A2. The measured EEG signal is amplified by professional acquisition equipment, converted from analog to digital, and then transmitted to the computer terminal;

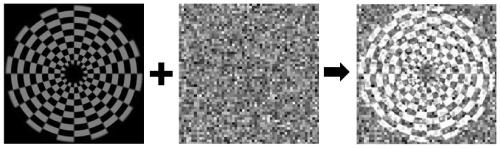

[0056] Step 2, refer to image 3 with Figure 4 , presenting four visual stimulation units with local noise ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More