Transistor and forming method thereof

A technology of transistors and dielectric layers, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of transistor reliability influence, transistor instability, transistor static power consumption increase, etc., to improve gate induction Leakage current, the effect of overcoming gate-induced leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

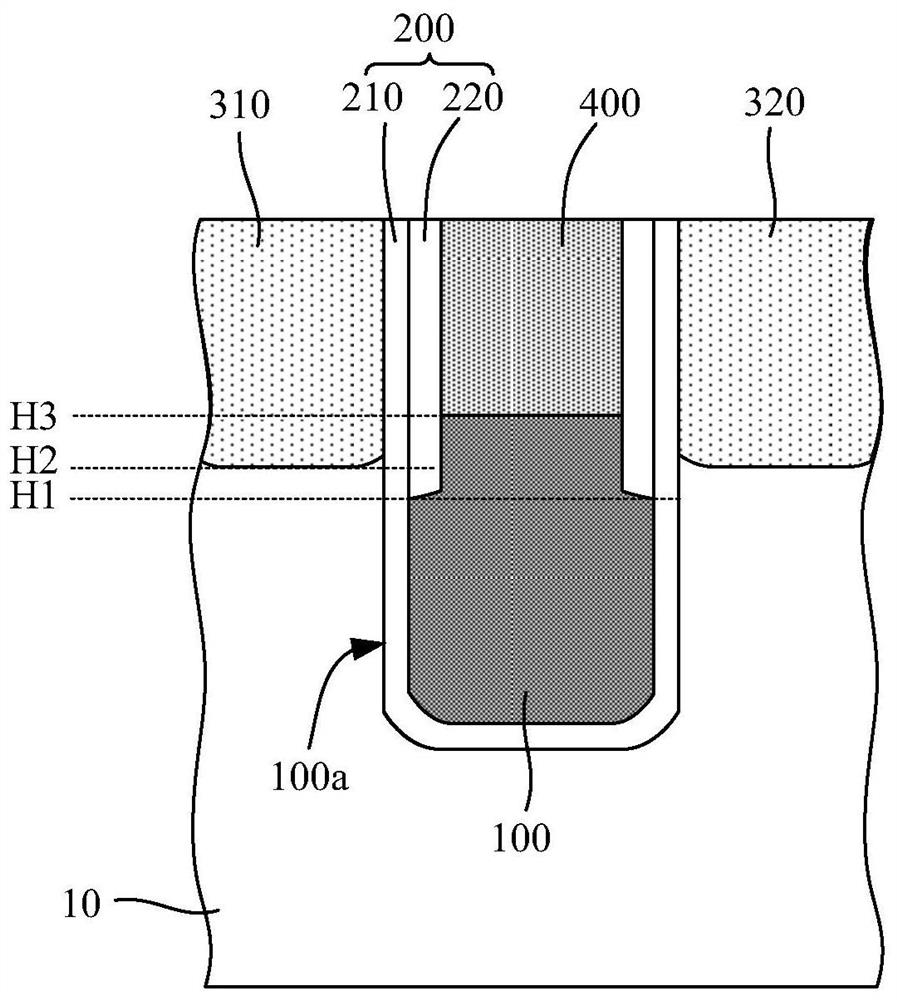

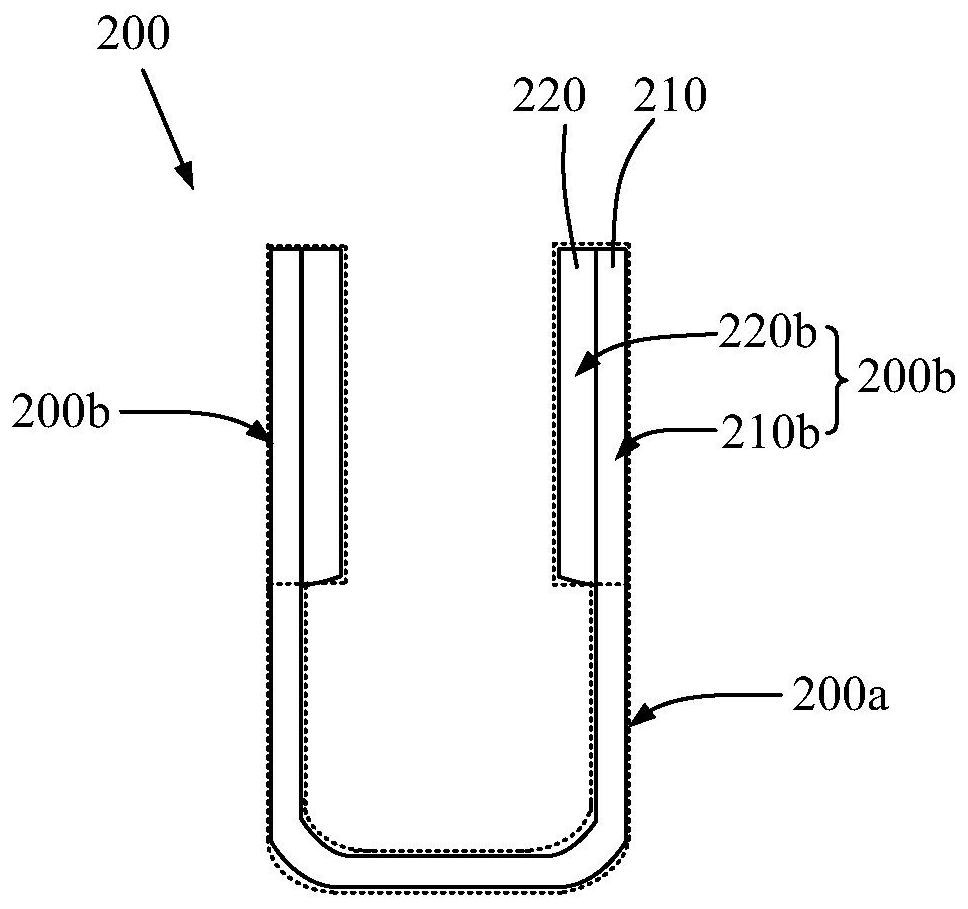

[0070] Figure 1a is a schematic structural diagram of a transistor in Embodiment 1 of the present invention, Figure 1b It is a schematic structural diagram of the gate dielectric layer of the transistor in Embodiment 1 of the present invention. like Figure 1a and Figure 1b As shown, the transistor includes: a substrate 10 in which a gate trench 100a is formed; and a gate dielectric layer 200 covering the inner wall of the gate trench 100a.

[0071] key reference Figure 1b and combine Figure 1a As shown, the gate dielectric layer 200 has an upper layer part 200b and a lower layer part 200a, and the upper layer part 200b covers the inner wall of the gate trench 100a higher than the predetermined height position (ie, the first height position H1), so The lower portion 200 a covers the inner wall of the gate trench 100 a lower than the predetermined height position (ie, the first height position H1 ).

[0072] Wherein, the upper layer part 200b is a laminated structure, s...

Embodiment 2

[0113] The difference from Embodiment 1 is that, in the gate dielectric layer in this embodiment, the upper portion protrudes toward the inner wall of the trench relative to the lower portion. Combine the following Figure 3a and Figure 3b The transistors in this embodiment will be described in detail.

[0114] Figure 3a It is a schematic structural diagram of the transistor in Embodiment 2 of the present invention, Figure 3b It is a schematic structural diagram of the gate dielectric layer of the transistor in the second embodiment of the present invention. like Figure 3a and Figure 3b As shown, in this embodiment, the gate dielectric layer 200' includes a first dielectric layer 210' and a second dielectric layer 220'.

[0115] Wherein, the first dielectric layer 210' covers the inner wall of the gate trench 100a' higher than the predetermined height position (the first height position H1), and is used to form the lining layer 210b' of the upper part 200b'. The se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More