MOSFET chip layout structure

A layout structure and chip technology, applied in electrical components, transistors, circuits, etc., can solve the problems of high chip on-resistance, insufficient chip performance, large chip area, etc., to improve chip performance, reduce chip cost, and reduce conduction. The effect of resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be described in further detail below in conjunction with examples and specific implementation methods.

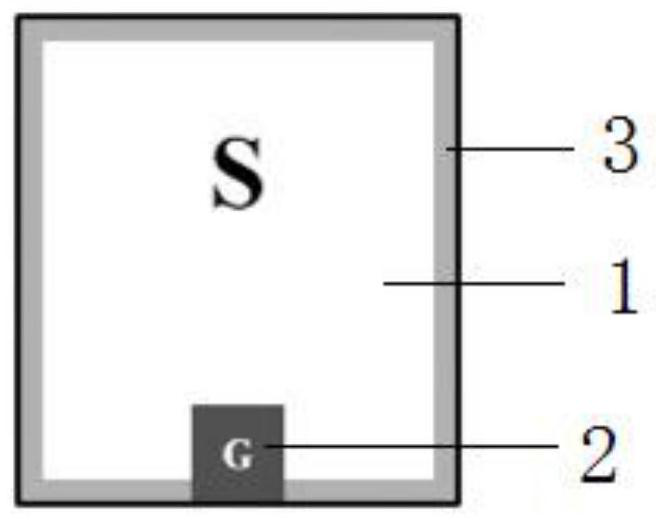

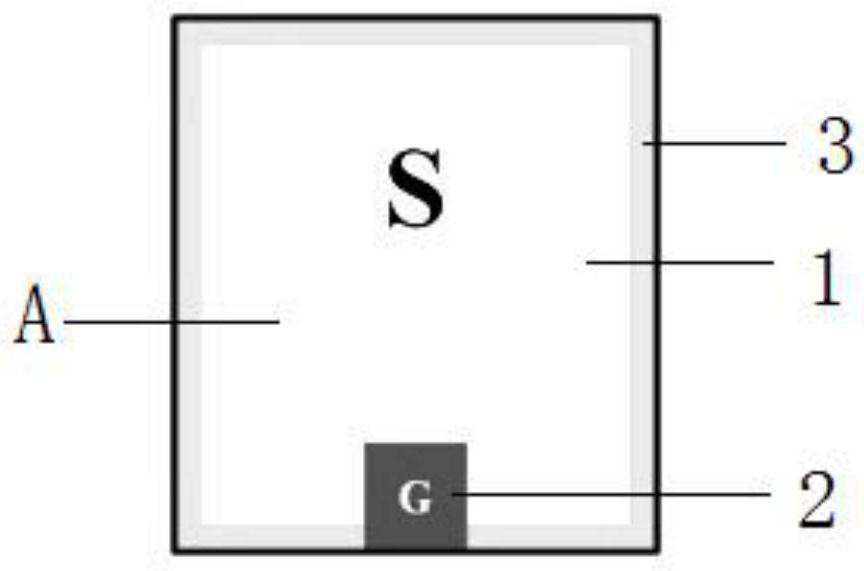

[0020] like image 3 As shown, a MOSFET chip layout structure is applied to a MOSFET chip, including the first layer of source metal at the bottom and the second layer of source metal in contact with the top surface of the first layer of source metal, the first layer of source metal The electrode metal is the source region 1 surrounded by the gate bus bar 3, the gate bus bar 3 has a gate etching window, the second layer of source metal covers the first layer of source metal, and the second layer of source metal A gate bonding region 2 is provided on the metal to be in contact with a gate bus bar 3 through a gate etching window.

[0021] The area of the source metal of the second layer is larger than the area of the source metal of the first layer.

[0022] like figure 2 , 3 As shown, a method for manufacturing a MOSFET chip layout ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More