Dynamic random access memory

A technology of dynamic random access and memory, which is applied in the field of memory, can solve the problems of hysteresis effect of memory effect, reduce product reliability, threshold voltage floating, etc., achieve the effect of improving reliability, avoiding threshold voltage floating, and improving floating body effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

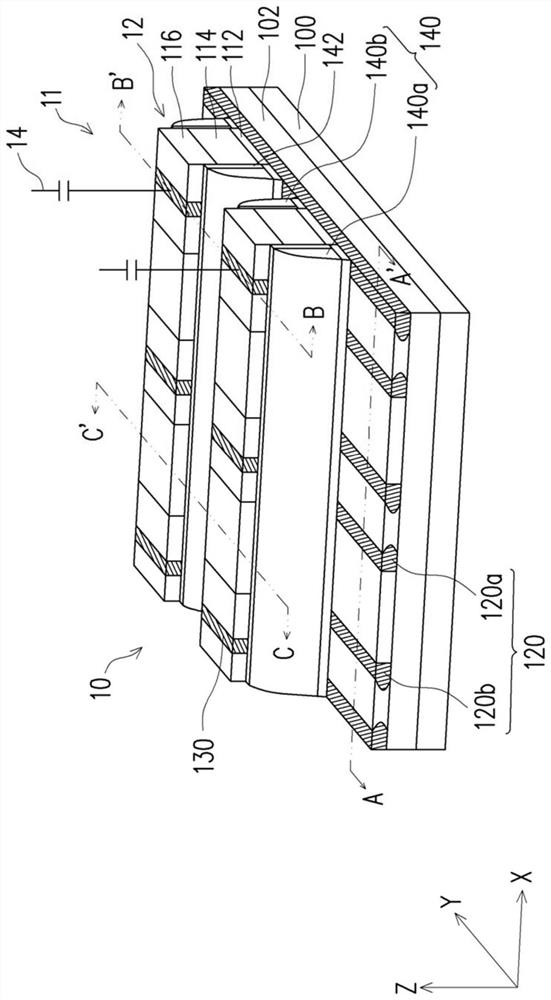

[0036] figure 1 It is a three-dimensional schematic diagram of a DRAM according to an embodiment of the present invention. In this example, figure 1 The DRAM 10 may for example be based on 4F 2 Array-arranged dynamic random access memory. For clarity, some components are omitted.

[0037] Please refer to figure 1 , in this embodiment, the DRAM 10 includes a plurality of storage units 11, the storage units 11 are located on the substrate 100, and each storage unit 11 includes a transistor 12 and a capacitor 14, wherein the capacitor 14 is located on the transistor 12 and is connected with the The transistor 12 is electrically connected. In this embodiment, the transistor 12 is, for example, a vertical transistor. Hereinafter, some components will be further described in detail.

[0038] Please continue to refer to figure 1 , in this embodiment, the DRAM 10 includes, for example, a substrate 100 , a plurality of transistors 12 , a plurality of bit line groups 120 , a plu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More