Fin field-effect transistor, fin and fabrication method for fin

A technology of fin field effect and manufacturing method, applied in the field of fins and their manufacture, and fin field effect transistors, can solve the problems of difficult process, high control, high thermal budget, low cost, etc., so as to reduce the manufacturing cost, and the process is simple and easy row effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

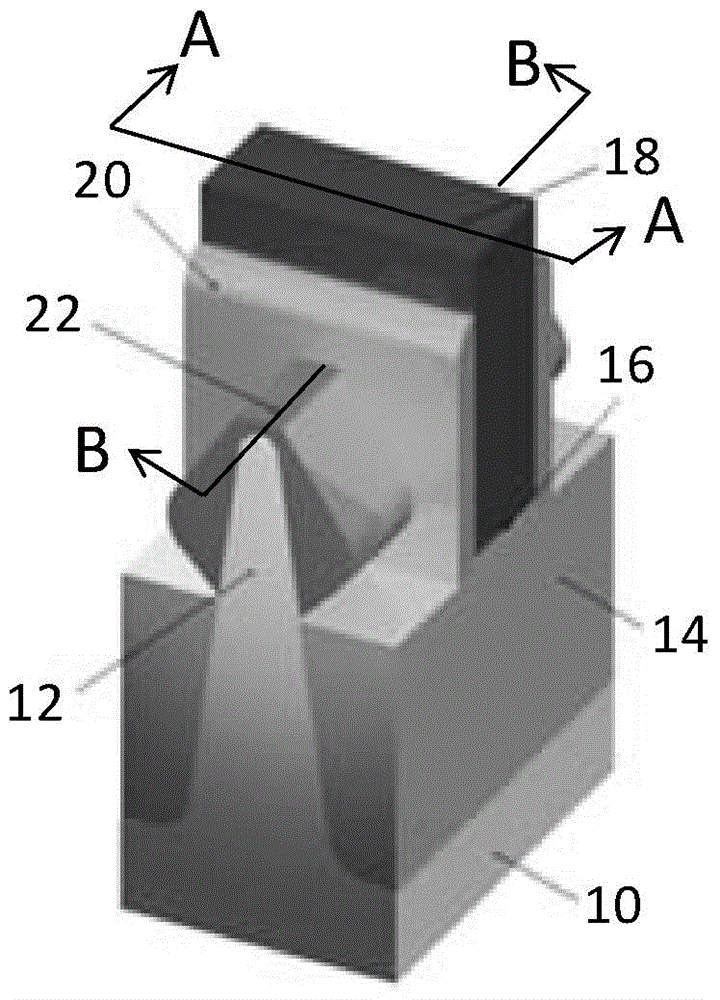

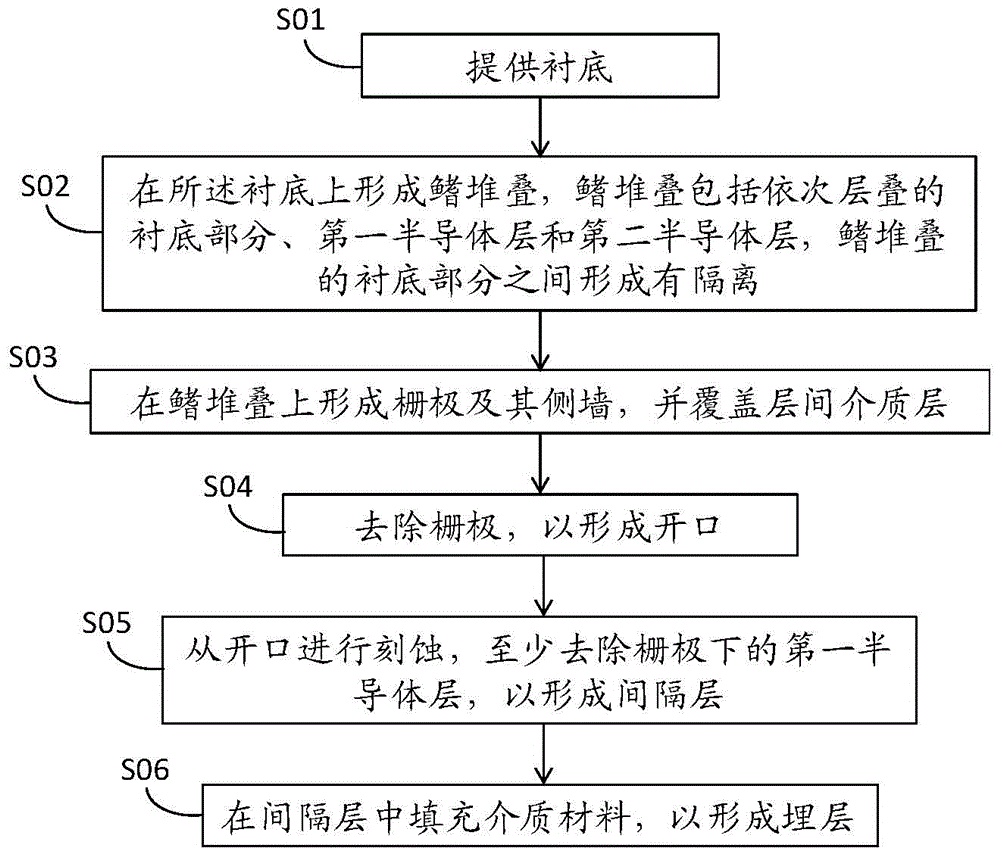

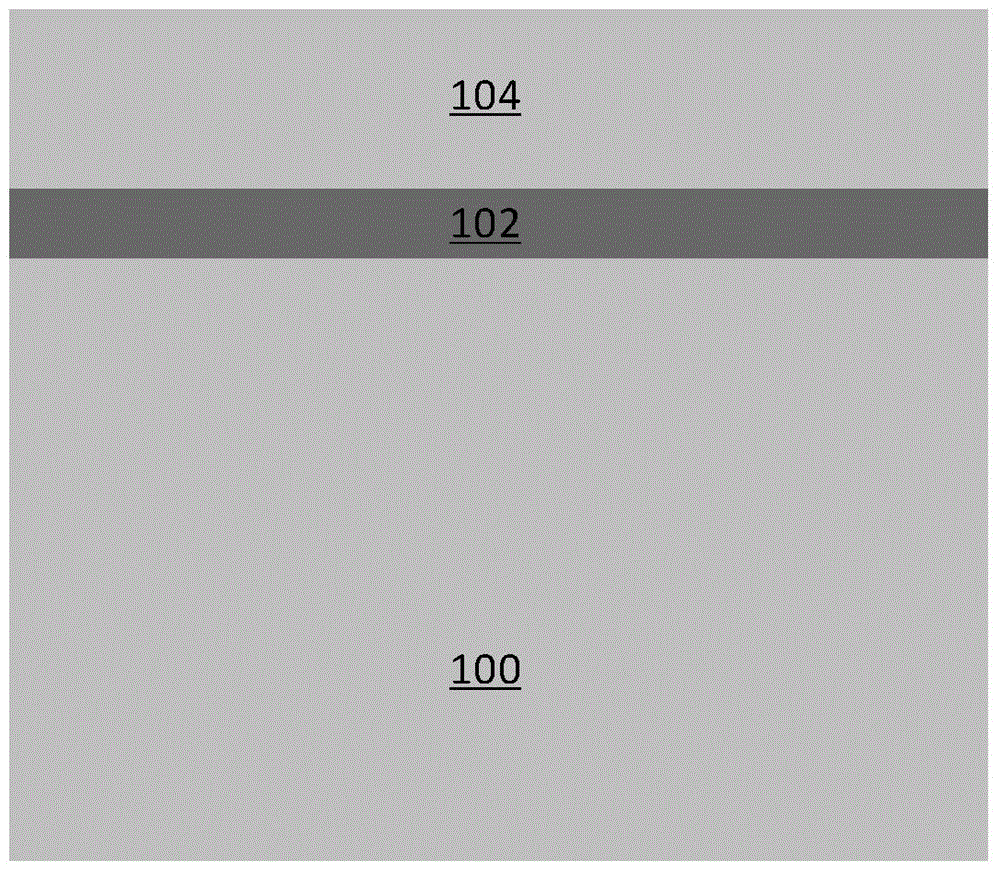

[0034] In order to make the above-mentioned objects, features and advantages of the present invention more obvious and understandable, the specific embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0035] In the following description, many specific details are explained in order to fully understand the present invention, but the present invention can also be implemented in other ways different from those described here, and those skilled in the art can do it without departing from the connotation of the present invention. Similar promotion, therefore, the present invention is not limited by the specific embodiments disclosed below.

[0036] Secondly, the present invention will be described in detail in conjunction with schematic diagrams. In detailing the embodiments of the present invention, for ease of description, the cross-sectional view showing the device structure will not be partially enlarged according to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More