SOI device structure and manufacturing method thereof

A technology of device structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as miniaturization and large structural area of unfavorable electronic products

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

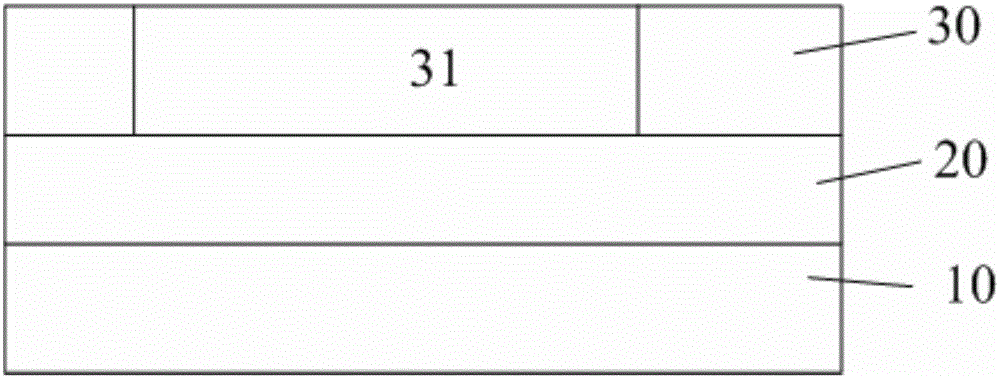

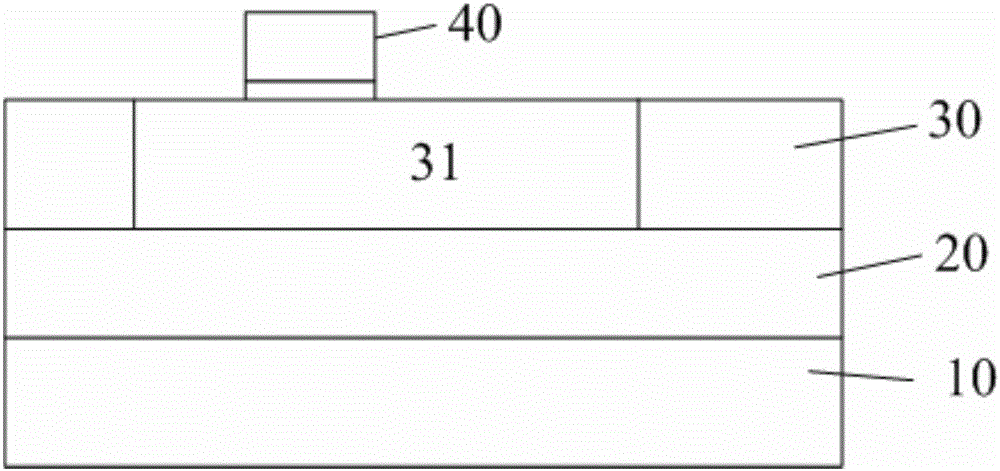

[0029] Figure 2 to Figure 8 Each step of the SOI device structure manufacturing method according to the preferred embodiment of the present invention is schematically shown.

[0030] Specifically, such as Figure 2 to Figure 8 As shown, the SOI device structure manufacturing method according to the preferred embodiment of the present invention comprises:

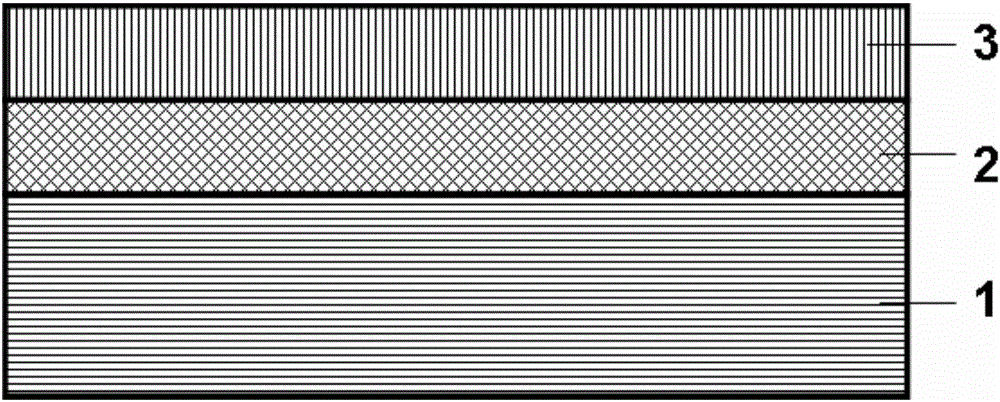

[0031] The first step: forming a silicon-on-insulator structure, the silicon-on-insulator structure includes a silicon base layer 10 as a supporting layer, a buried oxide layer 20 as an insulating layer, and a silicon top layer 31 stacked sequentially from bottom to top; and, in A device active region of the first doping type surrounded by the shallow trench isolation 30 is formed in the si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More