Multi-chip 3D stacked packaging structure with efficient heat dissipation and packaging method

A packaging structure and packaging method technology, applied in electrical components, electrical solid devices, circuits, etc., can solve problems affecting chip performance, and achieve the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

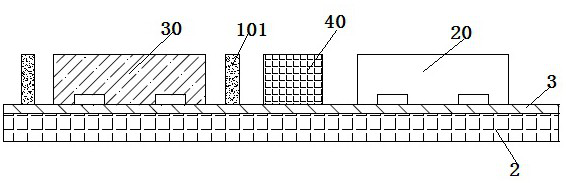

[0049] Please also refer to figure 1 , figure 1It is a structural schematic diagram of an efficient heat dissipation multi-chip 3D stack package structure according to Embodiment 1 of the present application. The highly efficient heat dissipation multi-chip 3D stack package structure includes:

[0050] redistribution layer 10;

[0051] The first chip 20, the first chip 20 is disposed on the redistribution layer 10, and is electrically connected to the redistribution layer 10;

[0052] A power device 30, the power device 30 is also disposed on the redistribution layer 10, and is electrically connected to the redistribution layer 10;

[0053] The first heat insulation element 40, the first heat insulation element 40 is located on the redistribution layer 10, and is arranged between the power device 30 and the first chip 20;

[0054] The first encapsulation layer 50, the first encapsulation layer 50 is disposed on the redistribution layer 10, and encapsulates the first chip 2...

Embodiment 2

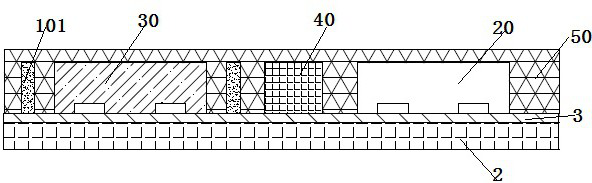

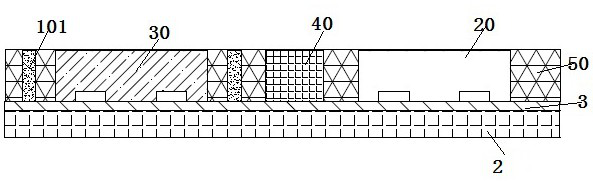

[0062] The first thermal insulation element 40 is used to thermally isolate the power device 30 from the first chip 20, so as to prevent a large amount of heat generated by the power device 30 from being transmitted laterally to the first chip 20 on the same layer, affecting its working performance, thereby shortening the The lifetime of the first chip 20 improves the reliability of the packaging structure. And in practical application, the quantity of the first chip 20 can be multiple, please refer to figure 2 as shown, figure 2 It shows a schematic cross-sectional structure of a highly efficient heat dissipation multi-chip 3D stack package structure in Embodiment 2 of the present application. In this package structure, the first heat insulating element 40 can be arranged on the power device 30 and the power device 30 Between each adjacent first chip 20, that is, it is arranged on each side of the power device 30 adjacent to the first chip 20, and even the first heat insul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More