A serial communication system

A serial communication and communication data technology, applied in the field of communication, can solve the problems of increasing hardware cost, unable to meet the requirements of bus diversification configuration, etc., and achieve the effect of improving flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

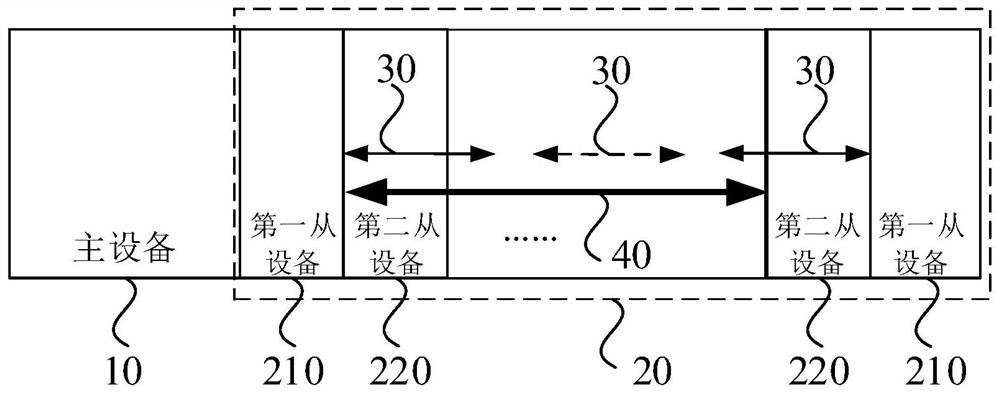

[0027] figure 2 It is a schematic diagram of a serial communication system provided by Embodiment 1 of the present invention, such as figure 2 As shown, the structure of the serial communication system includes: a master device 10 and a plurality of slave devices 20, the slave devices 20 include a first slave device 210 and a second slave device 220, each first slave device 210 and each second slave device 220 are installed according to random positions, wherein: the master device 10 and each first slave device 210 are connected for communication through a daisy-chain serial bus 30, and the daisy-chain serial bus 30 performs high-speed data transmission through a serial differential transmission mode; The master device 10 is connected to each second slave device 220 through the universal serial bus 40, and the universal serial bus 40 performs low-speed data transmission in a polling manner.

[0028] Wherein, the master device 10 may be used to send control instructions or i...

Embodiment 2

[0037] This embodiment is embodied on the basis of the foregoing embodiments. In the embodiment of the present invention, a specific implementation manner of high-speed data transmission between the master device and each first slave device is given.

[0038] Figure 4 It is a schematic structural diagram of a serial communication system applied to a high-speed bus application scenario provided by Embodiment 2 of the present invention. In order to more clearly illustrate the principle of high-speed data transmission, the structure of the serial communication system omits the second slave device. In an alternative embodiment of the present invention, as Figure 4 As shown, the processor of the master device 10 may include an LVDS interface; the processor of the first slave device 210 may use an FPGA (Field-Programmable Gate Array, Field Programmable Gate Array) chip. The processor of the master device 10 and the processors of each first slave device 210 may be connected in co...

Embodiment 3

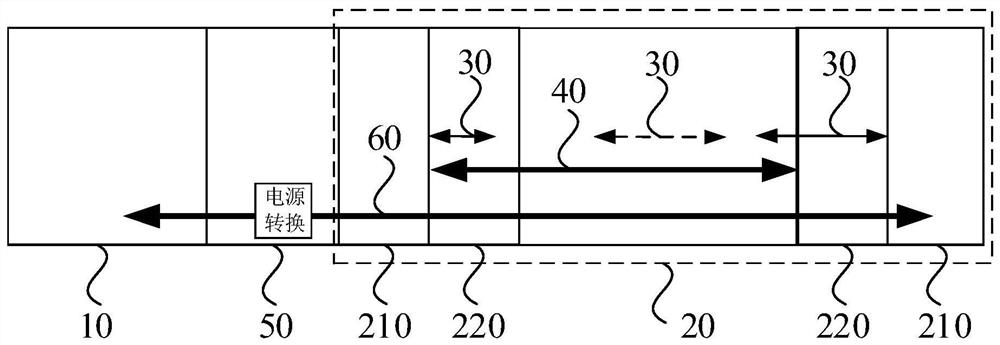

[0073] This embodiment is embodied on the basis of the foregoing embodiments. In the embodiment of the present invention, a specific implementation manner of low-speed data transmission between the master device and each second slave device is given. At the same time, a specific implementation method for the master device to perform high-speed data transmission and low-speed data transmission at the same time is given.

[0074] In the embodiment of the present invention, the master device can be used to determine the target second slave device according to the forward serial sequence of the second device, send downlink communication data to the target second slave device through the universal serial bus, and receive the target second slave device After the second slave device feeds back the uplink communication data for the downlink communication data, it updates the target second slave device according to the forward serial sequence of the second device; the target second slav...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More