Thin film transistor including oxide semiconductor layer

An oxide semiconductor and thin film transistor technology, which is applied in the manufacture of transistors, semiconductor devices, and semiconductor/solid-state devices, etc., can solve the problems of lower reliability, lower reliability, and threshold voltage deviation of display devices, and achieve high field effect mobility. , The effect of excellent light stress resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0086]

[0087] [Manufacturing of Thin Film Transistors]

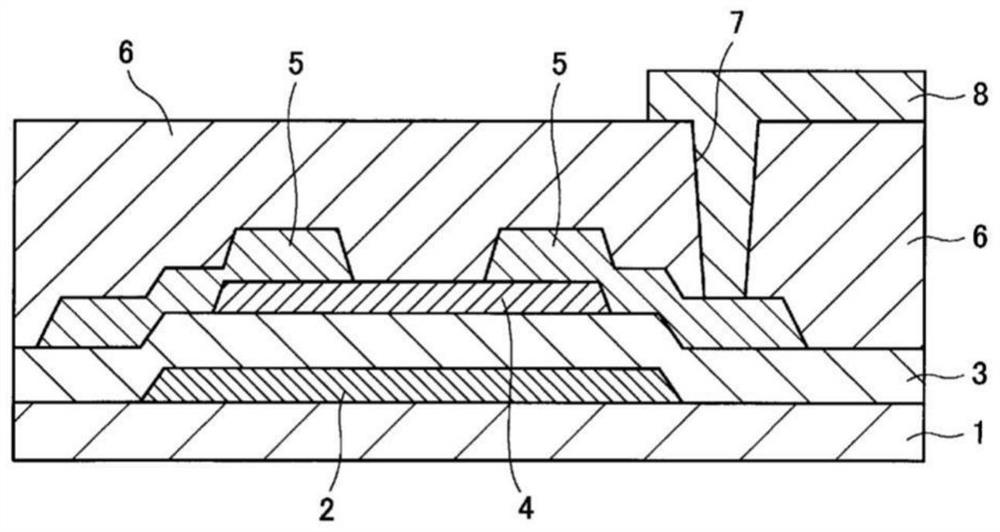

[0088] refer to figure 1 , the manufacturing method of the thin film transistor is shown below. On a glass substrate 1 (manufactured by Eagle, trade name Eagle 2000, 4 inches in diameter, 0.7 mm in thickness), a Mo film was formed to a thickness of 250 nm as a gate electrode. 2, and on it, use the plasma CVD method to form a film of silicon oxide (SiO x ) film as the gate insulating film 3.

[0089] Carrier gas: SiH 4 with N 2 Mixed gas of O

[0090] Film forming power density: 0.96W / cm 2

[0091] Film forming temperature: 320°C

[0092] Air pressure during film formation: 133Pa

[0093] Next, the oxide semiconductor layer 4 which is an In-Ga-Zn-Sn-O film described in Table 1 was formed with a film thickness of 40 nm under the following conditions.

[0094] (Oxide semiconductor layer formation)

[0095] Film formation method: DC (direct-current, DC) sputtering method

[0096] Device: CS200 manufactured by...

Embodiment 2

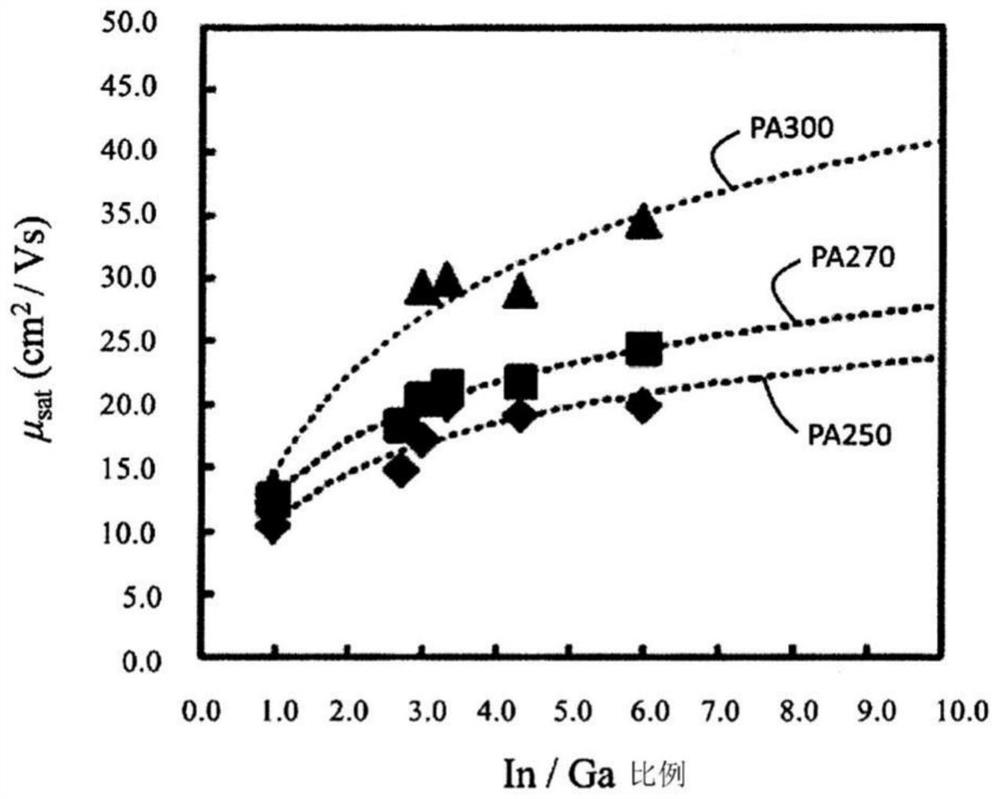

[0148] [The difference in post-annealing temperature vs. ΔV th Impact]

[0149] The stress tolerance (ΔV th @NBTIS) for comparison. The conditions of the stress application experiment were the same as described above.

[0150] Figure 4 It shows the I of the ESL-TFT (thin film transistor) using the No. 3 oxide semiconductor layer when the post-annealing is performed at 250°C and when the post-annealing is performed at 300°C. d -V g characteristic chart. Furthermore, Figure 4 In , "PA250" indicates the case where the post-annealing was performed at 250°C, and "PA300" indicates the case where the post-annealing was performed at 300°C. According to the I d -V g characteristics to calculate the field-effect mobility (μ sat ), threshold voltage offset (V th ), subthreshold coefficient (subthreshold, SS) and on-current (I on ).

[0151] (in the case of post-annealing at 250°C)

[0152] Field Effect Mobility (μ sat ): 19.94cm 2 / Vs

[0153] Threshold Voltage Offset ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More