Excitation generation method for SOC system-level verification environment

A verification environment, system-level technology, applied in CAD circuit design, special data processing applications, etc., to achieve a wide range of applications, reduce integration time, and speed up the progress of SOC verification.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056]The present invention will be further described in detail below with reference to the drawings and specific embodiments of the specification.

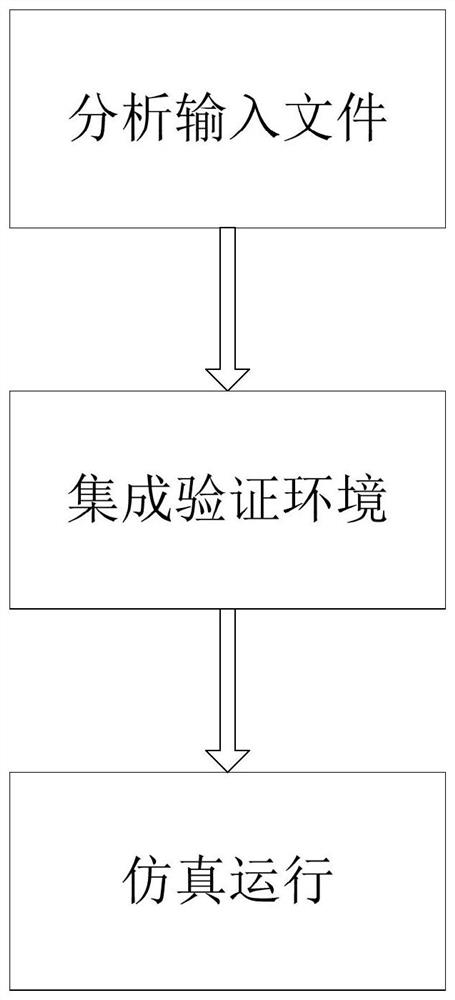

[0057]Such asfigure 1 As shown, the method for generating an SOC system-level verification environment of the present invention includes:

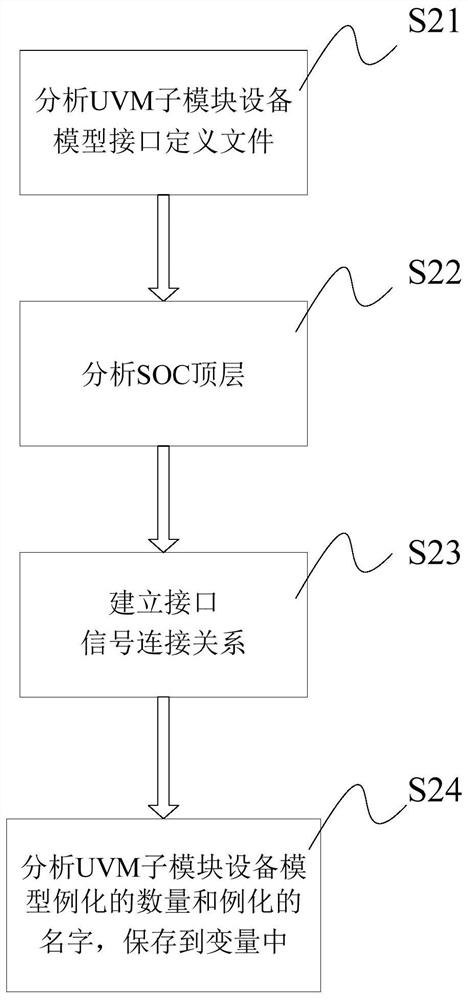

[0058]Step S1: Analyze the input file; analyze the sub-module device model UVM interface and the top level of the SOC system-level verification environment, and establish the connection relationship between the sub-module device model UVM interface and the top-level signal interface of the SOC system-level verification environment;

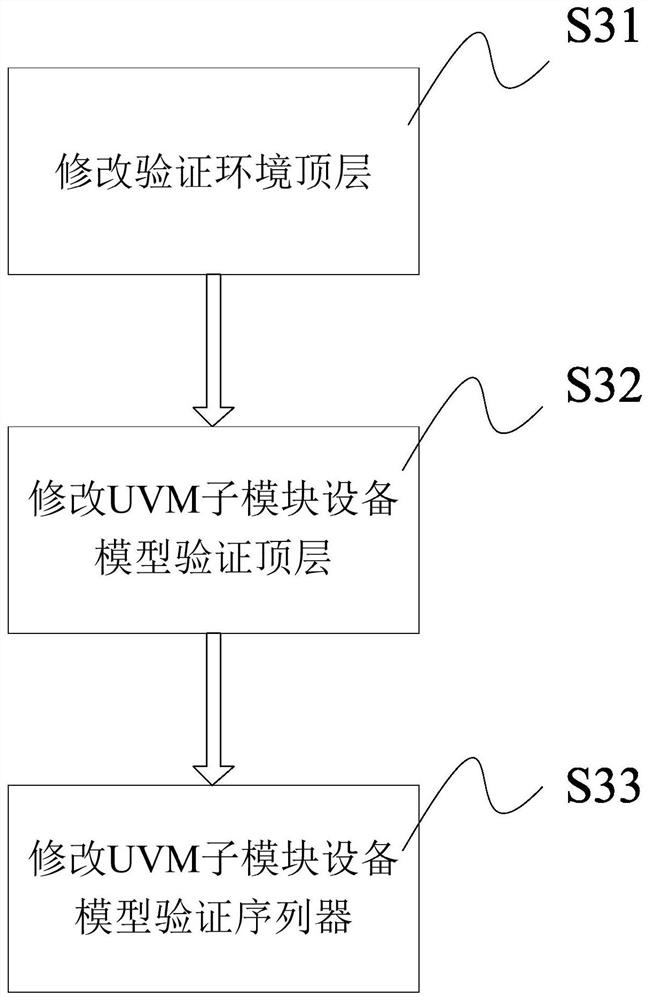

[0059]Step S2: Establish an integrated verification environment; enable the UVM environment of the sub-module equipment model to be quickly integrated into the SOC system-level verification environment;

[0060]Step S3: The simulation runs, and the analysis result is finished.

[0061]Through the above method of the present invention, the verification engineer does not need to be fam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More