A processor replay debugging method and system

A processor and replay technology, applied in the direction of detecting faulty computer hardware, etc., can solve the problems of slow waveform recording of hardware emulation accelerators, affecting the simulation speed, and long debugging cycle, so as to speed up the chip verification process, speed up the verification process, The effect of improving the efficiency of software debugging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is only some embodiments of the present invention, but not all embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

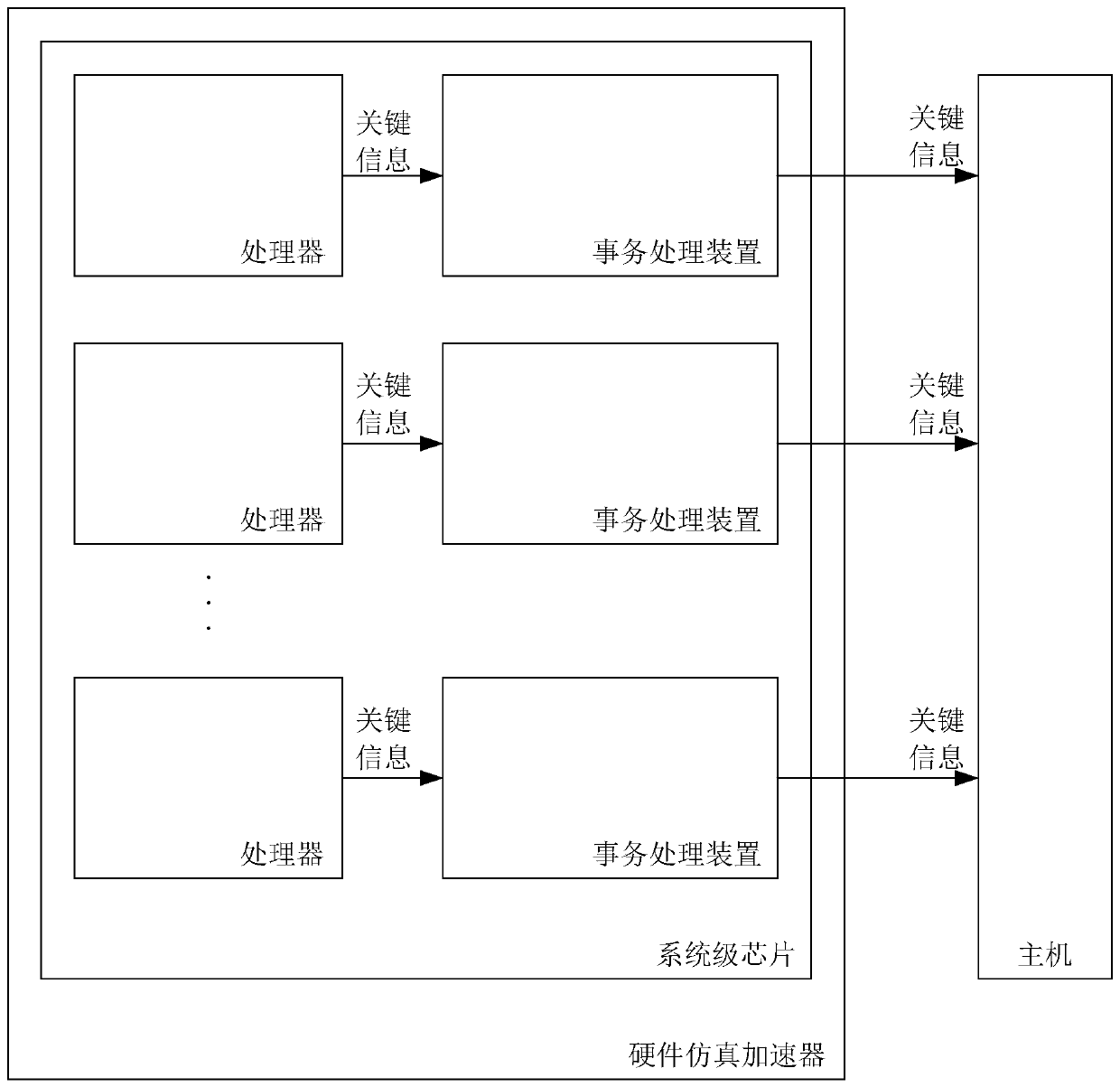

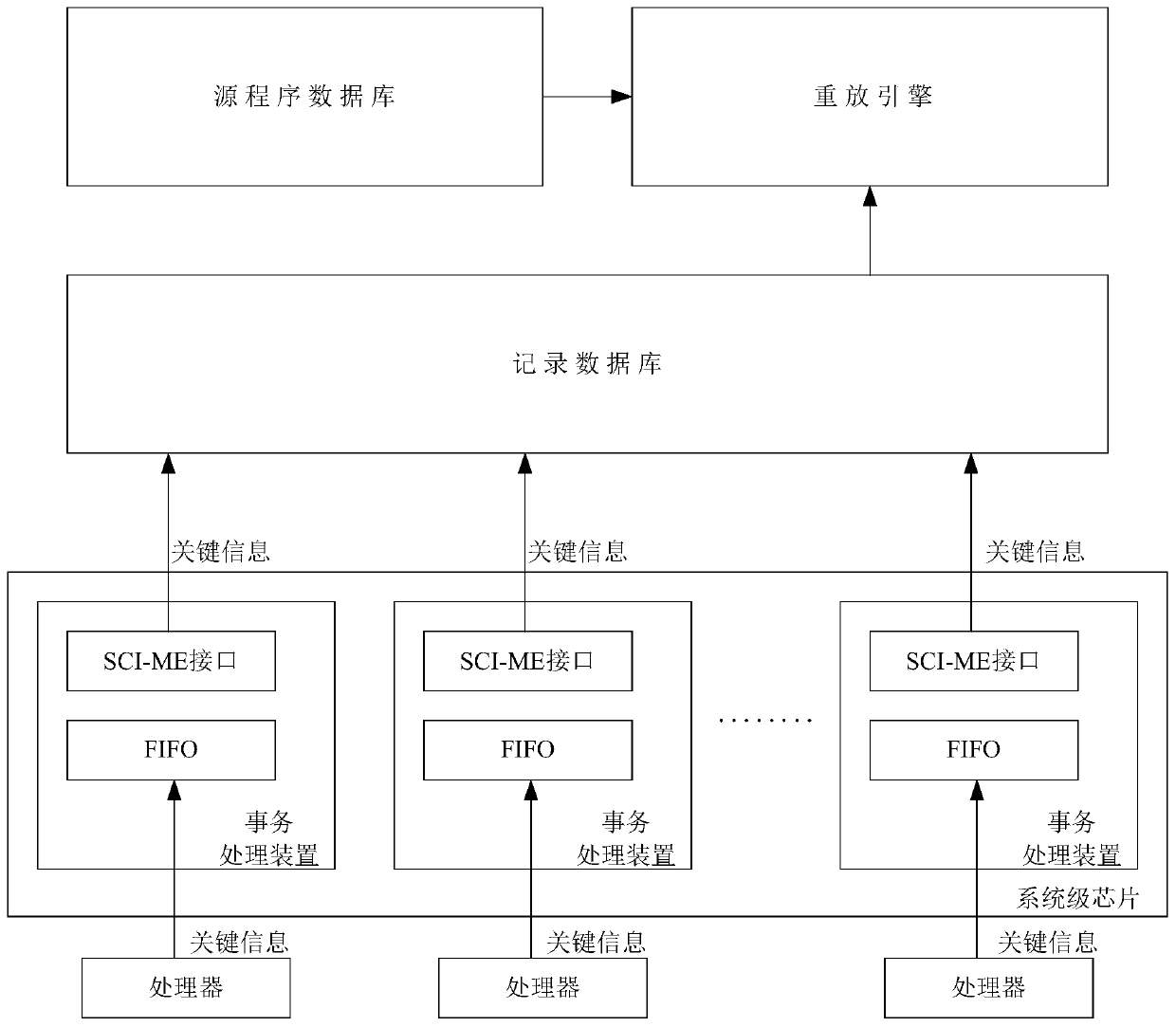

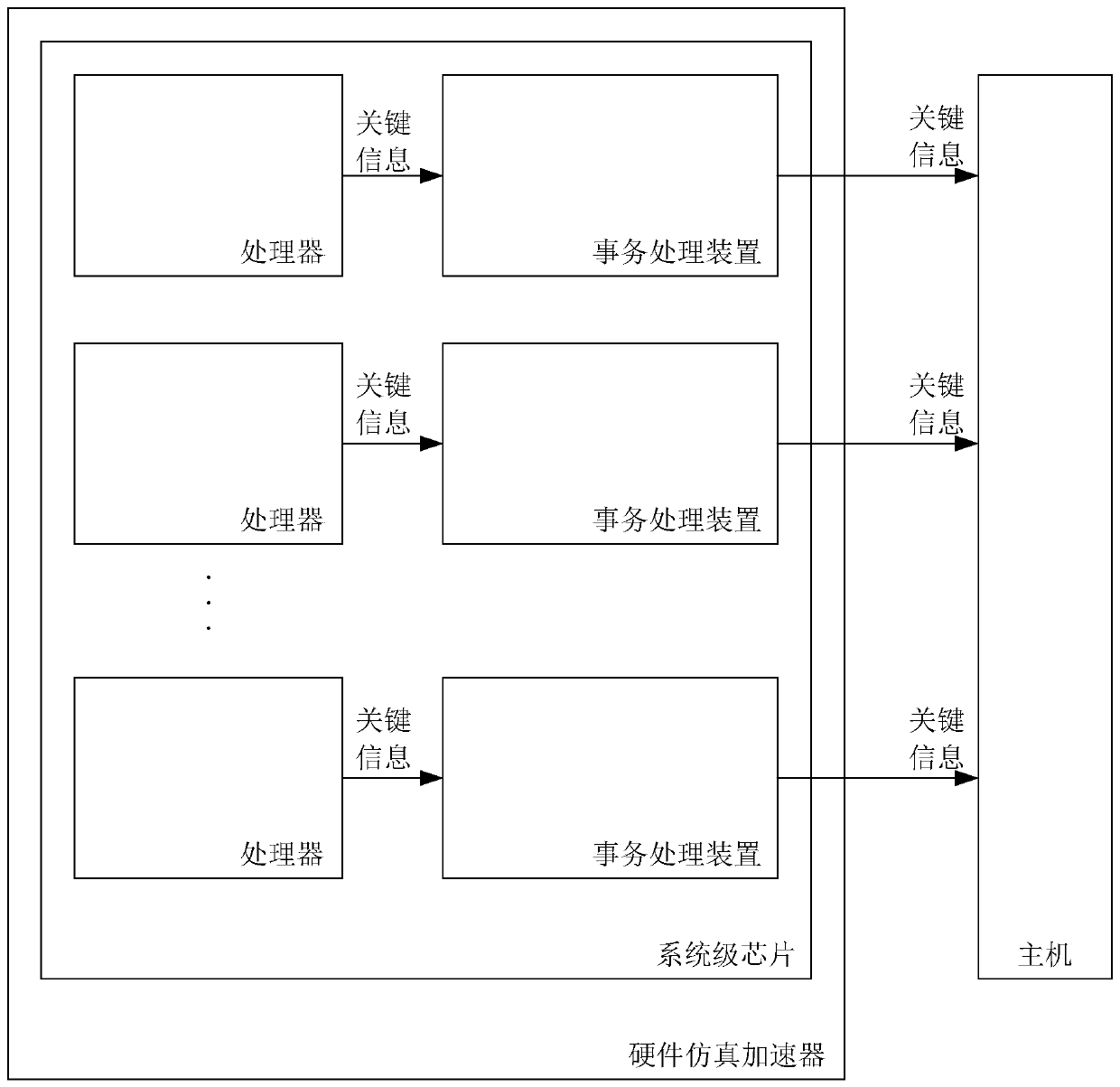

[0015] The present invention provides a processor replay debugging system, which is applied to hardware emulation accelerators, such as figure 1 As shown, the system includes a system-on-a-chip including at least one processor and at least one transaction processing device corresponding to the at least one processor arranged on the host compu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More