Gated clock conversion method based on recursive multi-way tree

A technology of gating clocks and conversion methods, which is applied in the directions of instruments, calculations, and electrical digital data processing, etc., and can solve problems such as clock cycle constraint violations, increased tool flow time, and unsatisfactory circuit optimization effects, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments, but these embodiments should not be construed as limiting the present invention.

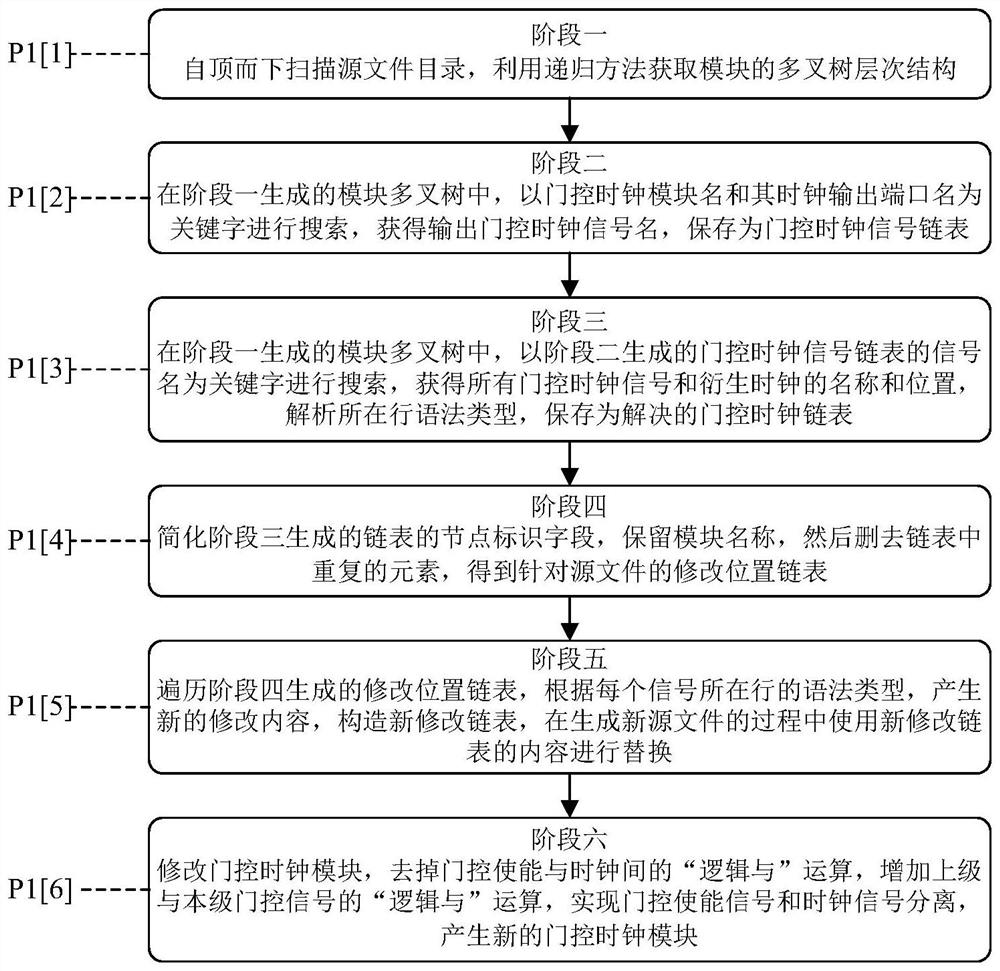

[0036] The present invention conceives a recursive multi-fork tree method for the purpose of converting the register description-level gating clock, which can realize the rapid replacement of the gating clock structure and save the time and energy of logic verification personnel. The overall flow diagram of the present invention is as figure 1 As shown, this is a phased implementation process, and the phased implementation process can be implemented using computer software programming languages, such as C / C++, java, python, and the like.

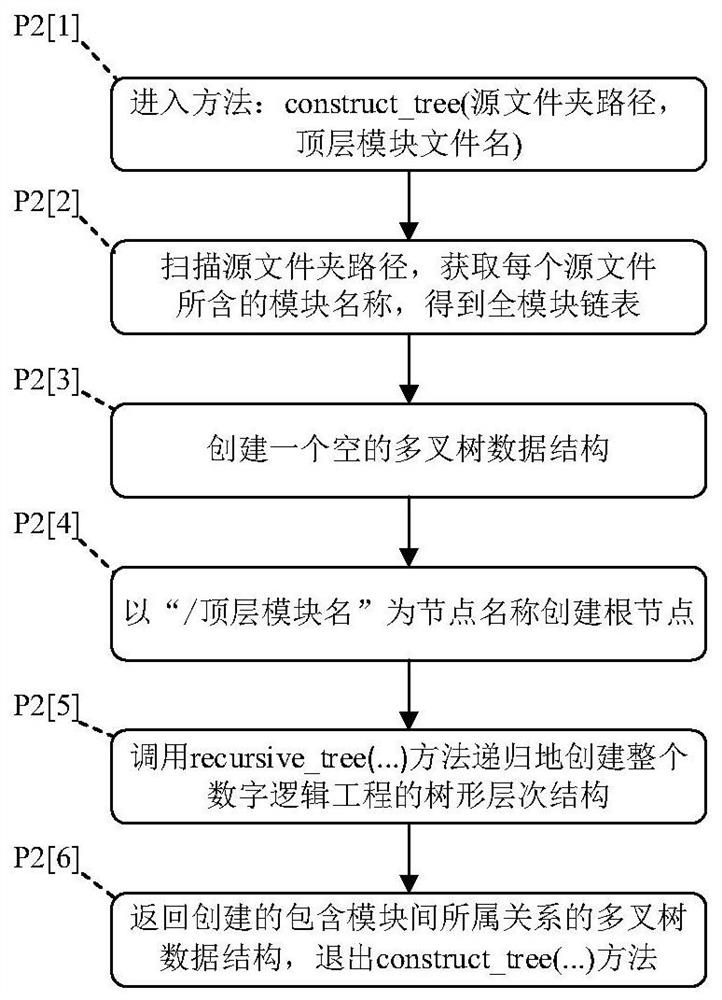

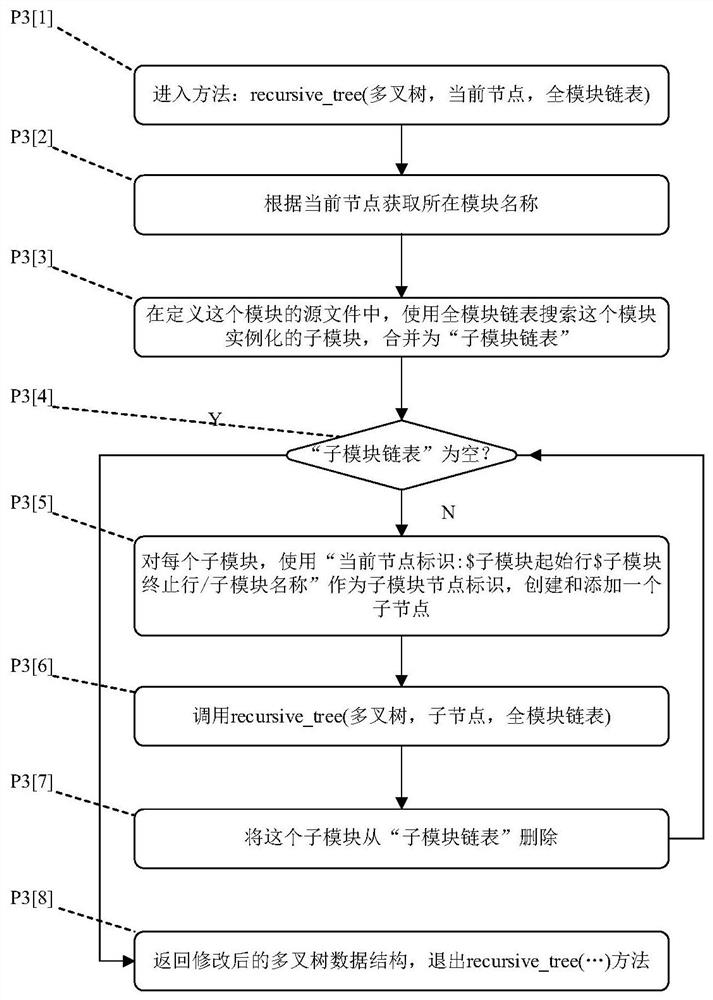

[0037] Considering the progressive relationship between the stages, the next step is to explain the workflow of each stage. The staged process is as follows (the number after the letter P represents the serial number of the pict...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More