Patents

Literature

47results about How to "Fix timing issues" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Industrial intelligent camera based on FPGA

InactiveCN104284065AGood technical effectAvoid interaction designTelevision system detailsColor television detailsCMOSInteractive design

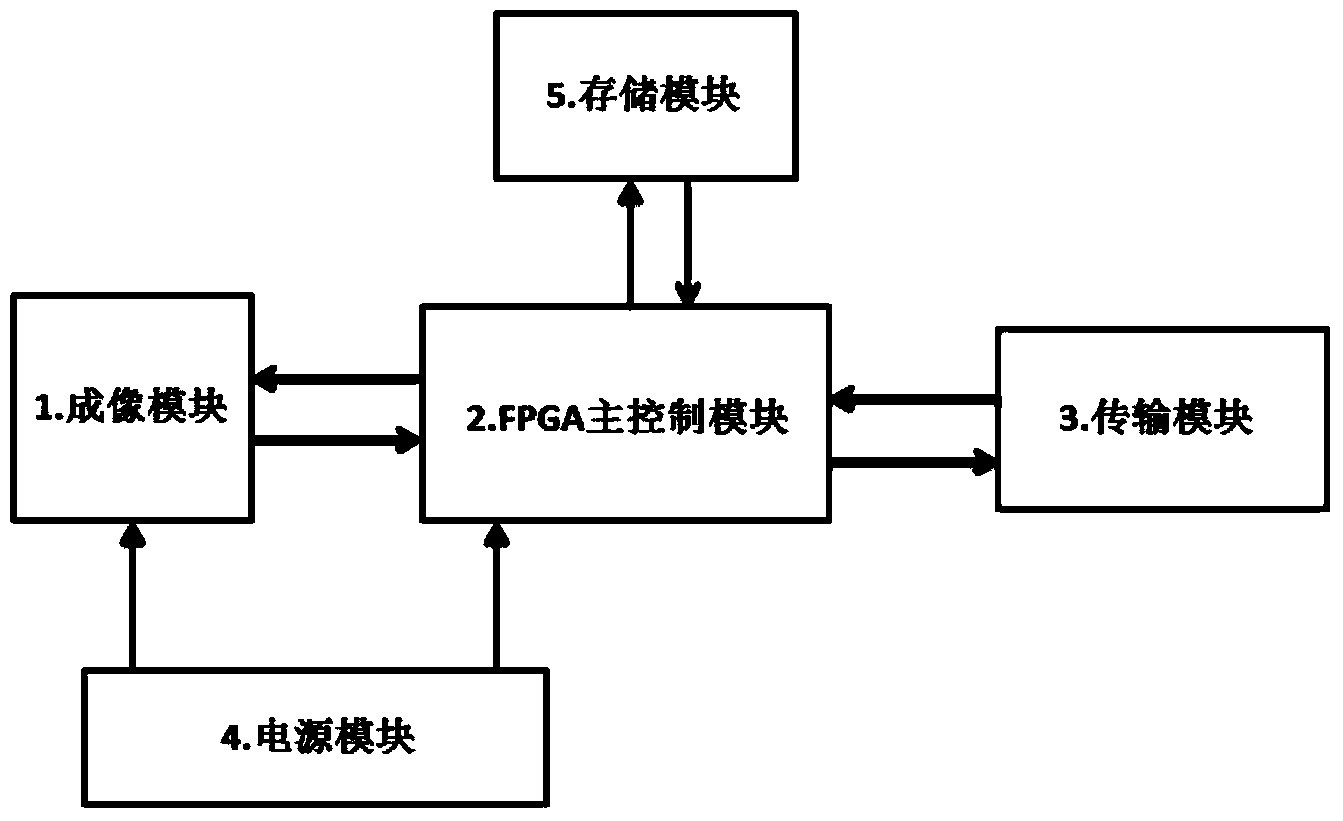

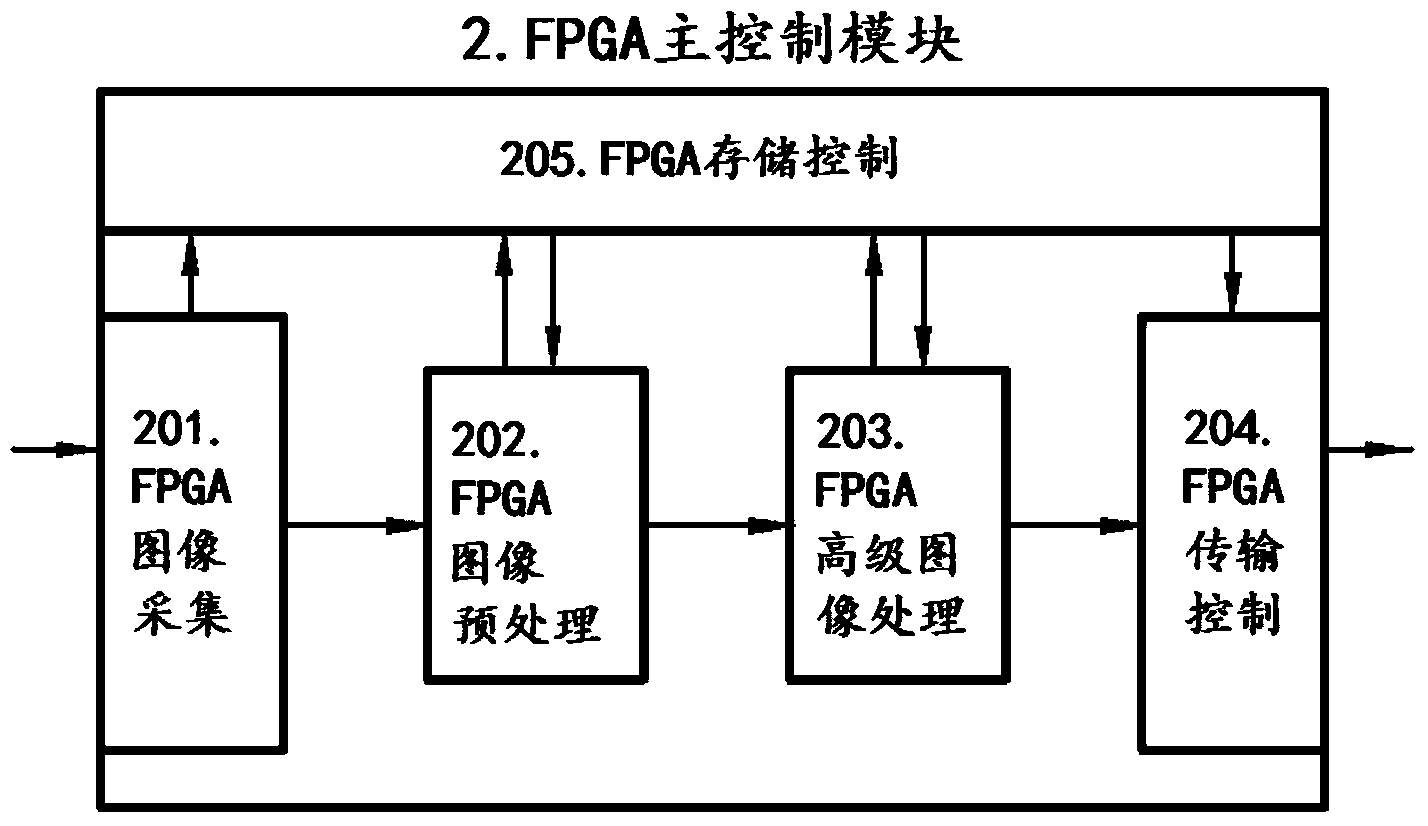

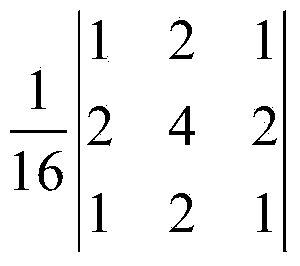

The invention provides an industrial intelligent camera which comprises an imaging module, a master control module, a transmission module, a power module and a storage module. The imaging module comprises a CMOS image sensor and a peripheral circuit; the master control module is an FPGA chip and comprises an image collecting control module, an image pre-processing module, an image advanced processing module, a transmission control module and a storage control module. According to the industrial intelligent camera, all image processing functions are achieved through the FPGA chip, the complex interactive design of an FPGA and a DSP is avoided, and the advantages that algorithms of the FPGA is achieved through a hardware circuit, so that the processing speed is high, and performance is stable are sufficiently played; the industrial intelligent camera is high in integration degree, small in overall size, small in weight, less in power dissipation and particularly suitable for application occasions with high requirements for the camera size and the image processing speed.

Owner:HUAZHONG UNIV OF SCI & TECH +1

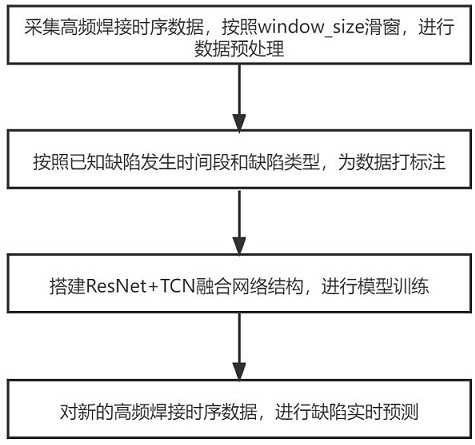

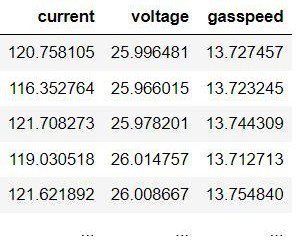

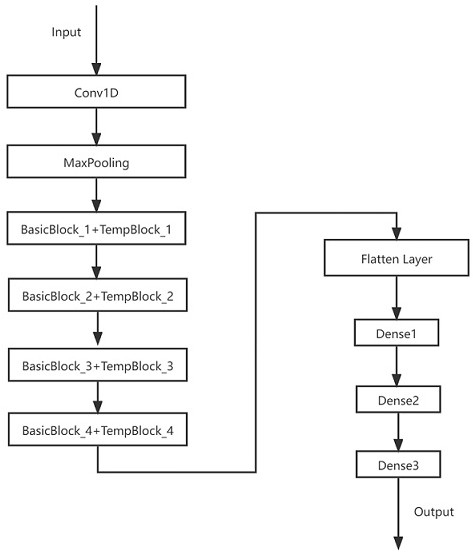

Welding defect real-time detection method and system based on high-frequency time sequence data

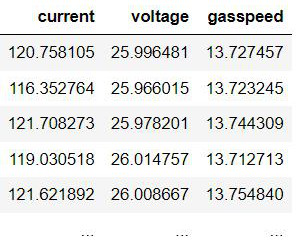

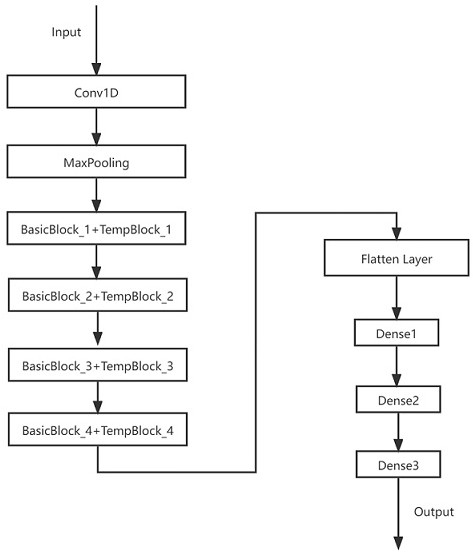

ActiveCN113870260AFix timing issuesIncrease training speedImage enhancementImage analysisNetwork structureNetwork model

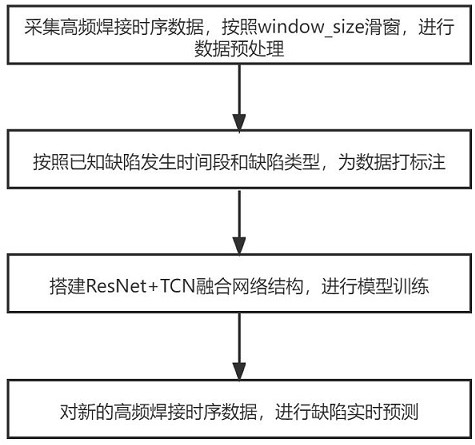

The invention discloses a welding defect real-time detection method and system based on high-frequency time sequence data. The detection method comprises the steps of firstly sampling the collected high-frequency welding time sequence data according to a set window length, marking a defect occurrence time period and a defect type for each sample, and generating a data sample set; training a ResNet and TCN fusion network model by using the generated data sample set to obtain a trained detection model; and finally, obtaining new real-time high-frequency welding data, inputting the new real-time high-frequency welding data into the trained detection model for prediction according to a set window length, and outputting a welding defect category in real time. According to the method, the ResNet network and the TCN are subjected to network structure fusion, the ResNet can be applied to the field of time sequence detection, and for high-frequency welding time sequence data with a large data size and a long sequence length, the training speed is increased in the training process through a parallel convolution calculation mode, and strong real-time prediction is achieved in the prediction process.

Owner:苏芯物联技术(南京)有限公司

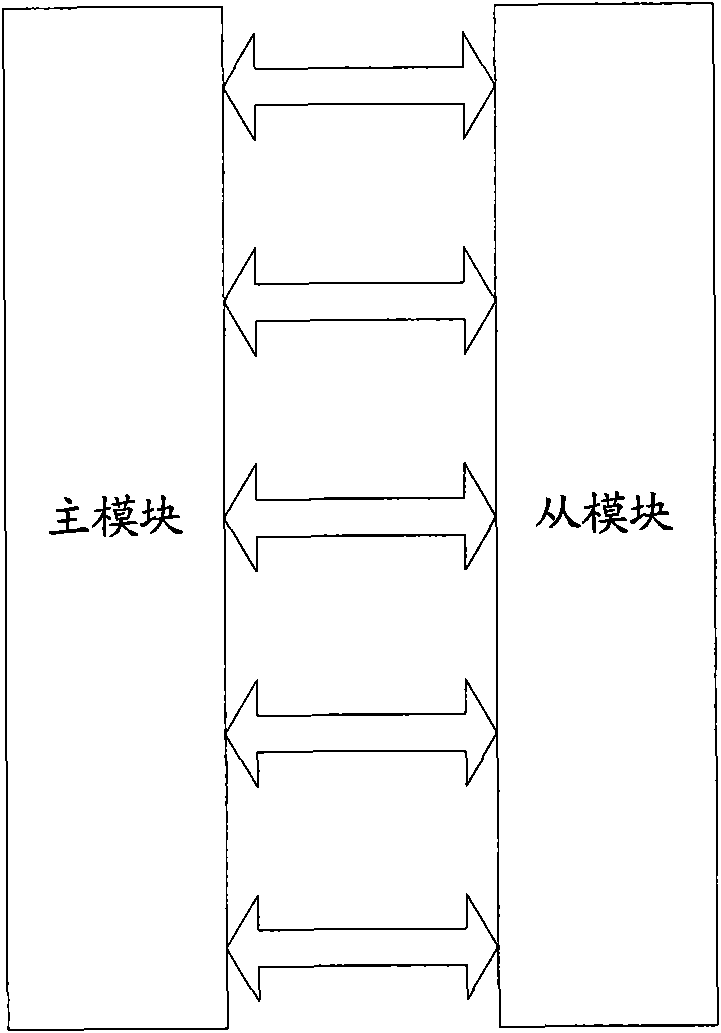

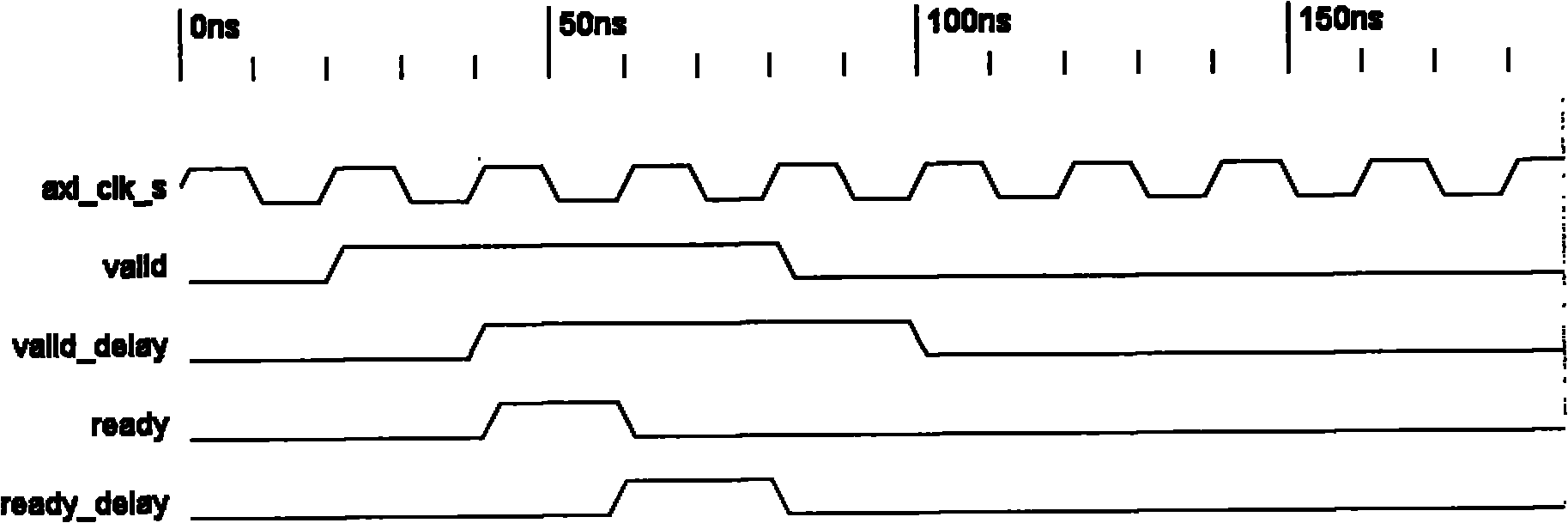

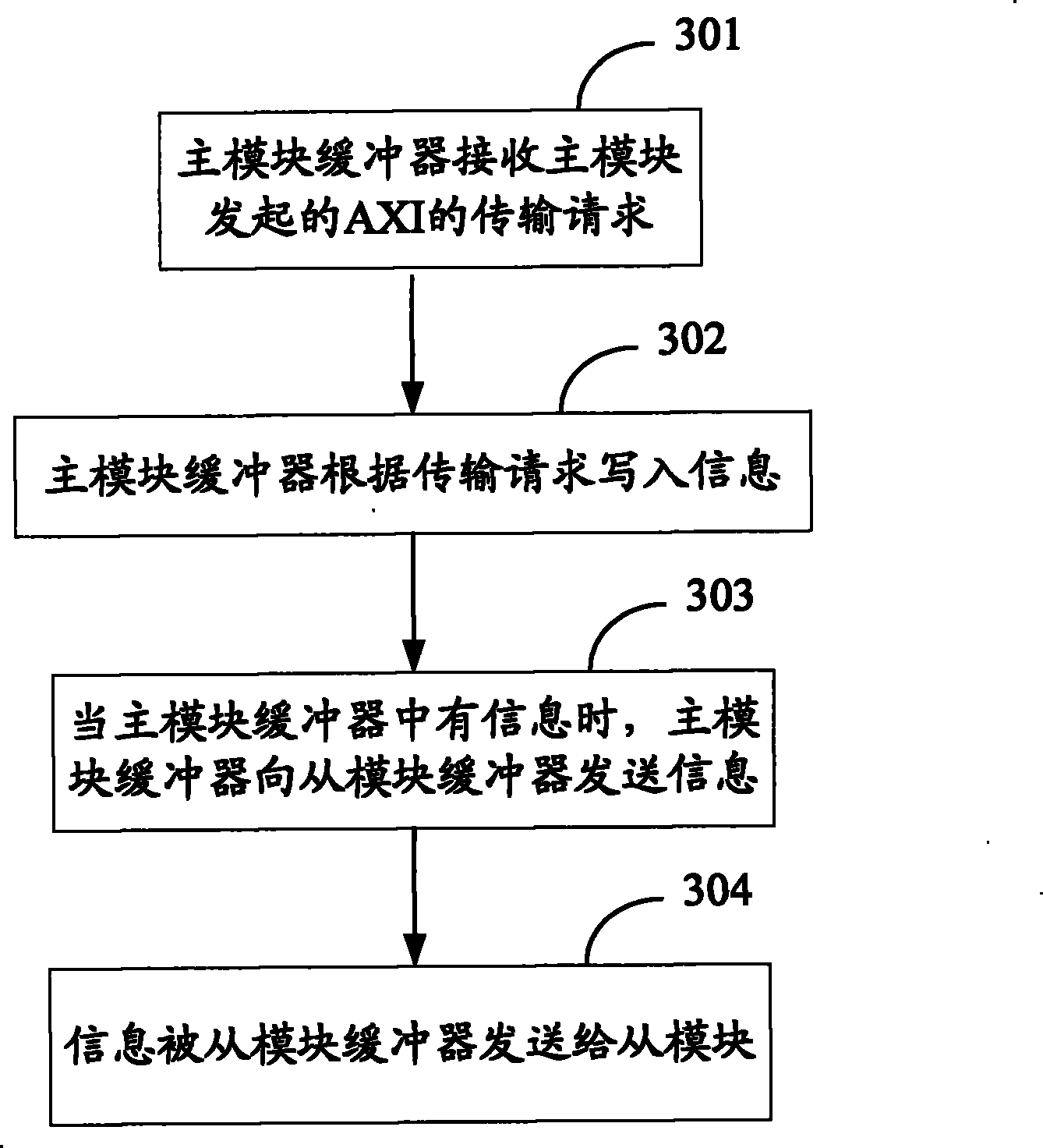

Method and system for realizing bus connection

InactiveCN102103564AGuaranteed timing optimizationAvoid timing issuesElectric digital data processingEmbedded systemData buffer

The invention discloses a method and a system for realizing bus connection. The method comprises the following steps that: a main module buffer receives a transmission request, initiated by a main module, of an advanced expandable interface bus; the main module buffer writes information according to the transmission request; when the main module buffer has the information, the main module buffer transmits the information to a slave module buffer; and the information is transmitted buffer to a slave module by the slave module. By the method and the system for realizing the bus connection, which is provided by the invention, as the main module buffer and the slave module buffer are adopted between the main module and the slave module, the signal input / output between the main module and the slave module is connected with a register, and the time sequence optimization of the bus connection can be guaranteed to the maximum extent.

Owner:ZTE CORP +1

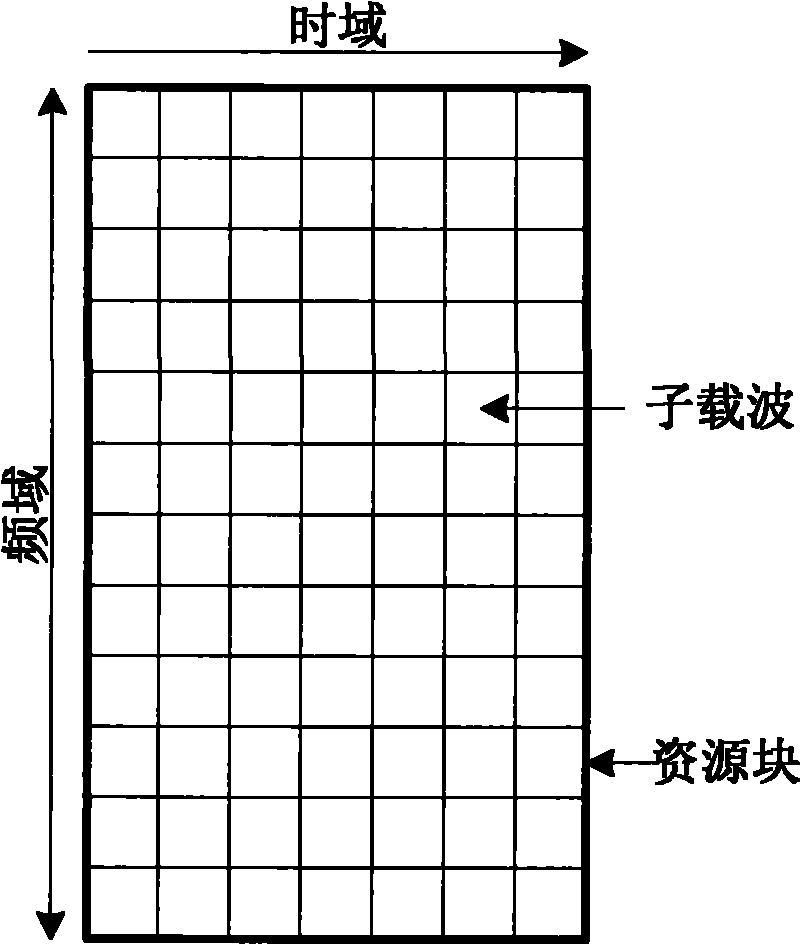

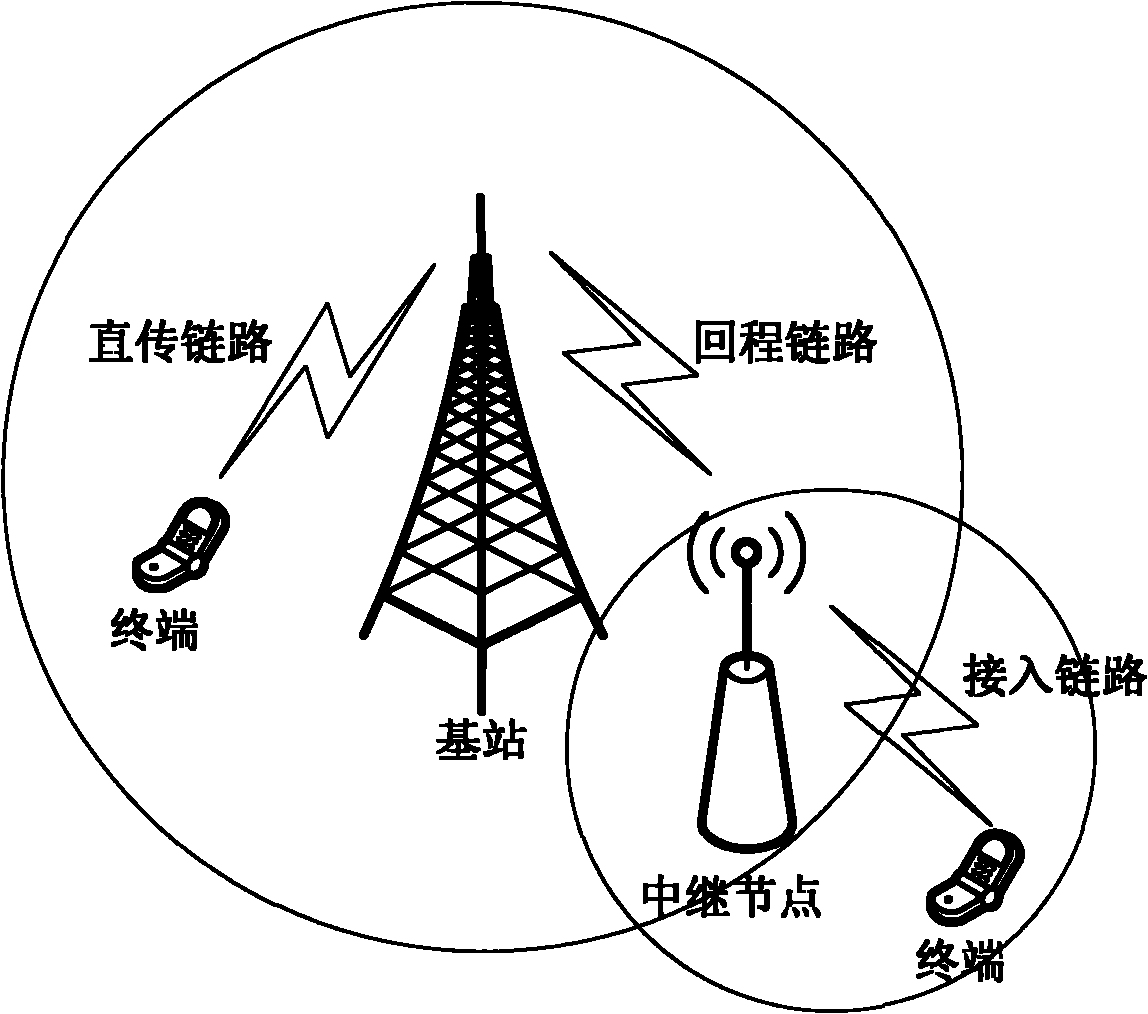

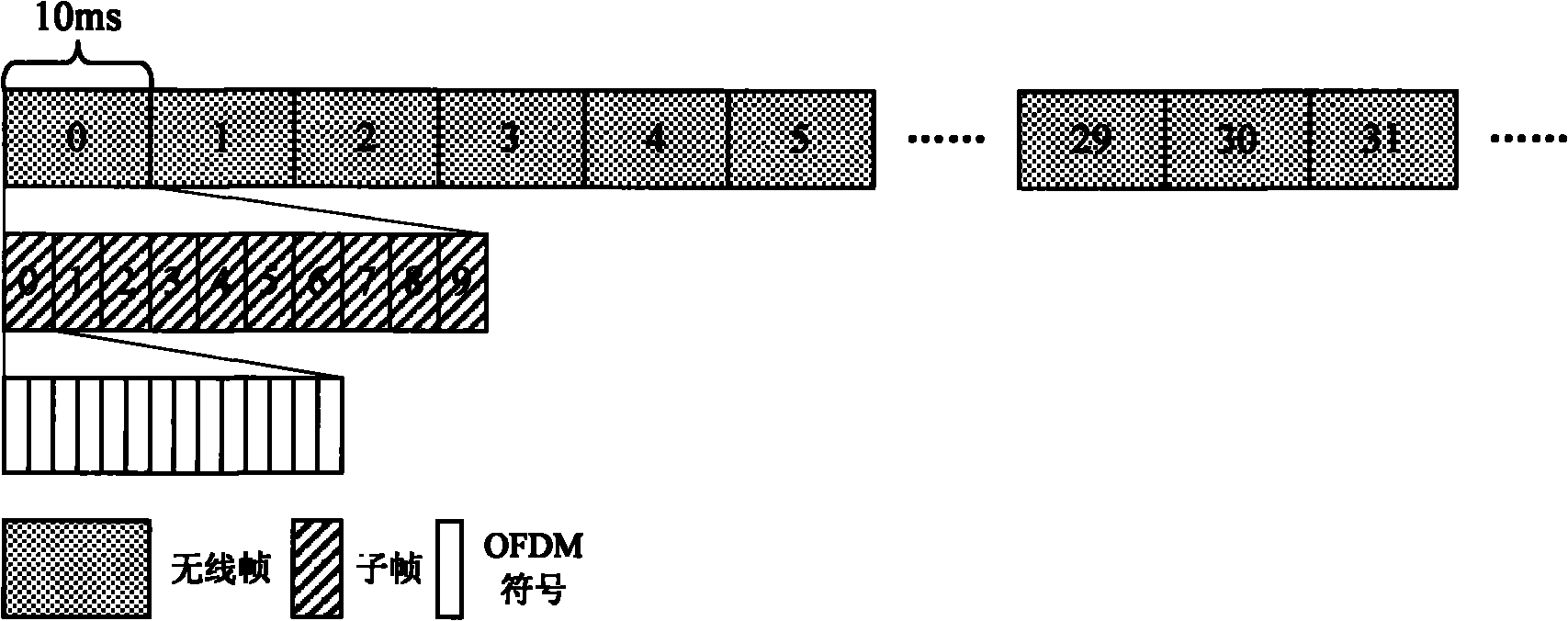

Method and system for timing subframe

InactiveCN102055518ANo overheadFix timing issuesSynchronisation arrangementRadio transmission for post communicationCommunications systemBackward compatibility

The invention discloses a method and a system for timing a subframe, applied to a communication system adopting a relay node. The method comprises the steps of: timing an uplink return link subframe at a relay node side according to a downlink return link subframe of the relay node side, determining timing quantity by using a time advance command (TAC) sent by a base station; and when the relay node sends an uplink signal to the base station, sending the advanced timing quantity according to the initial time of the downlink return link subframe of the relay node side. According to the technical scheme provided by the invention, the invention can be better suitable for a link between the relay node and the base station and is flexible in a timing mode without increasing the signaling overhead, thereby ensuring the backward compatibility and solving the problem of timing of the relay subframe and an access subframe.

Owner:ZTE CORP

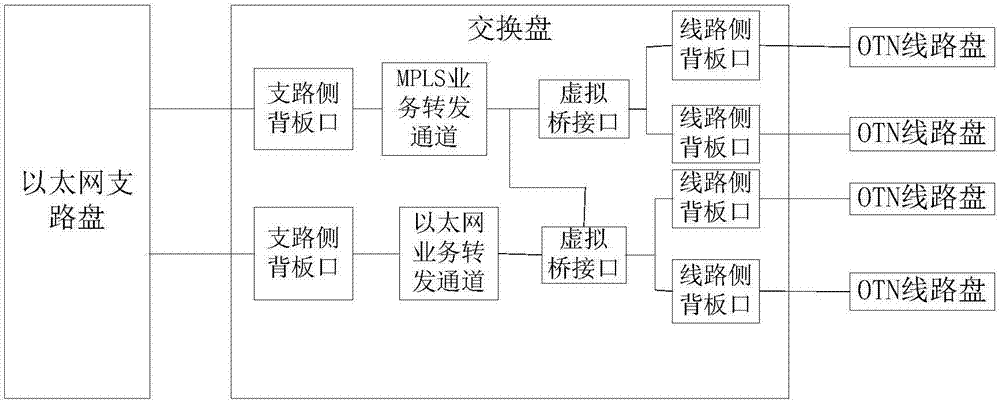

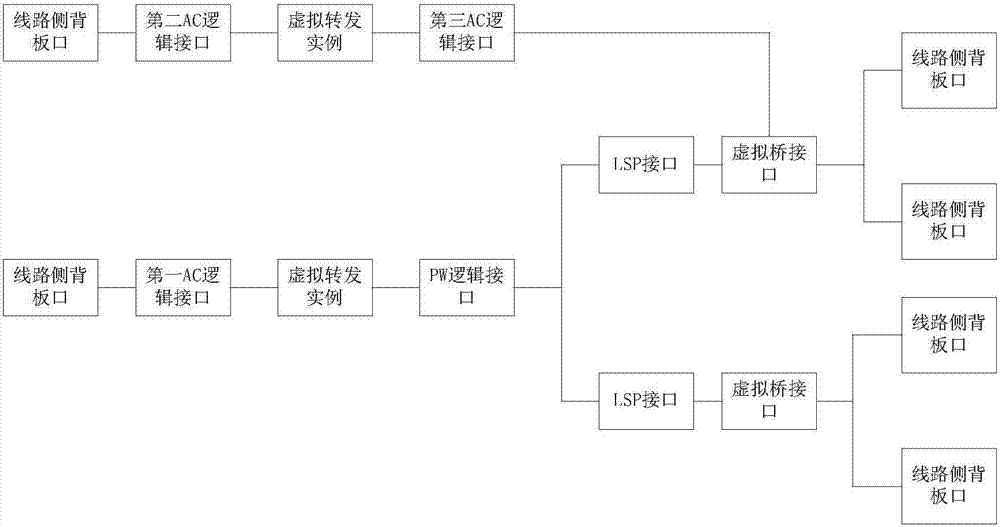

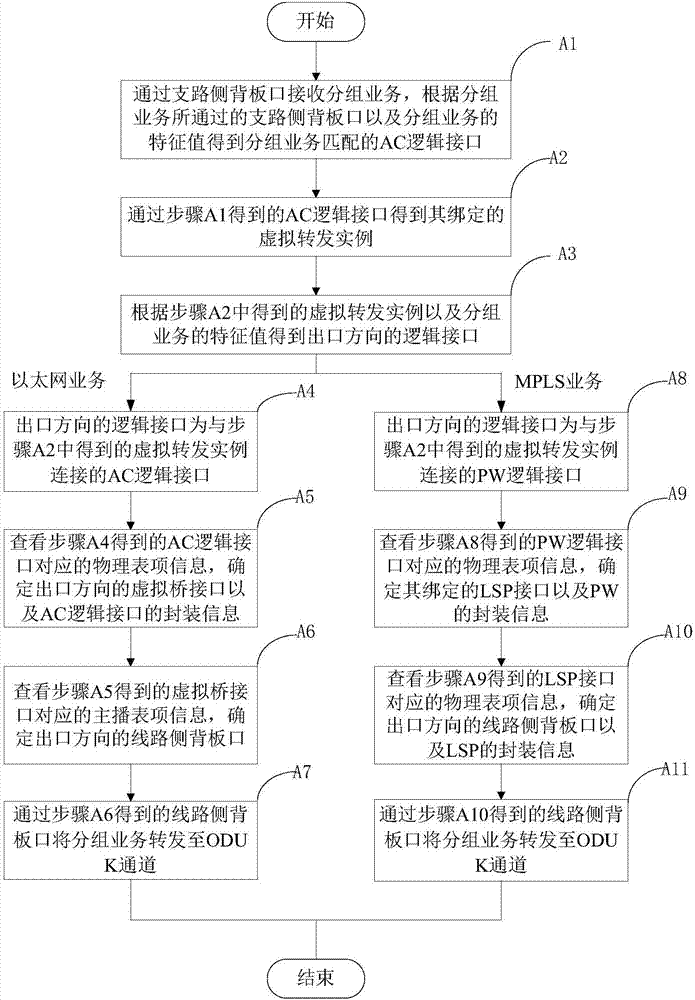

POTN service forwarding system and service forwarding, configuration issuing and protection methods

ActiveCN107135154AFix timing issuesRealize configuration decouplingMultiplex system selection arrangementsTime-division multiplexEthernetBackplane

The invention discloses a POTN service forwarding system and a forwarding method and relates to the technical field of POTN transmission. The system comprises an Ethernet branch disk, a switch disk and OTN line disks. POVE is instantiated to multicast in an up direction to realize bridging, packet services take the multicast as an outlet of an up direction service channel, and an OTN service takes the multicast as a source port interacting with an ODUK channel; the POVE is instantiated to VLANDOMAIN in a down direction to realize bridging, the OTN service maps a line side back plate port connected to the ODUK channel to the VLANDOMAIN, and the packet services take the VLANDOMAIN as a common physical port to complete classification processing of the packet services. The invention also discloses a POTN service forwarding method.

Owner:武汉光网信息技术有限公司

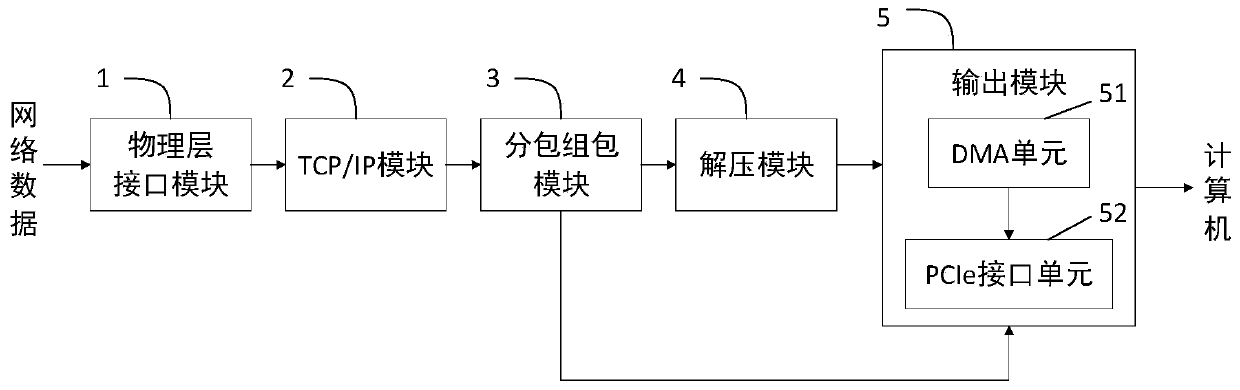

Data decompression device and method based on FPGA

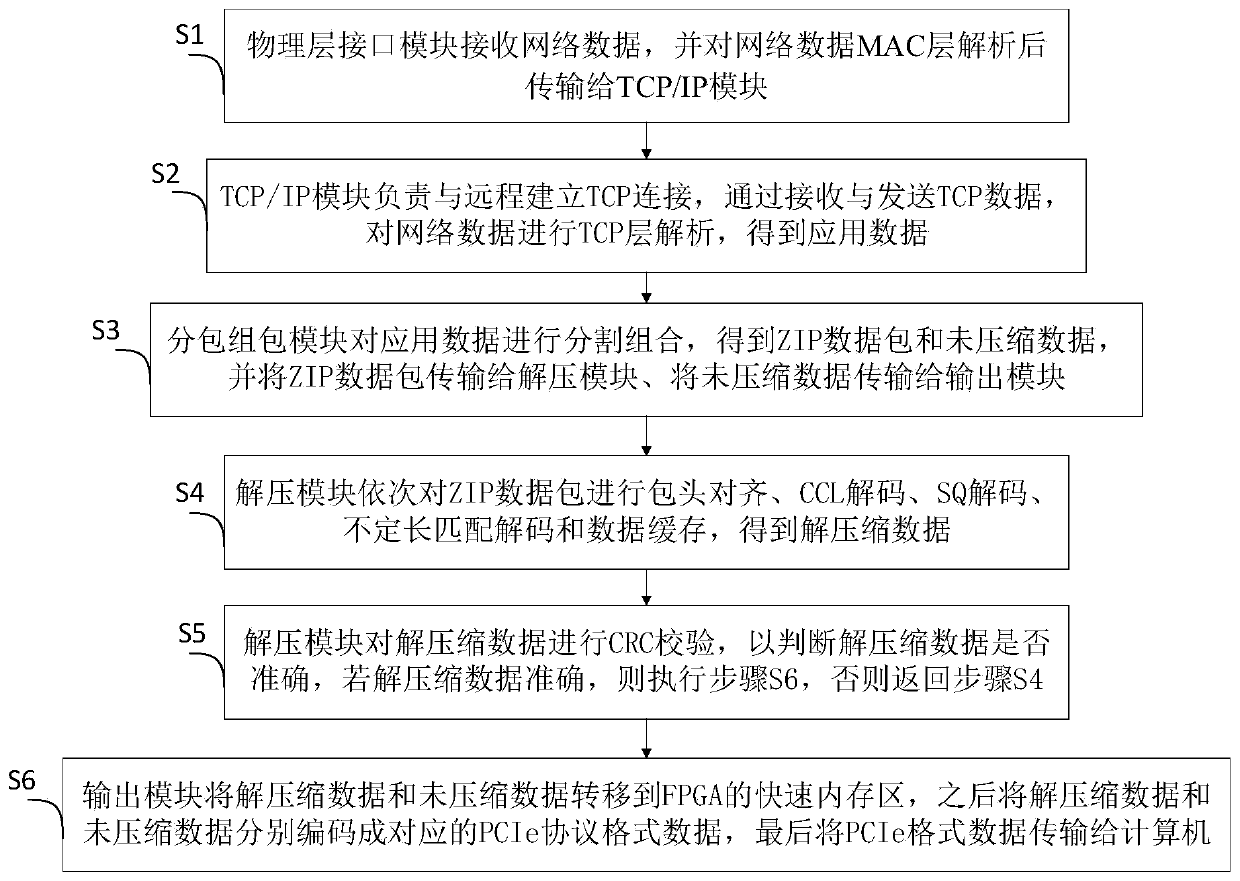

ActiveCN110620637AReduce resource usageReduce receiving delayAdaptation strategy characterisationOccupancy ratePhysical layer

The invention relates to a data decompression device and method based on an FPGA. The data decompression device comprises a physical layer interface module, a TCP / IP (Transmission Control Protocol / Internet Protocol) module, a sub-packaging module, a decompression module and an output module which are connected in sequence, the sub-packaging module is further directly connected with the output module, and the physical layer interface module is used for receiving network data, performing MAC layer analysis on the network data and then transmitting the network data to the TCP / IP module; the TCP / IP module is used for performing TCP analysis on the network data to obtain application data; the subpackaging module is used for segmenting and combining the application data to obtain a ZIP data packet and uncompressed data; the decompression module is used for decompressing the ZIP data packet to obtain decompressed data; and the output module transmits the decompressed data and the uncompresseddata to a computer. Compared with the prior art, the data decompression based on the FPGA can effectively replace a software decompression method, the CPU occupancy rate is reduced, the data delay isreduced, the data throughput is improved, and the purpose of quickly and accurately decompressing the data is achieved.

Owner:上海仪电(集团)有限公司中央研究院

Time sequence error correction system and method

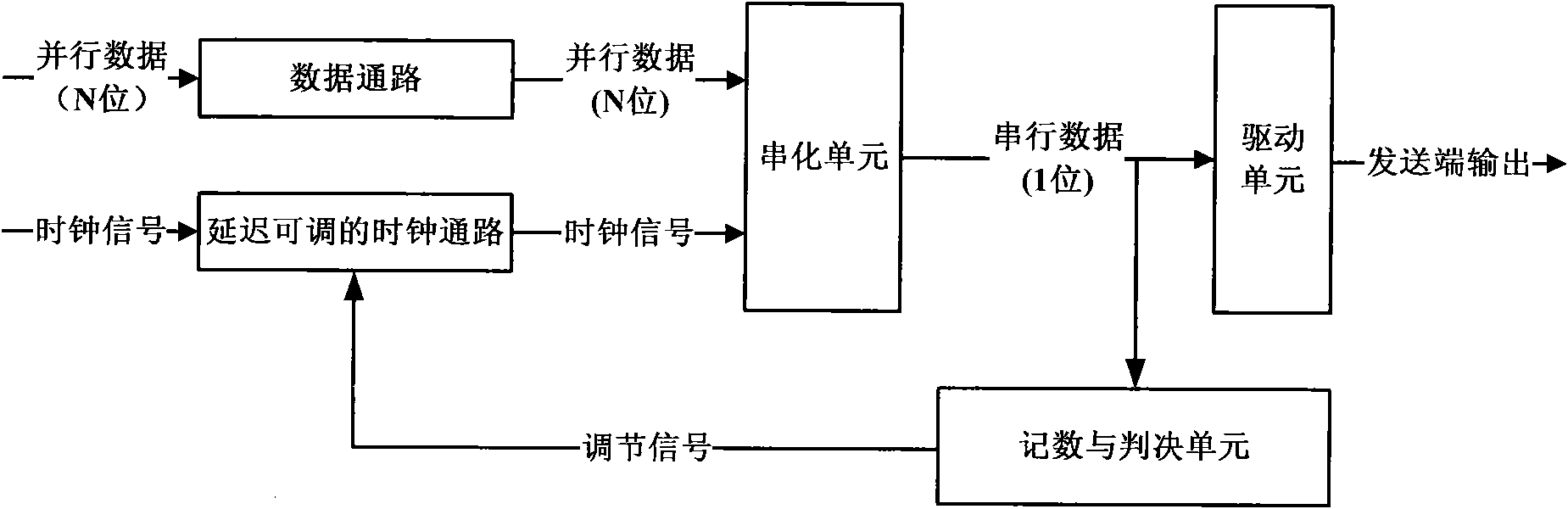

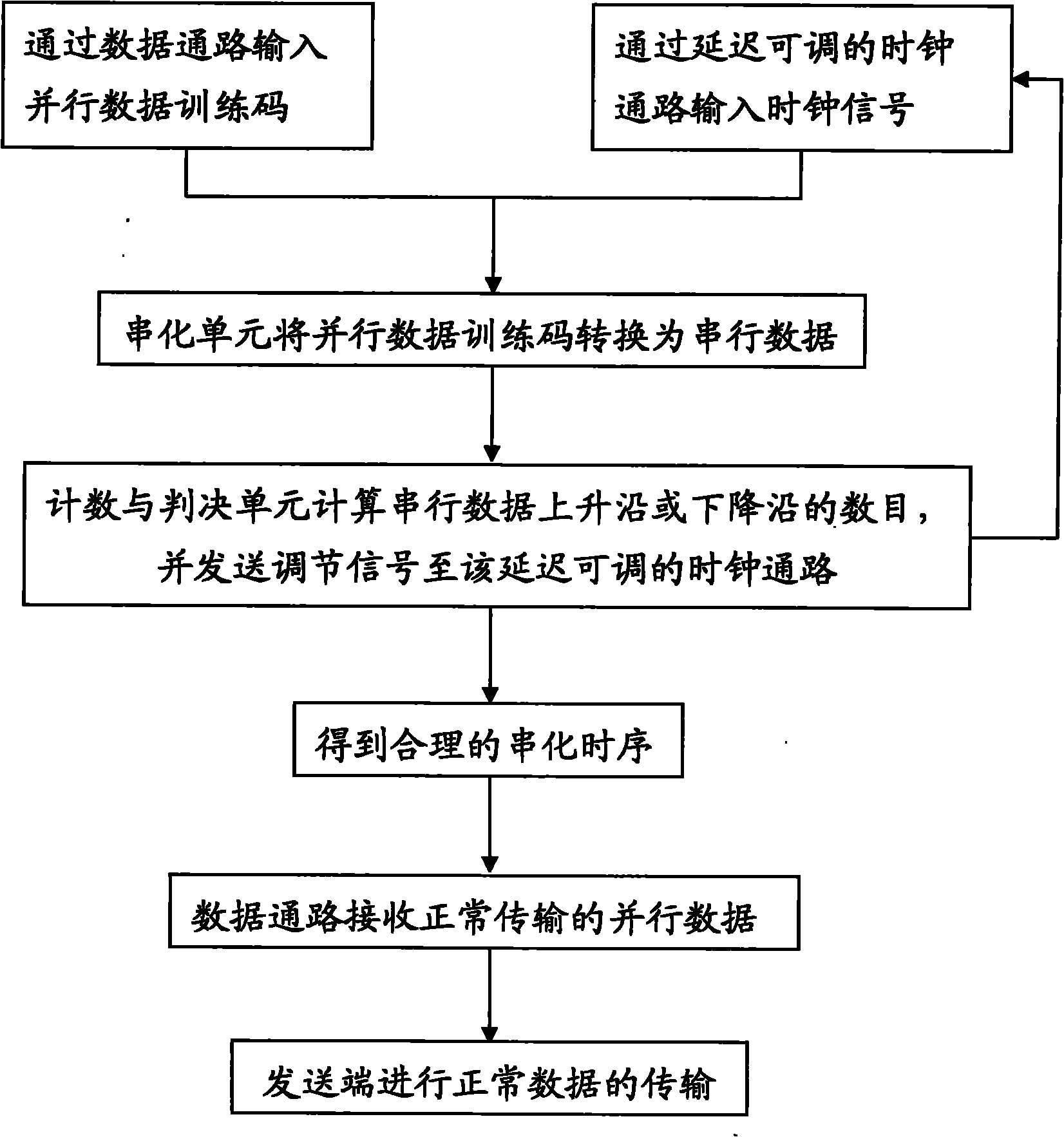

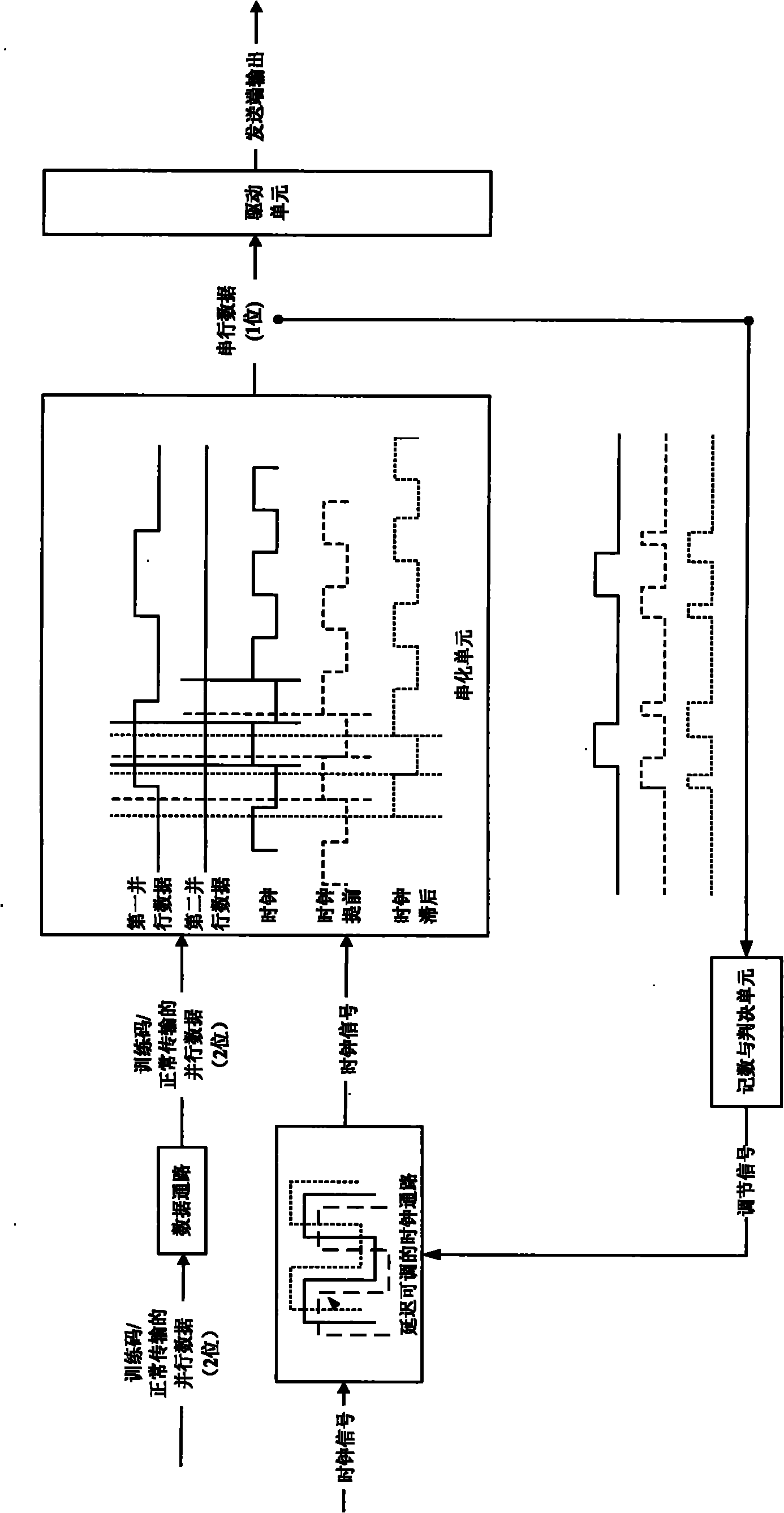

InactiveCN102064927AFix timing issuesParallel/series conversionCorrect operation testingData pathCorrection method

The invention relates to a time sequence error correction system which comprises a data path, a clock path with adjustable delay, a serializing unit, a driving unit and a counting and judging unit, wherein the data path is used for receiving parallel data; the clock path with the adjustable delay is used for receiving a clock signal; the serializing unit is connected with the data path and the clock path with the adjustable delay and used for converting the parallel data into serial data; the driving unit is used for converting the serial data into a current signal or a voltage signal and outputting the signal; and the counting and judging unit is used for calculating the number of rising edges or falling edges of the serial data and sending a regulating signal for regulating the delay time of the clock signal to the clock path with the adjustable delay to control the time sequence of the serializing unit so as to ensure that the number of the rising edges or the falling edges is the same as a preset correct number, and the time sequence of the serializing unit reaches an optimal value. The invention also provides a time sequence error correction method. The method effectively solves the time sequence problem in a serializing process.

Owner:新疆芯团科技集团有限公司

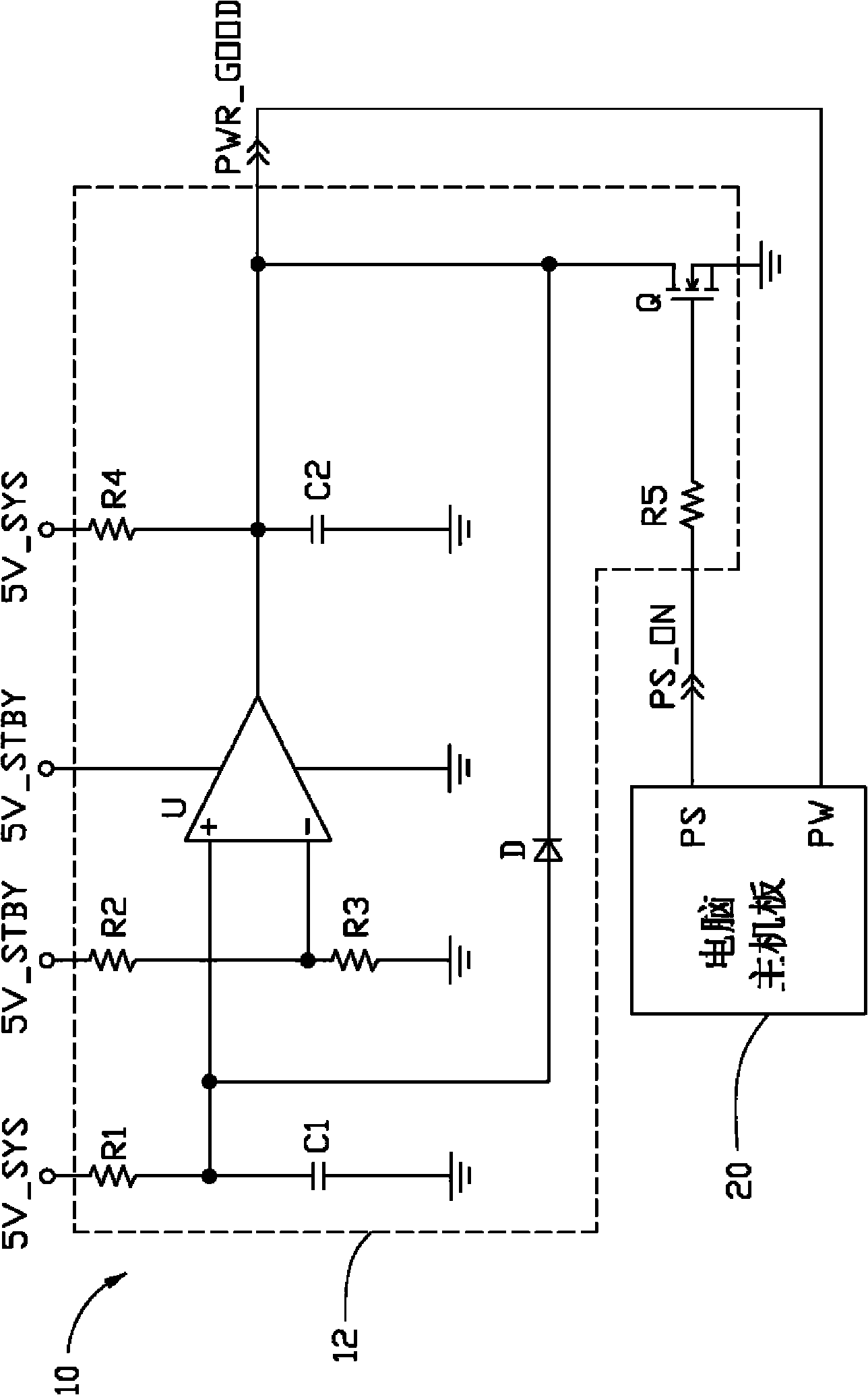

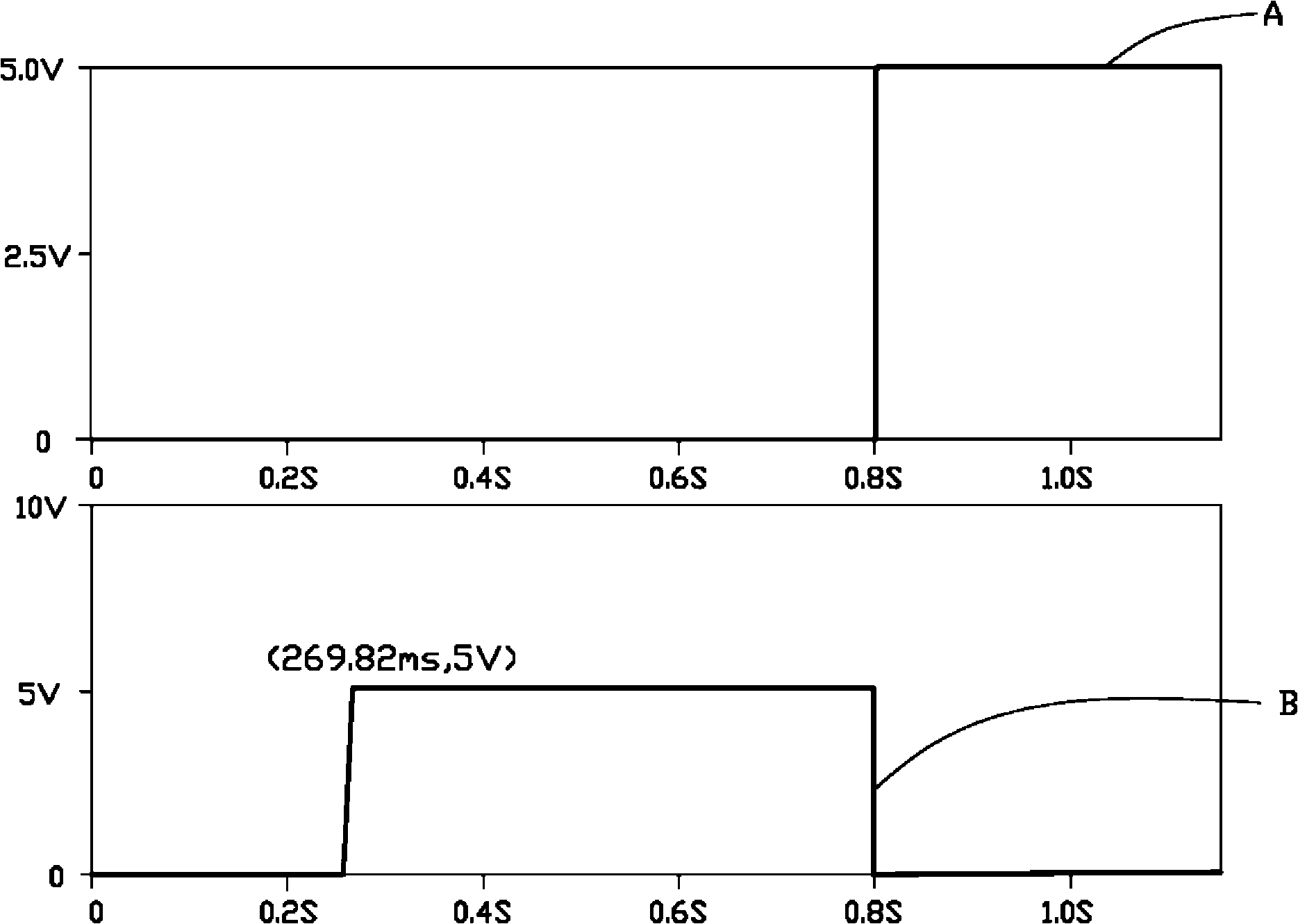

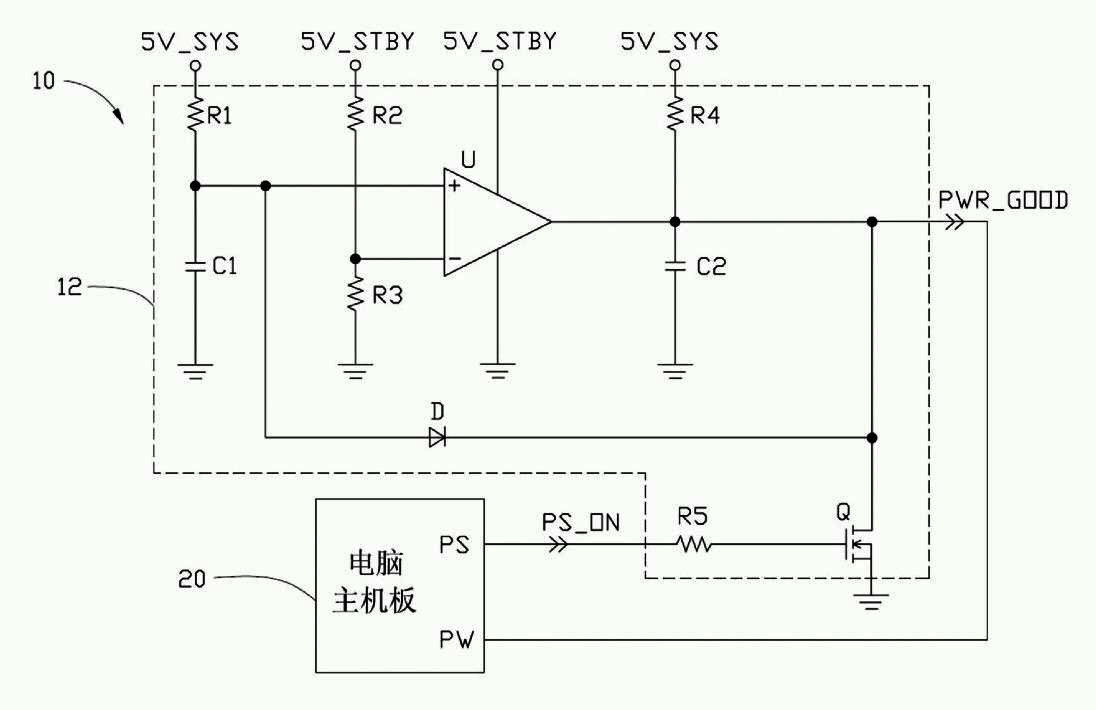

Computer power and power state signal generating circuit thereon

InactiveCN101872229AFix timing issuesNo jitterVolume/mass flow measurementPower supply for data processingCapacitanceElectrical resistance and conductance

The invention relates to a computer power comprising a system voltage output end, a backup voltage output end and a power state signal generating circuit. The power state signal generating circuit comprises an operational amplifier, a first resistor, a second resistor, a third resistor, a fourth resistor, a fifth resistor and an electronic switch, wherein one end of the first resistor is connected with the system voltage output end and the other end is grounded through a capacitor; a node between the first resistor and the capacitor is connected with the in-phase input end of the operational amplifier; one end of the second resistor is connected with the backup voltage output end and the other end is grounded through the third resistor; a node between the second resistor and the third resistor is connected with the inverted input end of the operational amplifier; the output end of the operational amplifier outputs a power state signal; one end of the fourth resistor is connected with the system voltage output end and the other end is connected to the output end of the operational amplifier and the first end of the electronic switch; the second end of the electronic switch is grounded; and the third end of the electronic switch receives power-on signals sent by a computer mainboard through the fifth resistor. The power supply can satisfy the requirement of power time sequence of the mainboard.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

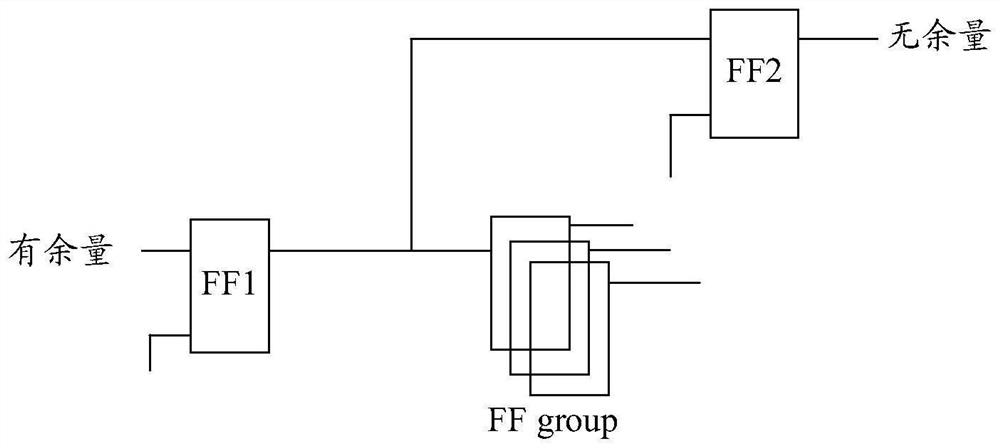

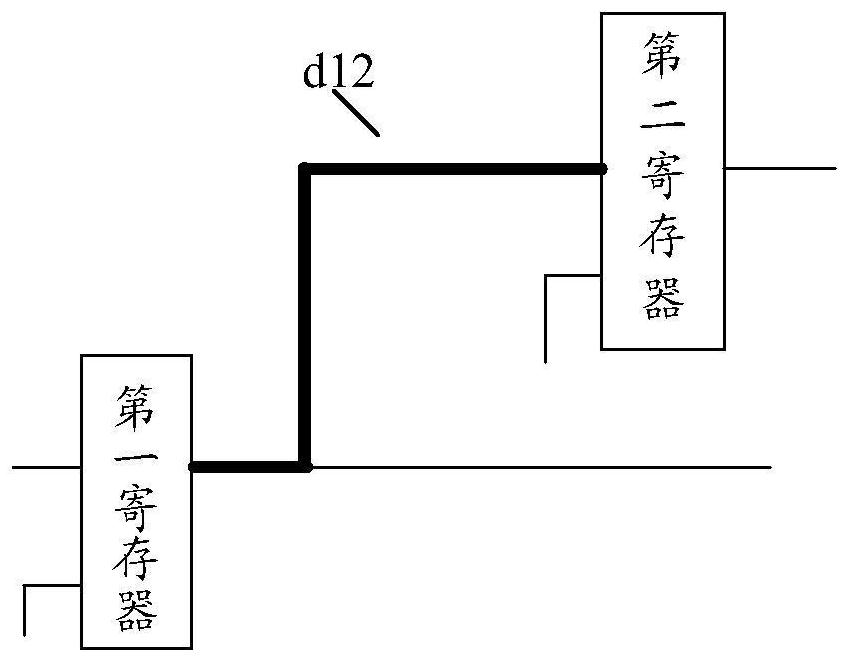

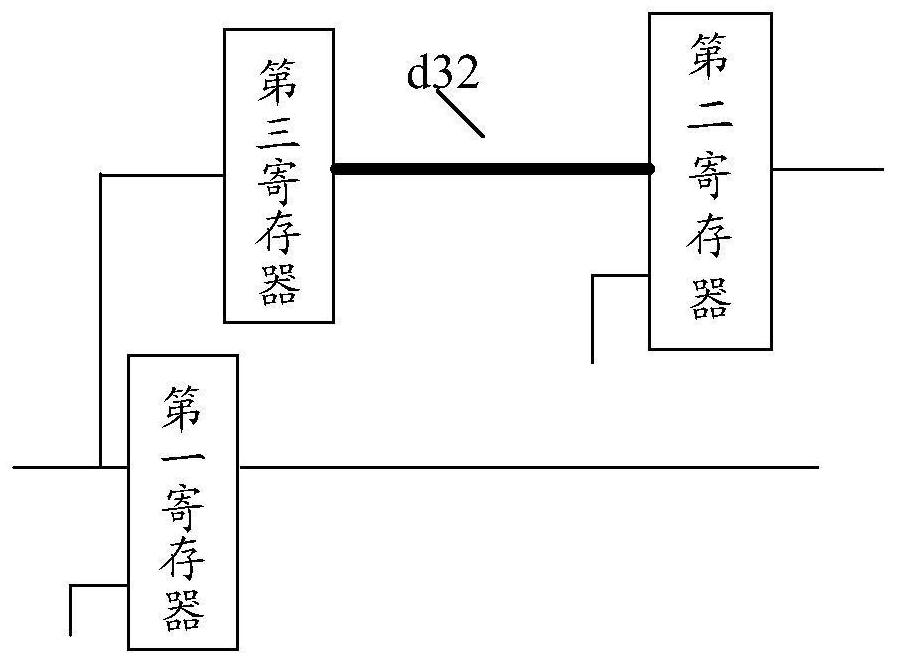

Time sequence optimization circuit and method, chip and electronic equipment

PendingCN114841104AThe effect of achieving timing closureFix timing issuesComputer aided designSpecial data processing applicationsComputer hardwareHemt circuits

The embodiment of the invention discloses a time sequence optimization circuit and method, a chip and electronic equipment, the electronic equipment comprises the chip provided with the time sequence optimization circuit, the time sequence optimization circuit comprises a first register, a second register and a third register, and the third register is a duplicated register of the first register; the path distance between the first register and the second register is greater than that between the third register and the second register; when a time sequence report obtained by executing the time sequence analysis command indicates that time sequence violation exists in the first time sequence path, the second time sequence path is used for performing time sequence optimization processing; the path starting point of the first time sequence path is a first register, and the path end point is a second register; the path starting point of the second time sequence path is the third register, and the path end point is the second register. The time sequence optimization method comprises the following steps: executing a time sequence analysis command to obtain a time sequence report; and when the time sequence report indicates that the time sequence violation exists in the first time sequence path, performing time sequence optimization processing through the second time sequence path.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

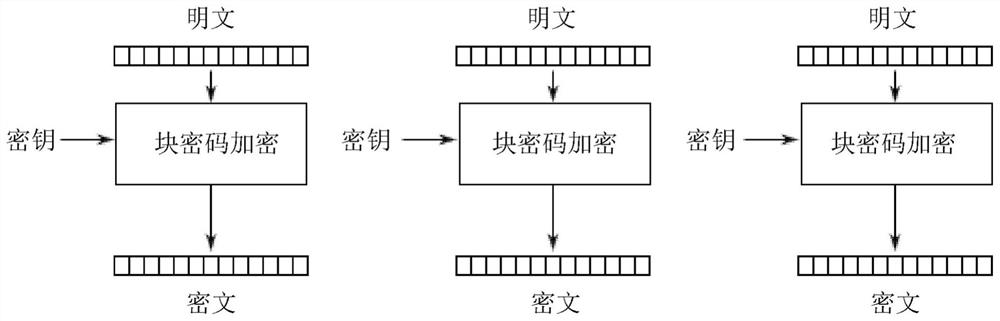

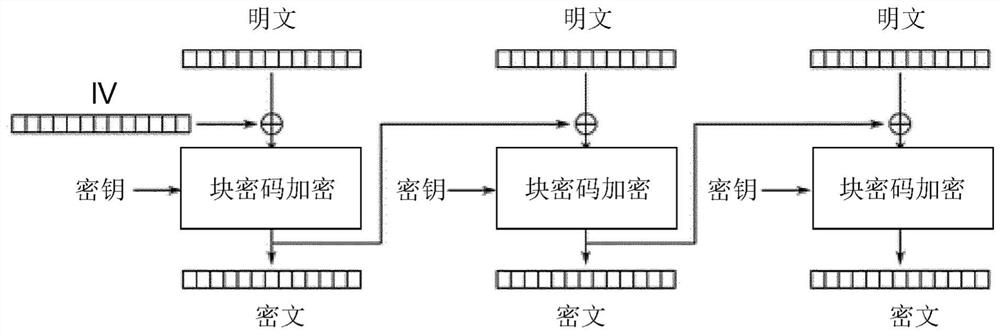

Memory-efficient hardware cryptographic engine

PendingCN112513856AReduce loadResolve synchronizationEncryption apparatus with shift registers/memoriesInternal/peripheral component protectionComputer hardwareComputer architecture

A hardware cryptographic engine (8) comprises a direct-memory-access (DMA) input module (13) for receiving input data over a memory bus, and a cryptographic module (15). The cryptographic module (15)comprises an input register (20) having an input-register length, and circuitry (22) configured to perform a cryptographic operation on data in the input register (20). The hardware cryptographic engine (8) further comprises an input-alignment buffer (16) having a length that is less than twice said input-register length, and alignment circuitry (23) for performing an alignment operation on inputdata in the input-alignment buffer(16). The hardware cryptographic engine (8) is configured to pass input data, received by the DMA input module (13), from the memory bus (10) to the input register (20) of the cryptographic module (15) after buffering an amount of input data no greater than the length of the input-alignment buffer (16).

Owner:NORDIC SEMICONDUCTOR

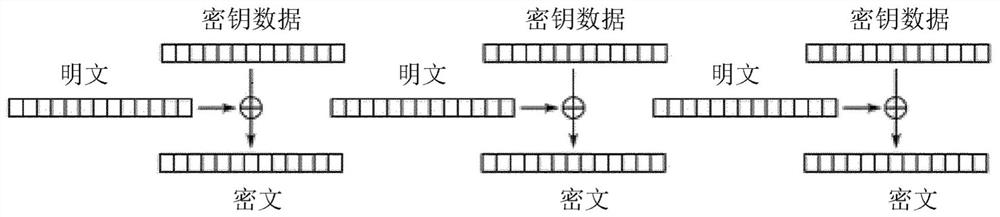

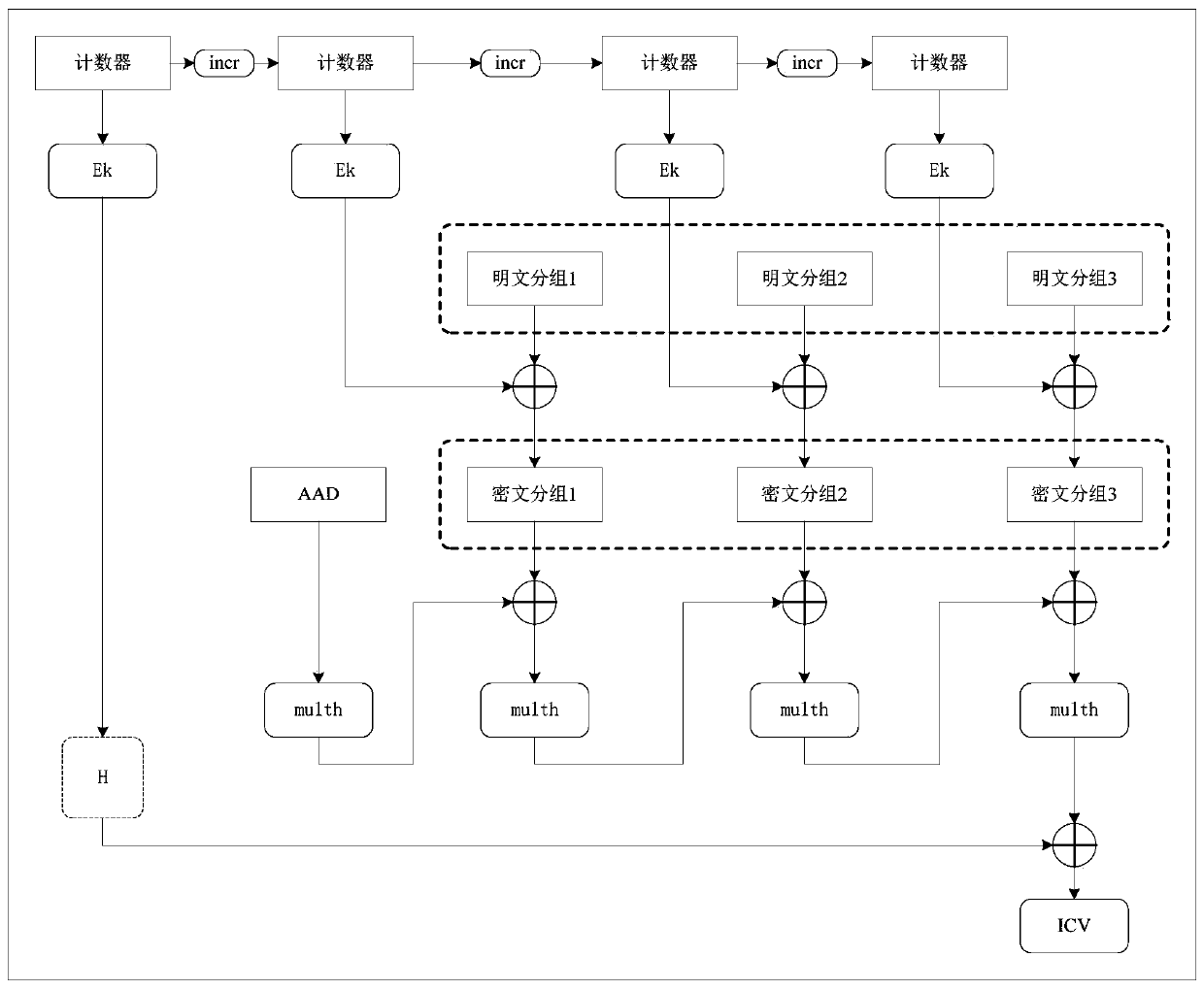

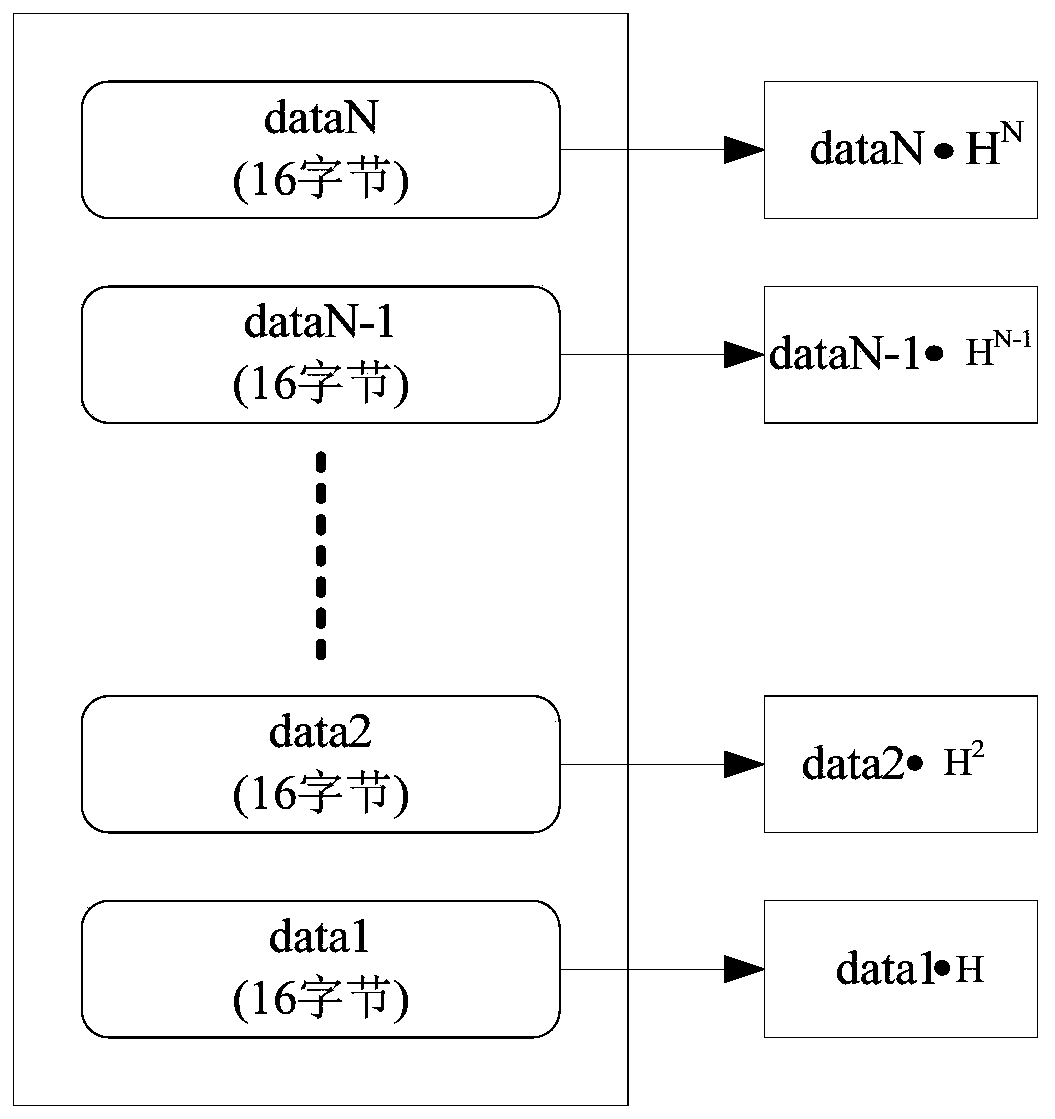

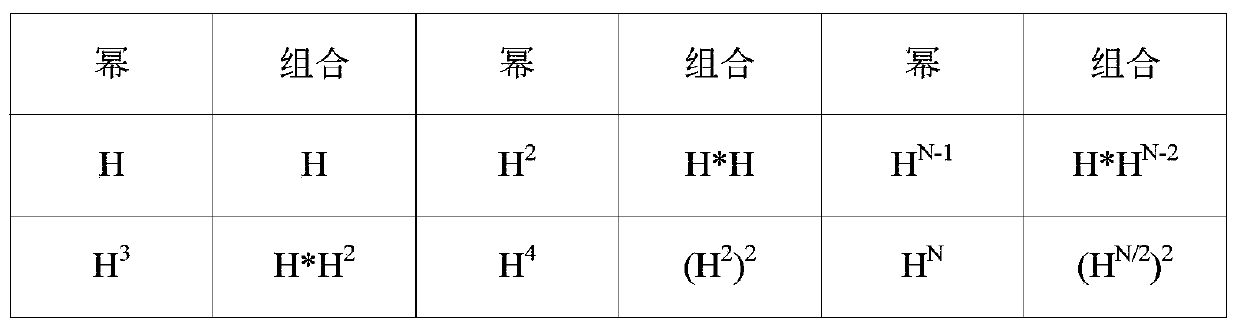

A chip data processing method and system based on an AES-GCM

InactiveCN109714151AFix timing issuesLower latencyEncryption apparatus with shift registers/memoriesPlaintextComputer science

The invention provides a chip data processing method and system based on an AES-GCM. The method comprises the steps that S1, initializing a chip; S2, performing AES encryption on the binary number '0'by using a key k to obtain a variable H, and calculating the integer power of the variable H; And S3, grouping the plaintext data based on an AES algorithm, carrying out point multiplication on eachgroup of plaintext data and the integer power of the corresponding variable H in a finite field, and finally obtaining the ICV value of the authentication tag. According to the invention, the delay ofdata processing is reduced, the operation speed of the chip is improved, the number of triggers is reduced, and the area of the chip is reduced.

Owner:SUZHOU CENTEC COMM CO LTD

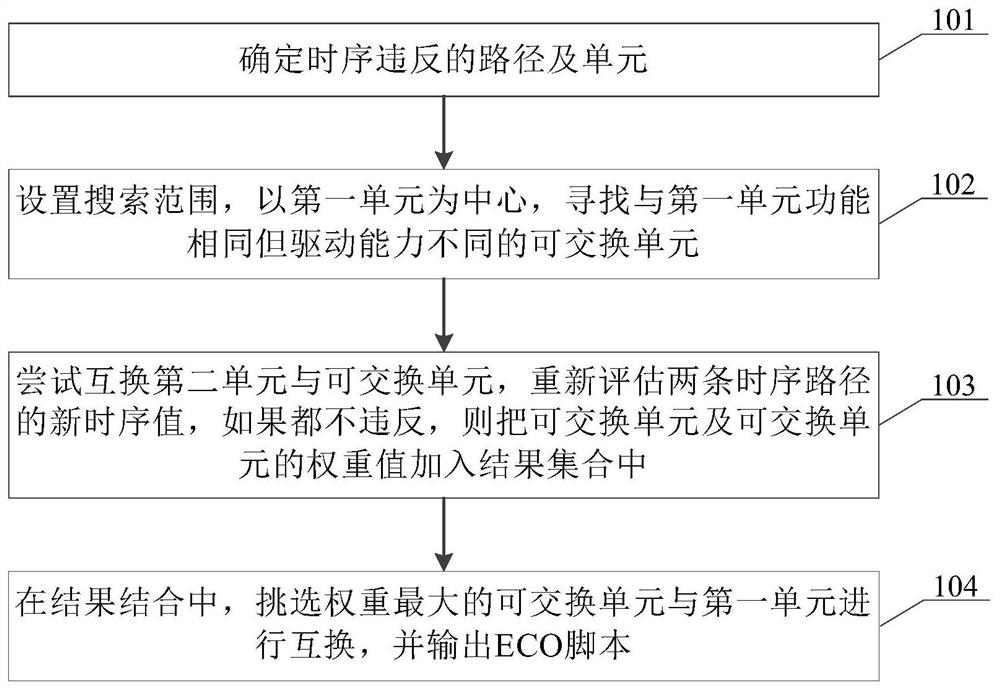

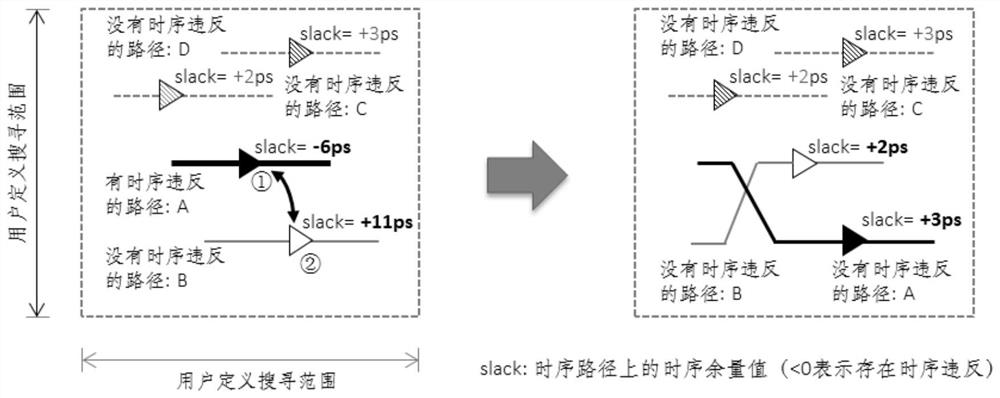

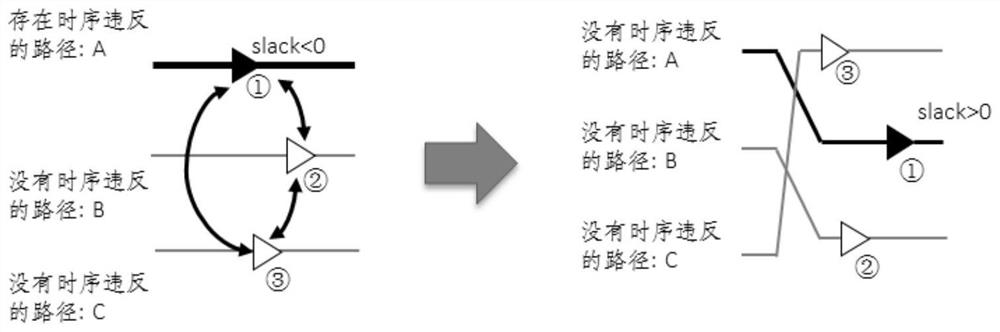

A time sequence path correction method

InactiveCN112668266AFix timing issuesGuaranteed to workComputer aided designSpecial data processing applicationsAlgorithmResult set

The invention discloses a time sequence path correction method. The method comprises the following steps: determining a path and a unit of time sequence violation; setting a search range and searching an exchangeable unit; exchanging the time sequence violation units and the exchangeable units, evaluating new time sequence values of the two time sequence paths, and adding the exchangeable units which do not violate the time sequence and weight values of the exchangeable units into a result set; and in the result set, selecting the exchangeable unit with the maximum weight value to be exchanged with the time sequence violation unit to generate a result path. According to the time sequence path correction method, on the premise that the chip design physical layout is not changed and the chip function behavior is not changed, the purpose of time sequence optimization is achieved through unit exchange, so that time sequence correction can be carried out in the post-mask stage in the design later stage, and the correctness of chip design is guaranteed.

Owner:北京华大九天科技股份有限公司

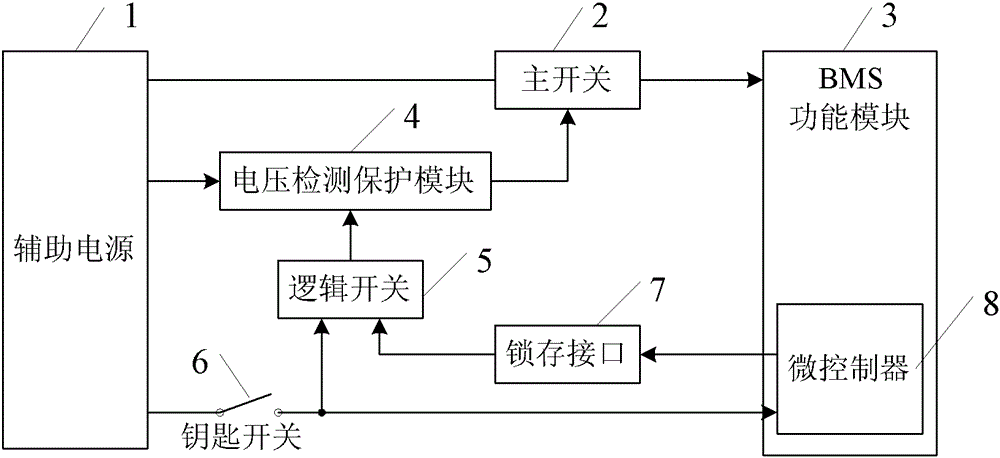

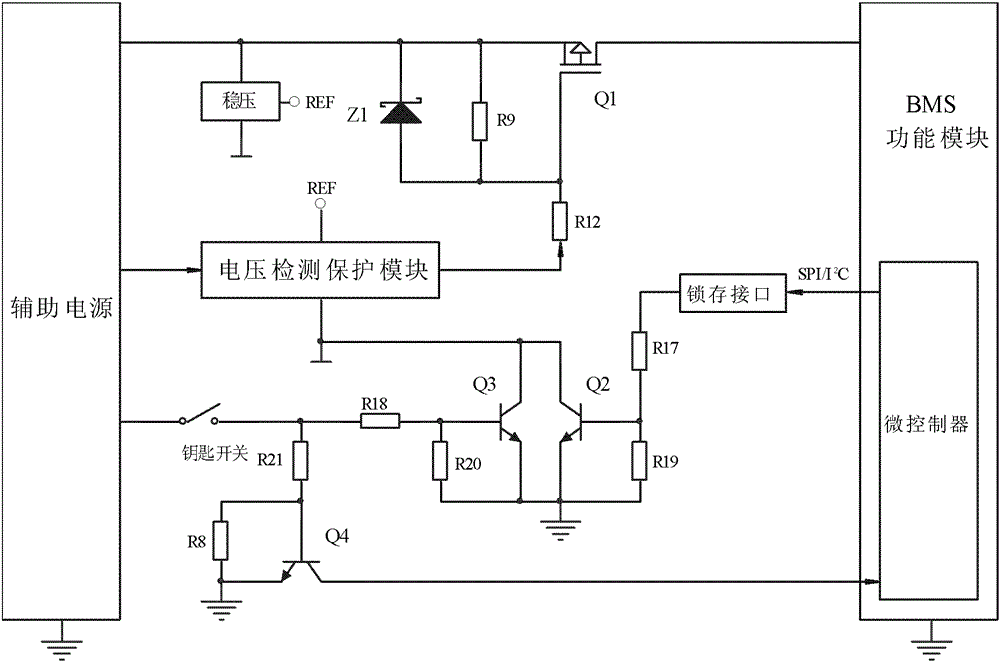

Battery Management System with Power Control

ActiveCN102231553BAvoid problems with wrong control strategiesWith automatic power lock functionBatteries circuit arrangementsElectric powerElectricityOvervoltage

Owner:陕西法士特松正电驱系统股份有限公司

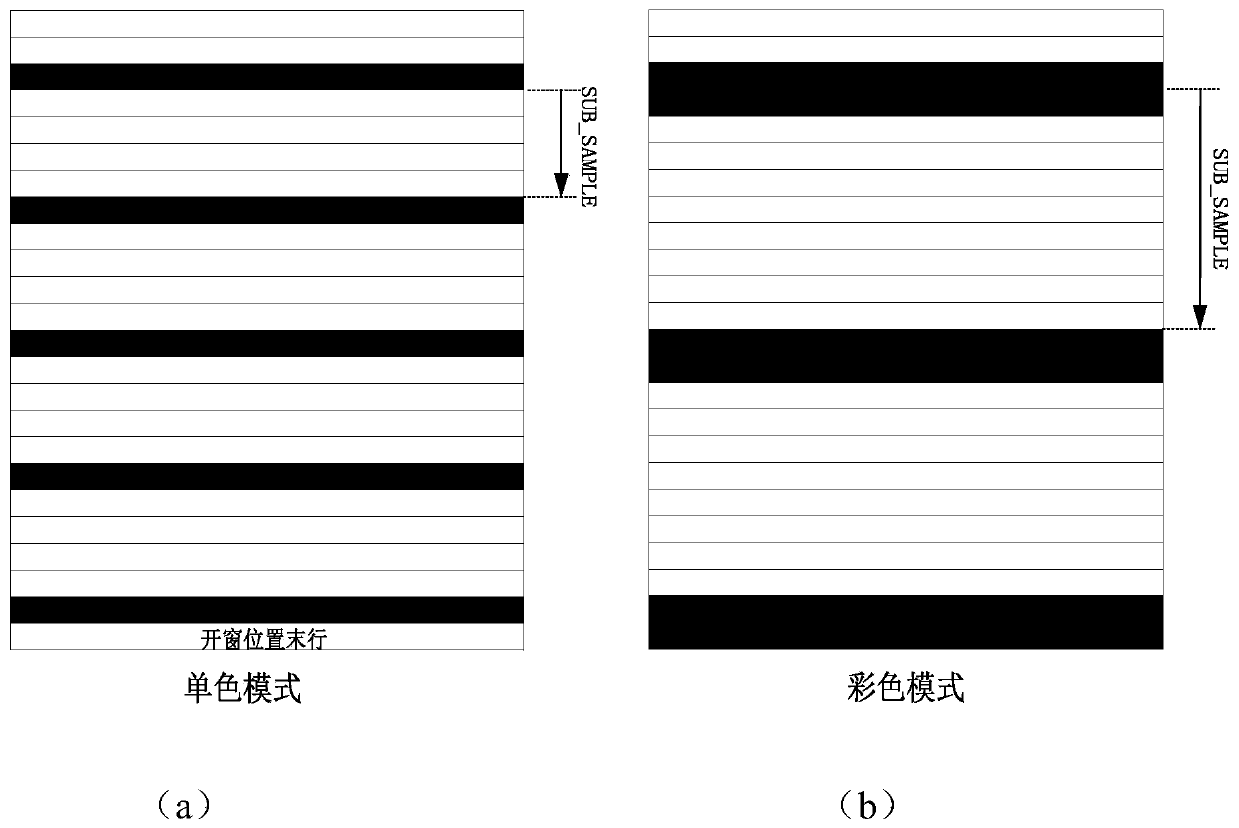

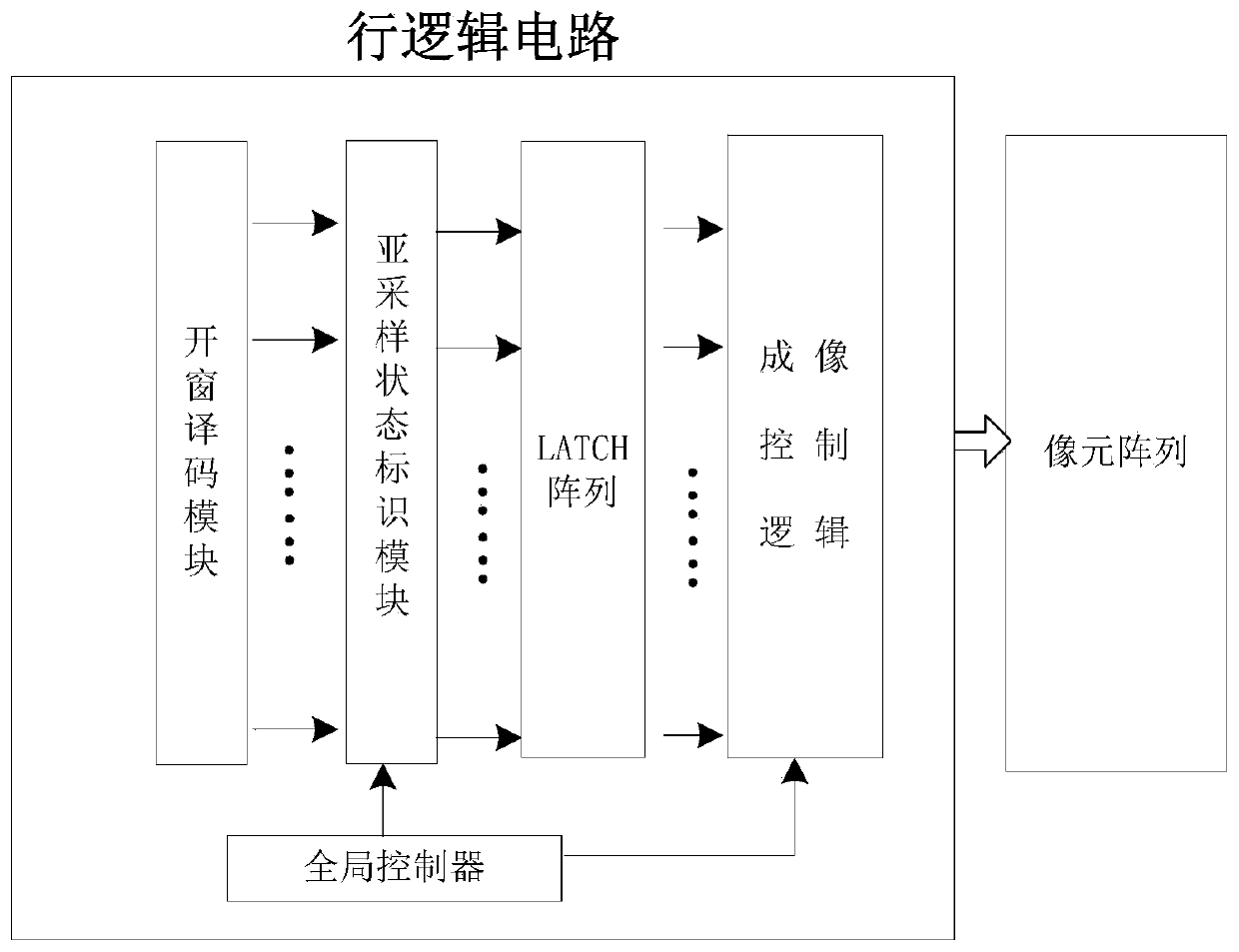

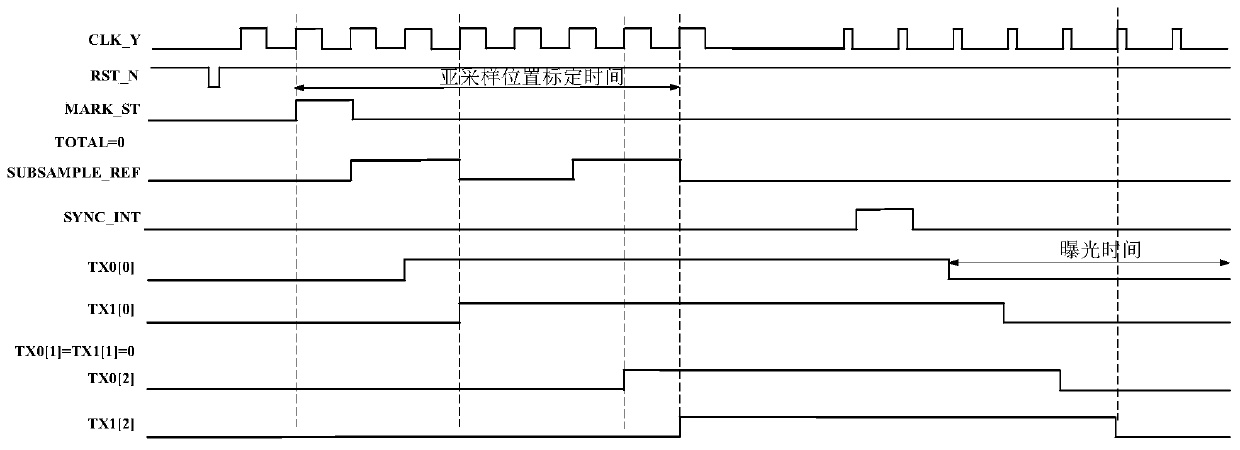

Free sub-sampling type row logic circuit for image sensor and working method thereof

ActiveCN111294530AFix timing issuesQuick lockTelevision system detailsColor television detailsExposureEmbedded system

The invention belongs to the technical field of image sensors, and discloses a free sub-sampling type row logic circuit for an image sensor and a working method thereof. According to the invention, through a windowing decoding module, a sub-sampling state identification module, a LATCH array, a global controller and an imaging control logic module, control of pixel rows of the image sensor is completed; a plurality of exposure modes are supported; full-array free sub-sampling of the super-large-scale pixel array is realized through sub-sampling identification of the pixel array; through the design of an address identifier and a sub-sampling pointer chain, a small-area sub-sampling mark in a windowing range is supported; subsampling one-key turn-off is supported; through clock gating design, the sub-sampling identification and the pixel imaging work frequency are different, and sub-sampling rapid calibration is realized. The free sub-sampling type row logic circuit is simple in design structure, flexible in configuration, wide in application range and capable of supporting multiplexing and splicing and can be applied to different types of image sensor chip circuits.

Owner:XIAN MICROELECTRONICS TECH INST

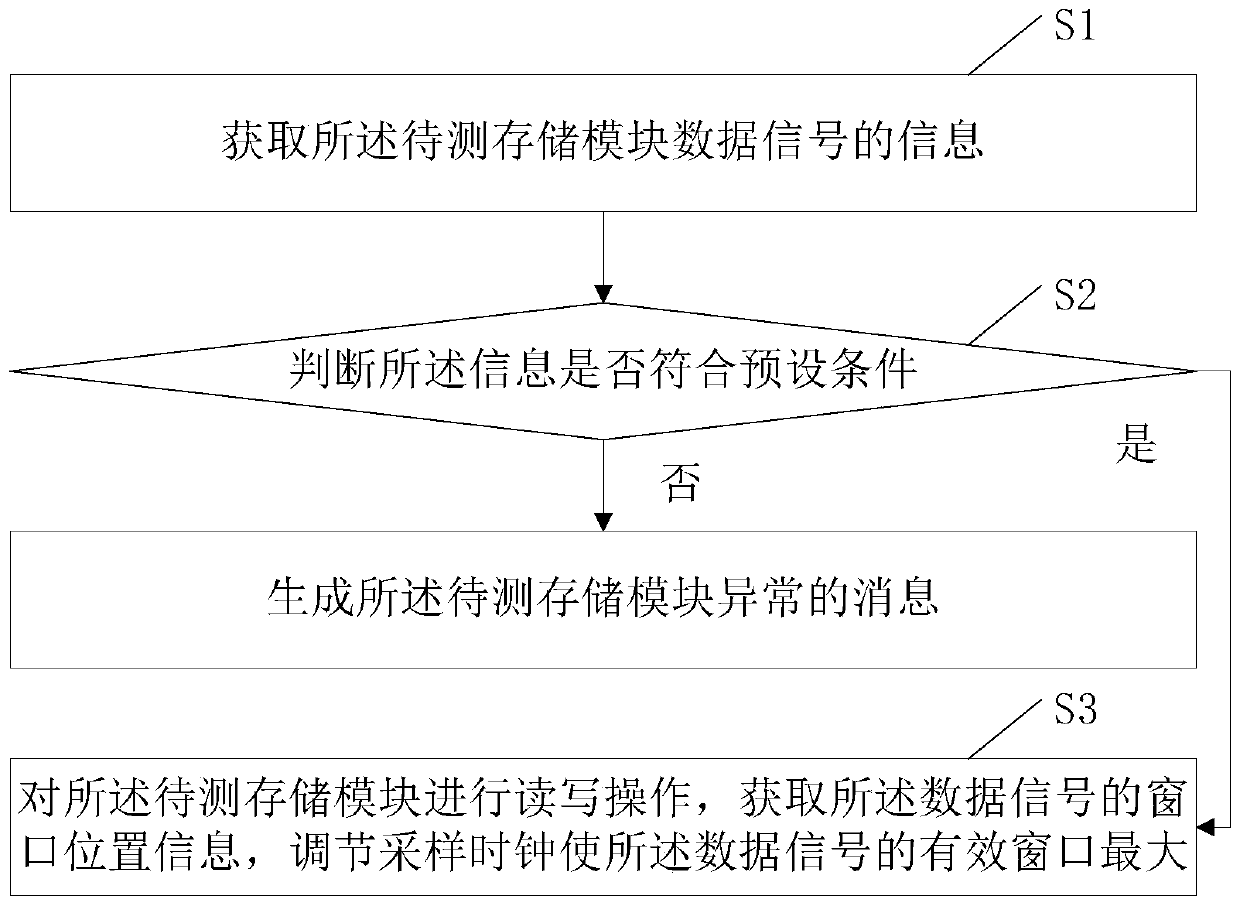

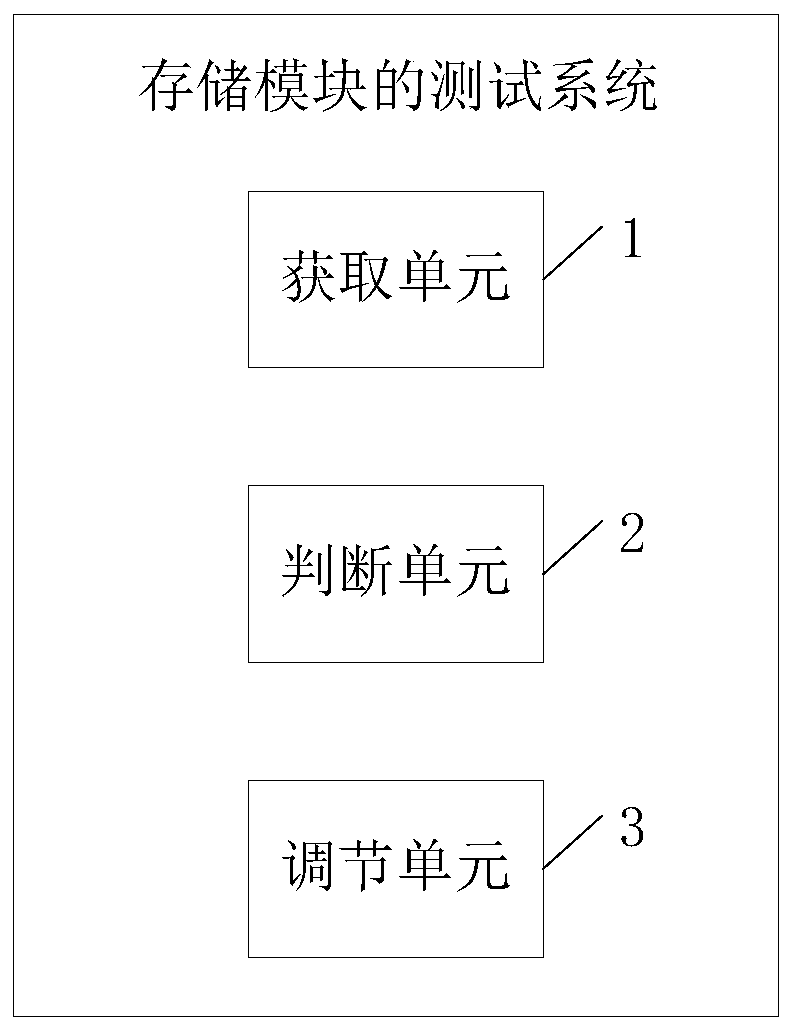

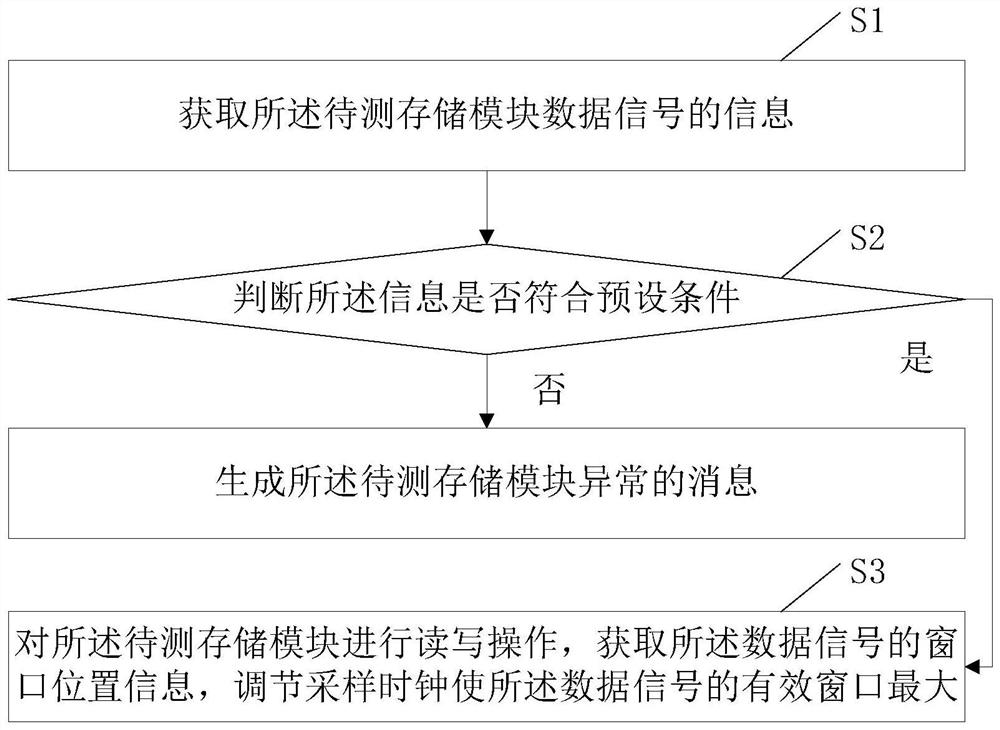

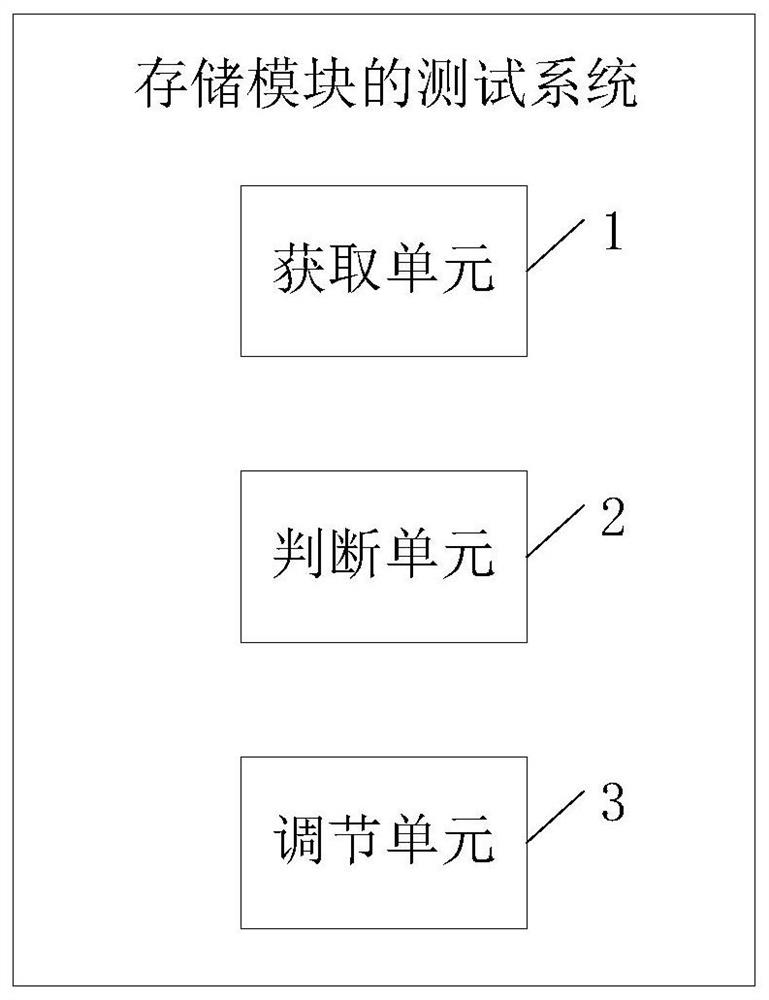

A storage module testing method and system

The invention discloses a storage module testing method and system, and belongs to the technical field of communication. According to the invention, the information of the acquired data signal of theto-be-tested storage module is judged so as to avoid a time sequence problem; Furthermore, read-write operation is further carried out on the to-be-tested storage module, window position information of the data signal is obtained, and a sampling clock is adjusted to enable an effective window of the data signal to be maximum, so that the purpose of automatically and quickly testing the storage module is achieved, and the testing efficiency is improved.

Owner:AMOLOGIC (SHANGHAI) CO LTD

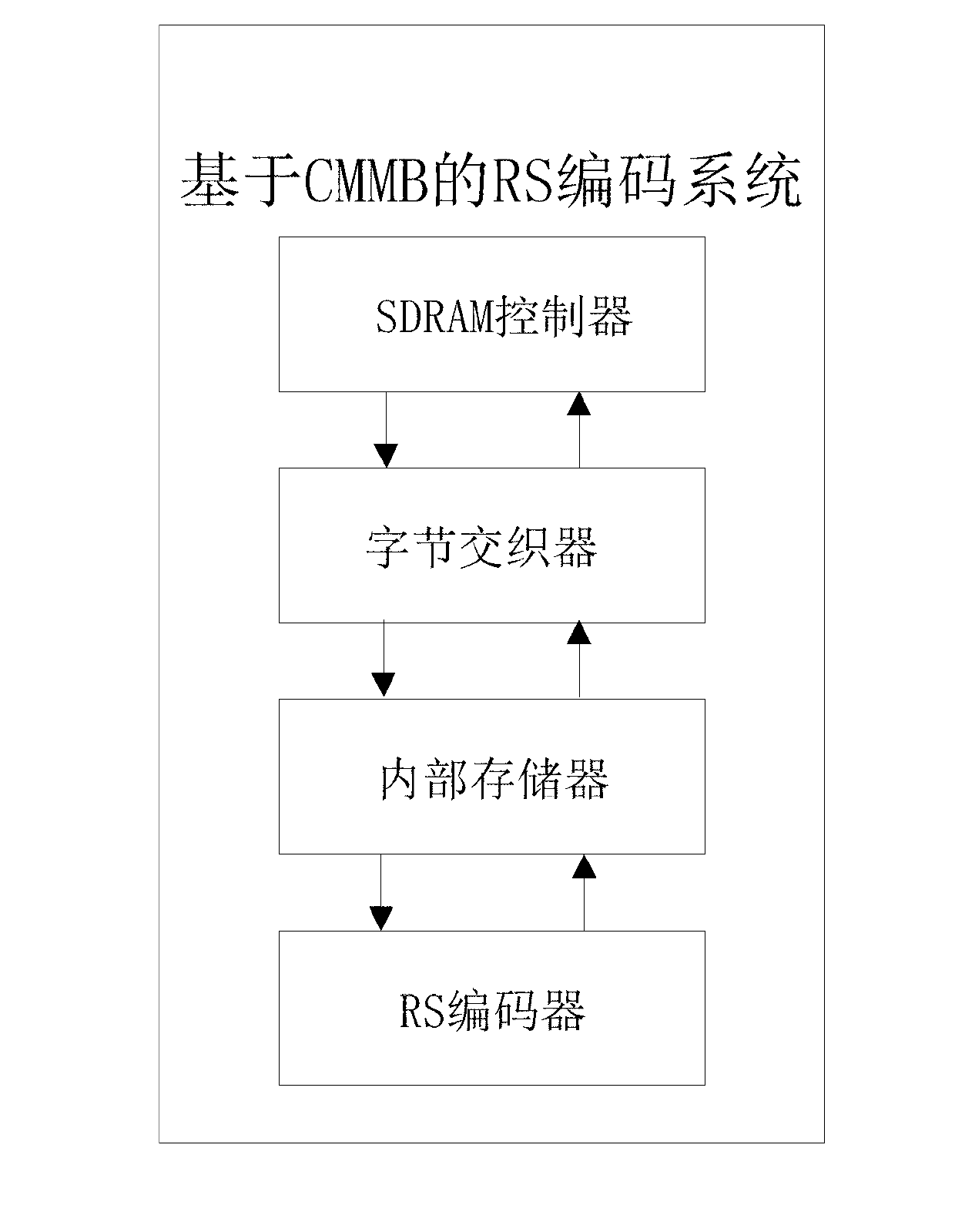

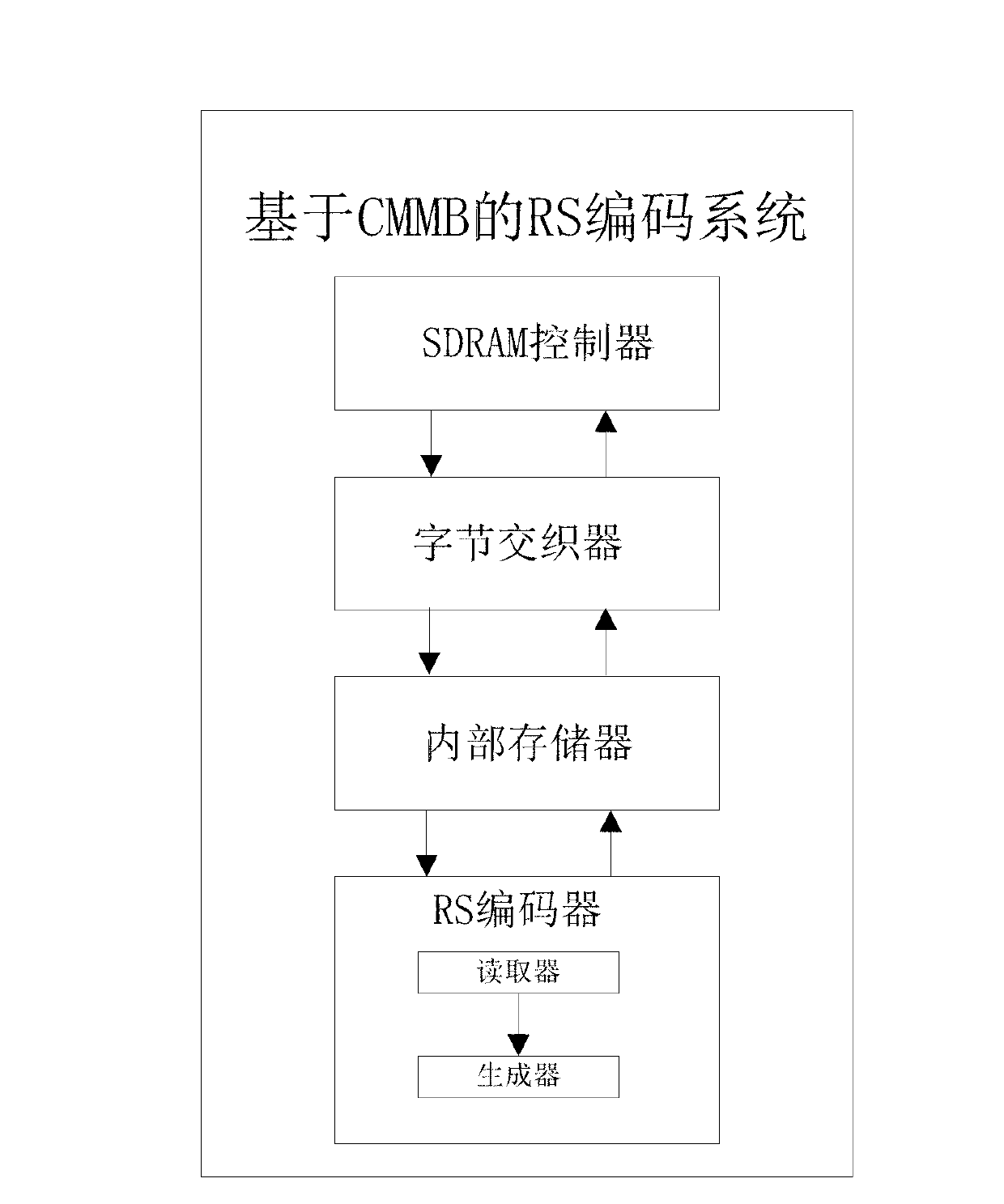

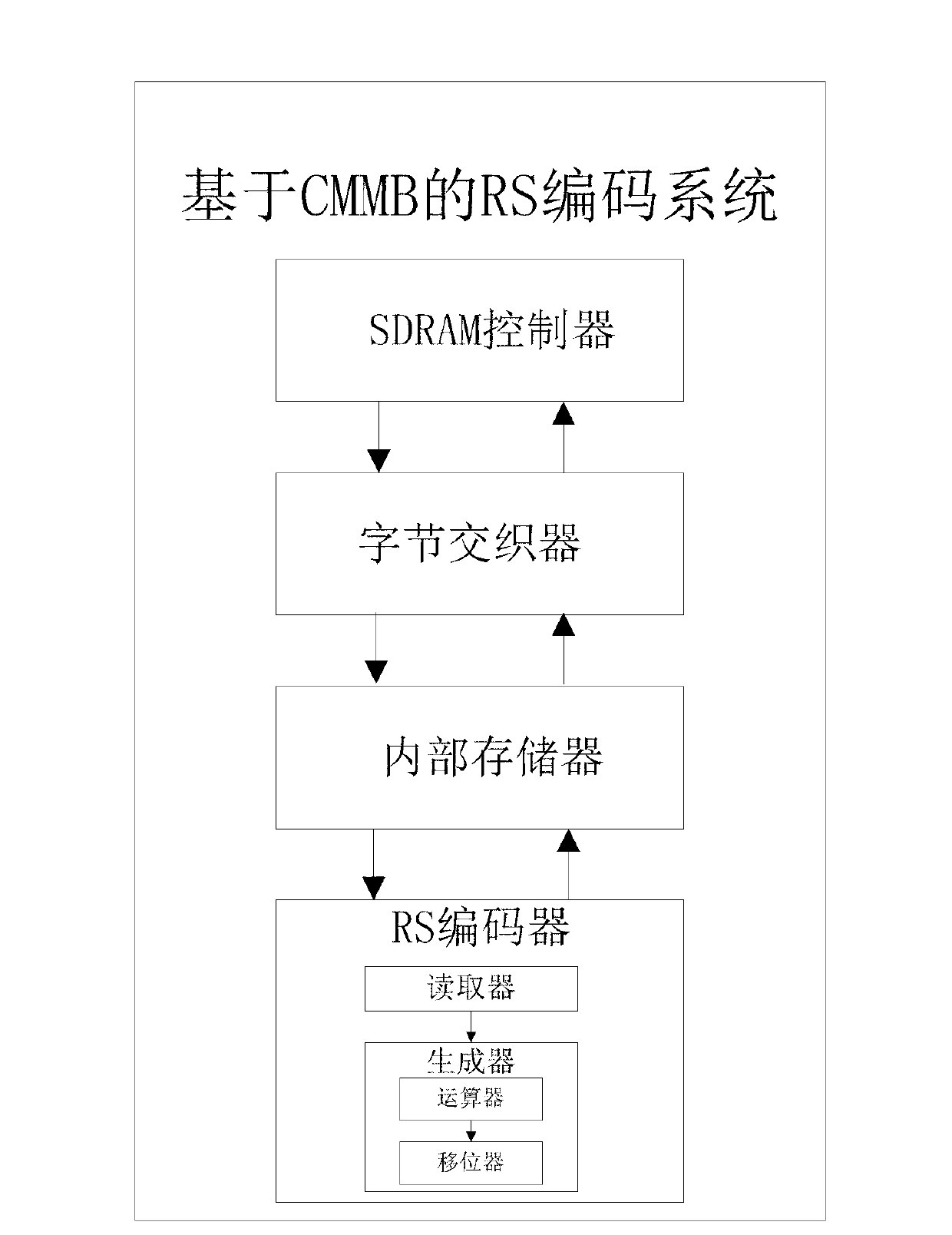

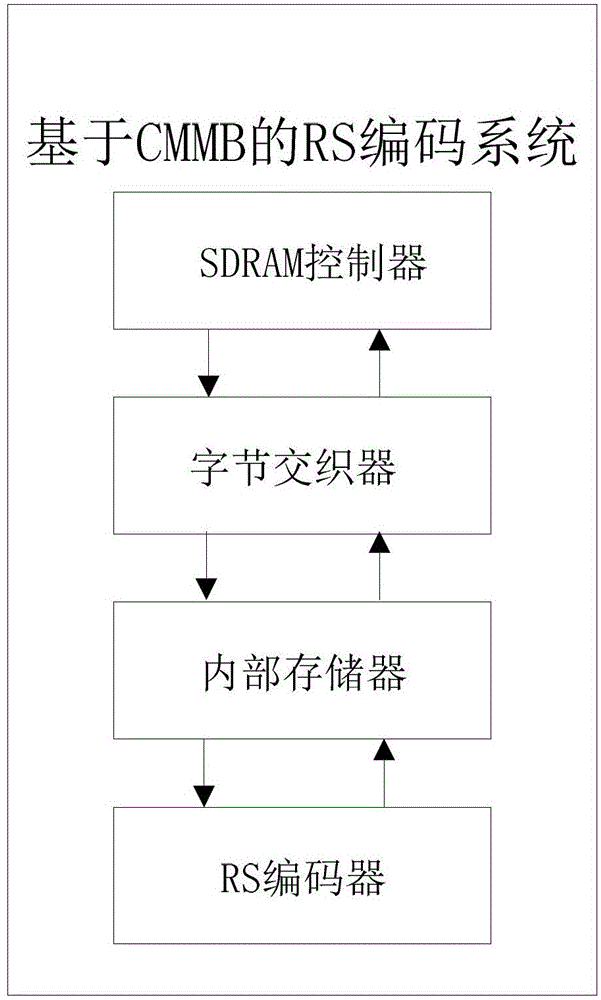

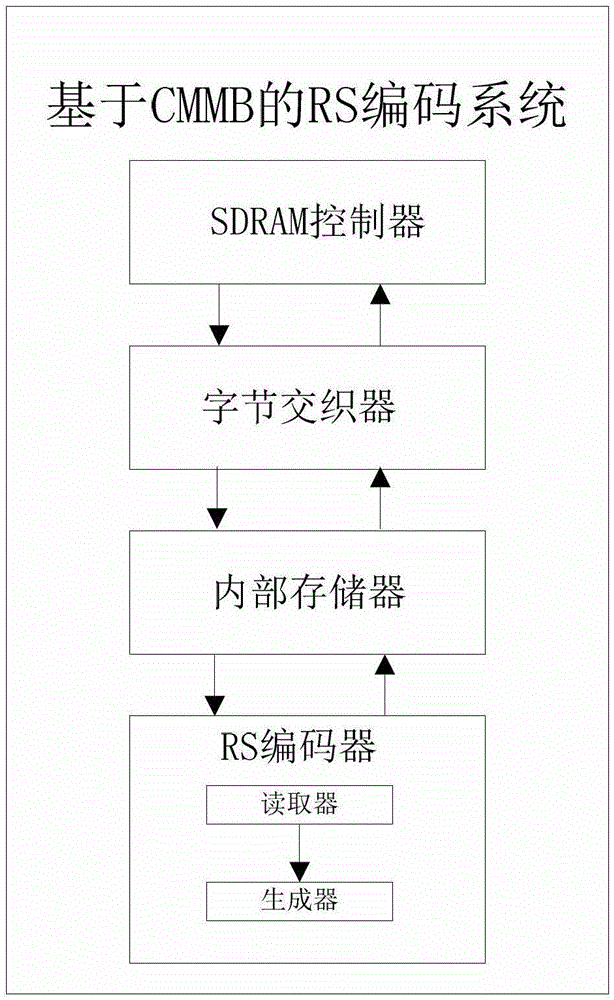

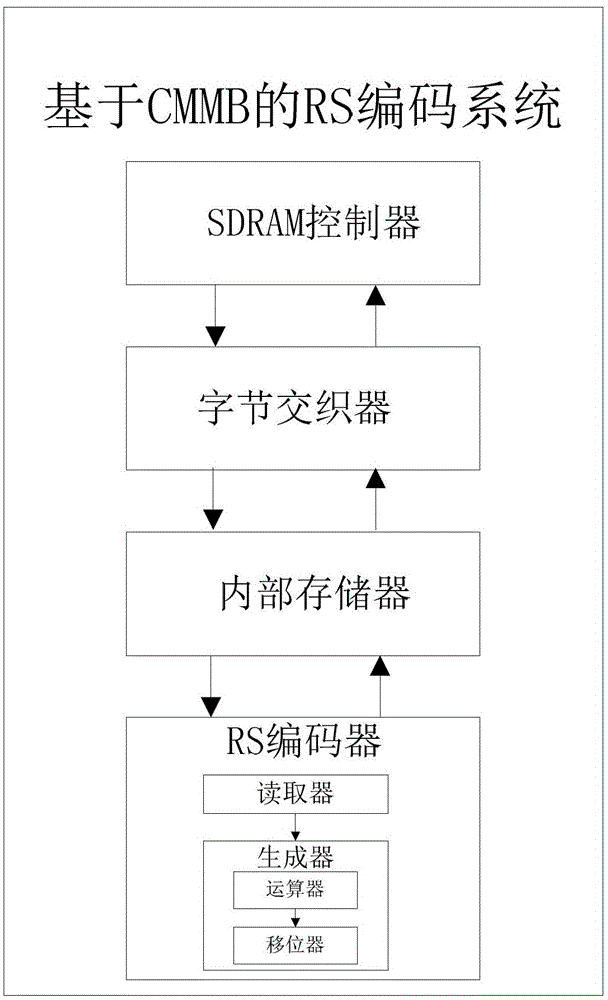

CMMB (China mobile multimedia broadcasting) based RS (reed-solomon) coding system and implementing method thereof

ActiveCN103001736ASave internal resourcesReduce computationError preventionInternal memorySynchronous dynamic random-access memory

The invention discloses a CMMB (China mobile multimedia broadcasting) based RS (reed-solomon) coding system and an implementing method thereof. The CMMB based RS coding system comprises an SDRAM (synchronous dynamic random access memory) controller, a byte interleaver, an internal memory and an RS coder, wherein the SDRAM controller is used for receiving information code streams and storing accessing check codes, the byte interleaver is used for subjecting accessing information codes and the check codes to byte interleaving, the internal memory is used for caching the accessing information codes and the check codes, and the RS coder is used for coding the information codes. The implementing method includes that the SDRAM controller receives the information code streams, the information codes are subjected to byte interleaving by the byte interleaver, the information codes interleaved are stored in the internal memory and are read and encoded and the like. By the CMMB based RS coding system and the implementing method thereof, internal resources of an FPGA (field programmable gate array) is effectively saved, and operation load is reduced, so that the problem about time sequence of the FPGA is solved, the low-end FPGA can be utilized for design, and normal work in complicated environment can be guaranteed.

Owner:ALLWIN TELECOMM

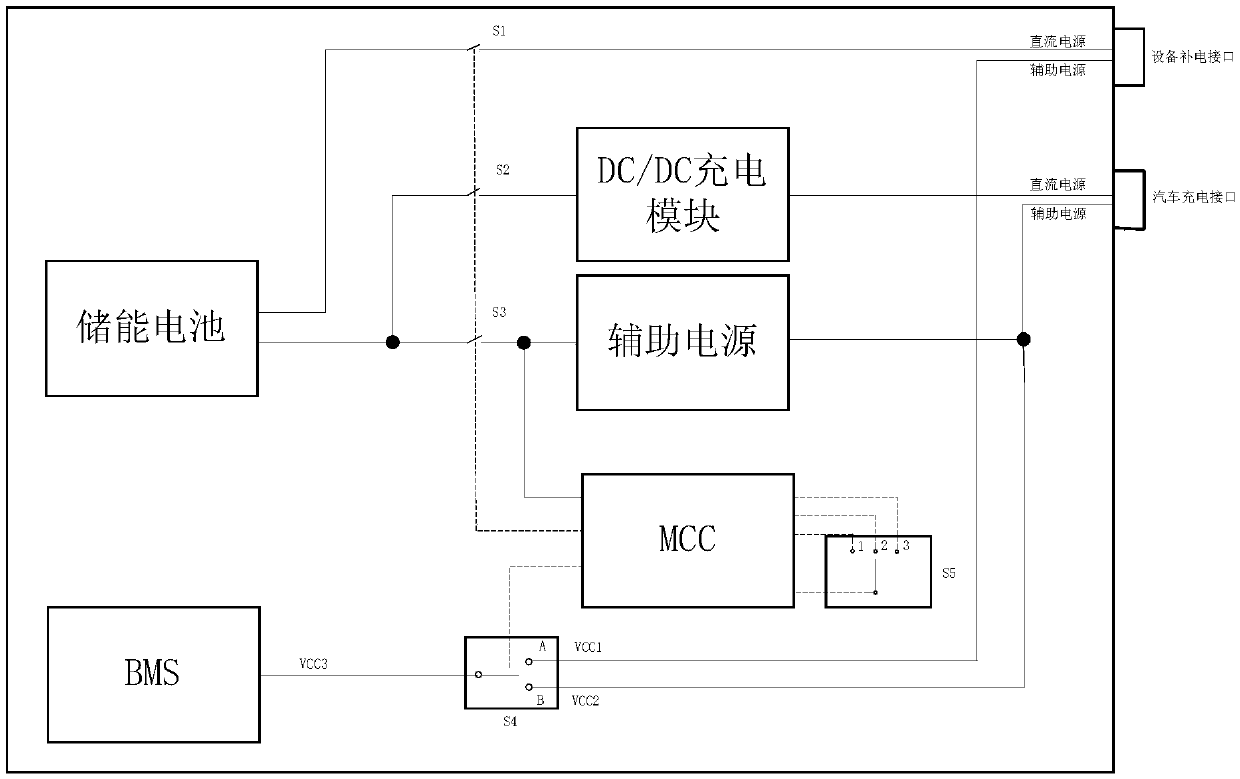

Mobile charging system and controlling method thereof

ActiveCN105515113AAvoid excessive dischargeExtended service lifeCharging stationsSafety/protection battery circuitsMobile chargeEngineering

The invention discloses a mobile charging system and a controlling method thereof. The mobile charging system comprises an energy storage battery and a battery management system, wherein the input end of the energy storage battery is connected to a recharging interface of equipment through a switch S1, the output end of the energy storage battery is connected to a charging interface of an automobile through a switch S2 and a switch S3, a DC / AC charging module is arranged between the switch S2 and the charging interface of the automobile, an auxiliary power supply is arranged between the switch S3 and the charging interface of the automobile, the battery management system is connected with a switch S4, a contact A of the switch S4 is connected to the recharging interface of the equipment, and a contact B of the switch S4 is connected to the output end of the auxiliary power supply, a mobile charging controller is arranged between the switch S3 and the auxiliary power supply, the mobile charging controller is connected with a switch S5 used for selecting operation states, and the mobile charging controller can be used for controlling the switches S1-S4 through the operation state of the switch S5. According to the mobile charging system and the controlling method thereof, standby loss of the system is reduced, over discharge of the battery is prevented, the service life of the battery is prolonged, and meanwhile the problem of time sequence in the process of automobile charging and equipment recharging can be solved.

Owner:XIAN TGOOD INTELLIGENT CHARGING TECH CO LTD +1

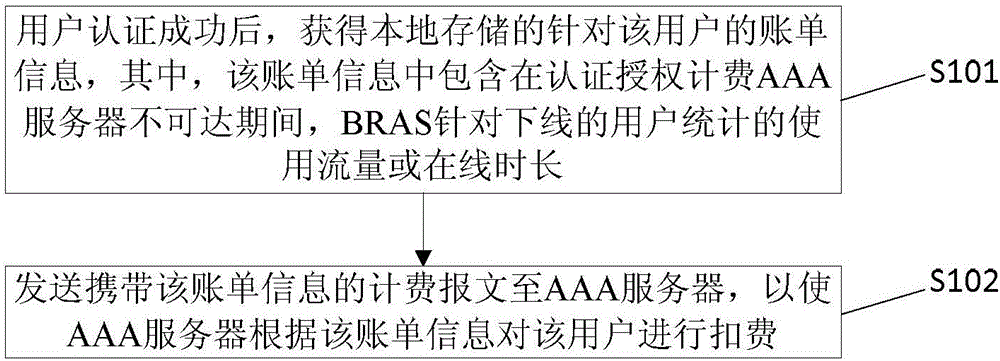

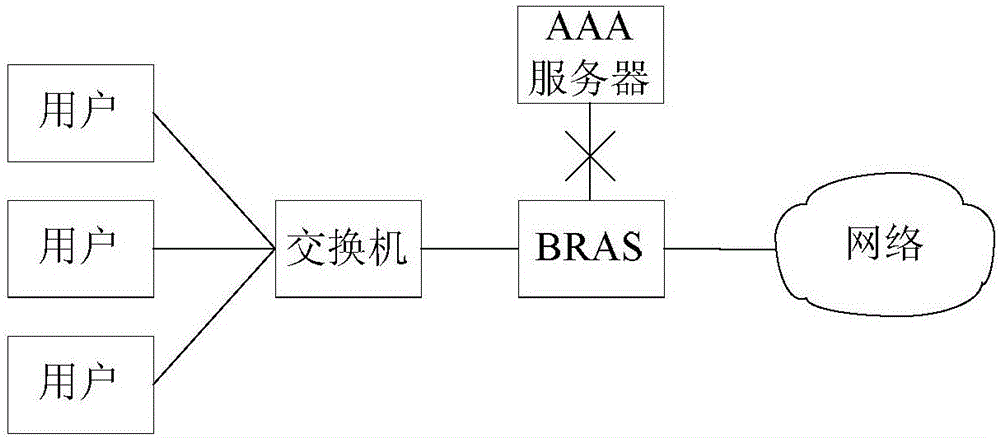

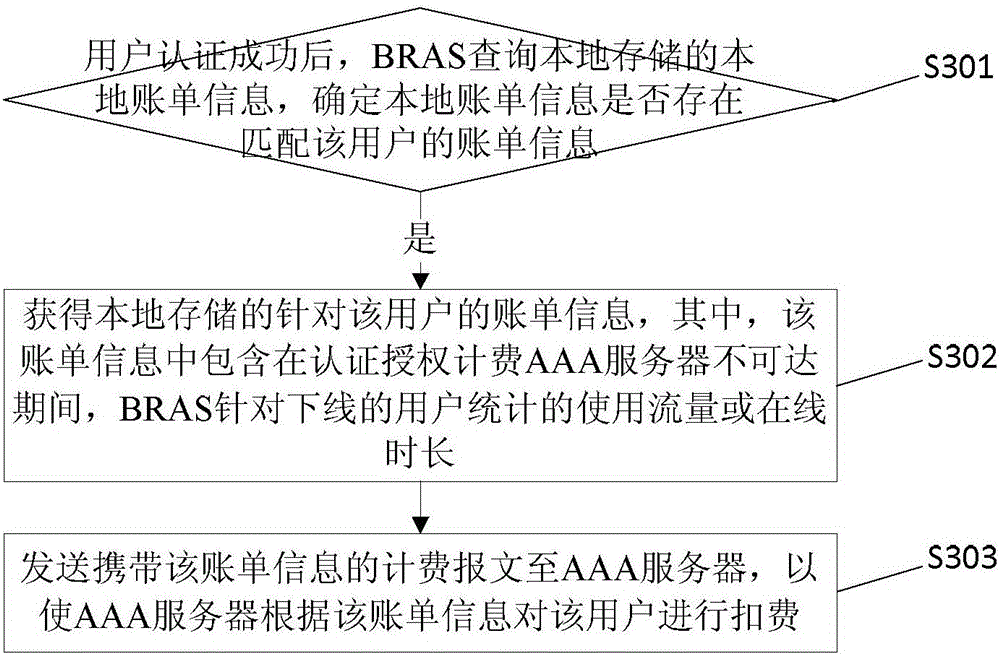

Accounting method and device

InactiveCN106411536AFix timing issuesTimely deductionMetering/charging/biilling arrangementsAccounting methodAuthentication authorization accounting

The invention provides an accounting billing method and device. The method includes the following steps that: after the authentication of a user succeeds, a broadband remote access server (BRAS) obtains locally-stored bill information for the user, wherein the bill information contains consumed traffic or online duration of offline users which is calculated by the BRAS in an AAA (authentication-authorization-accounting server) inaccessible period; and an accounting message carrying the bill information is sent to the AAA server, so that the AAA server can perform deduction for the user according to the bill information. According to the accounting method and device provided by the embodiments of the invention, after online authentication of the user succeeds, the accounting message carrying the bill information is sent to the AAA server immediately, and therefore, the times sequence problem of the uploading and analysis of the bill information, and the going online again of the user can be avoided, and the AAA server can immediately perform deduction according to the bill information.

Owner:NEW H3C TECH CO LTD

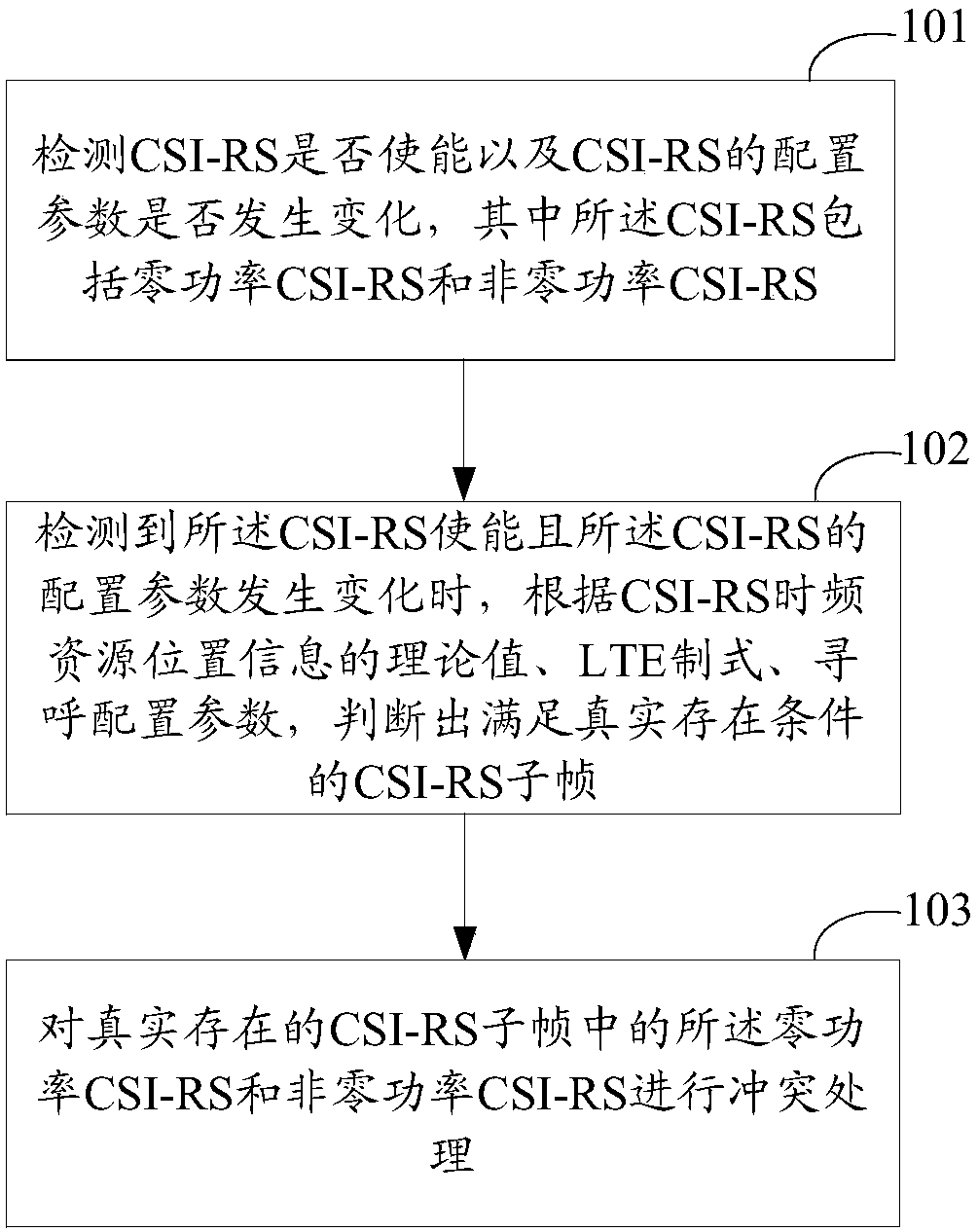

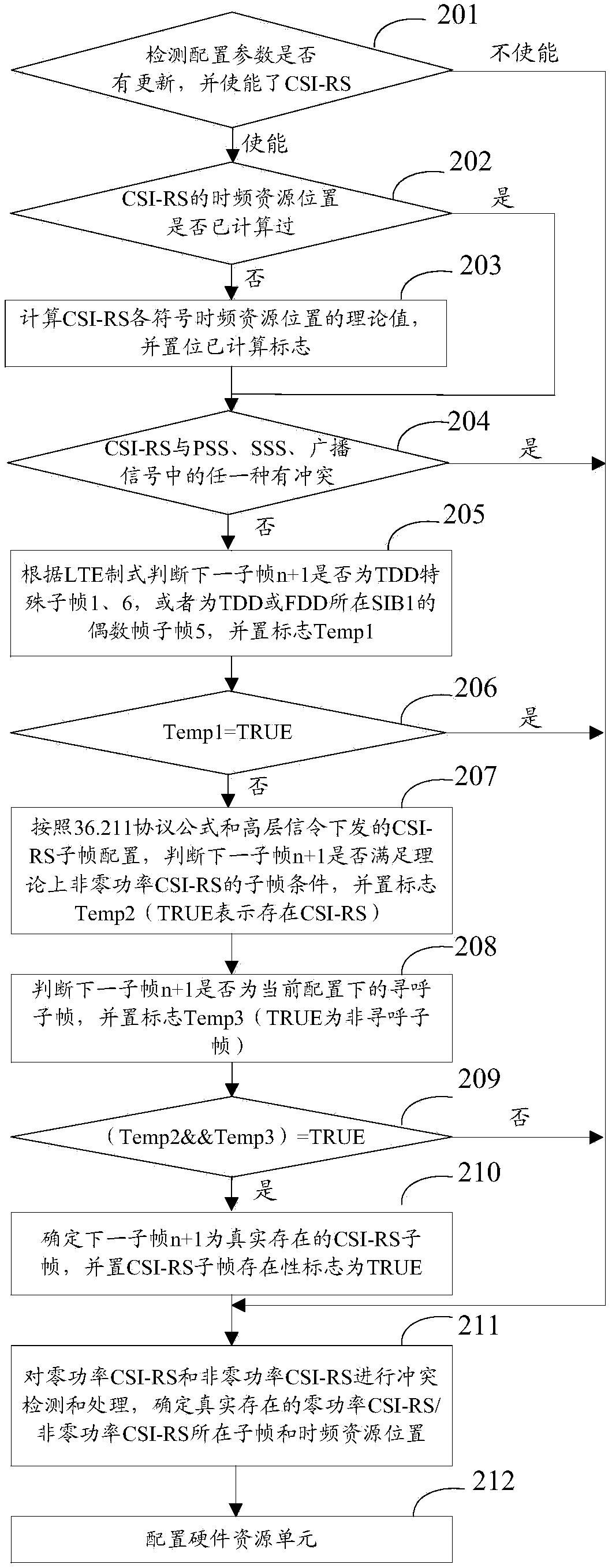

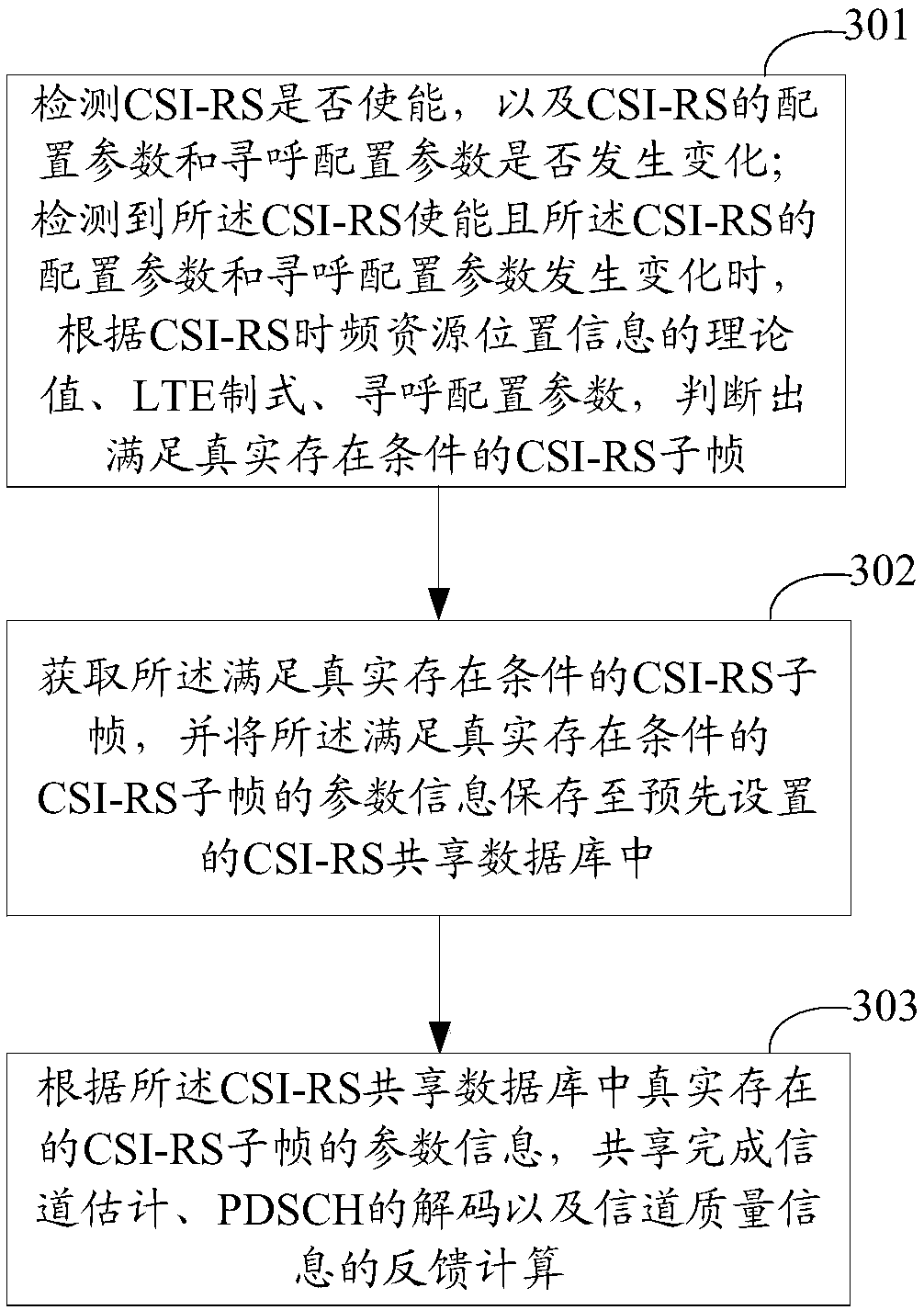

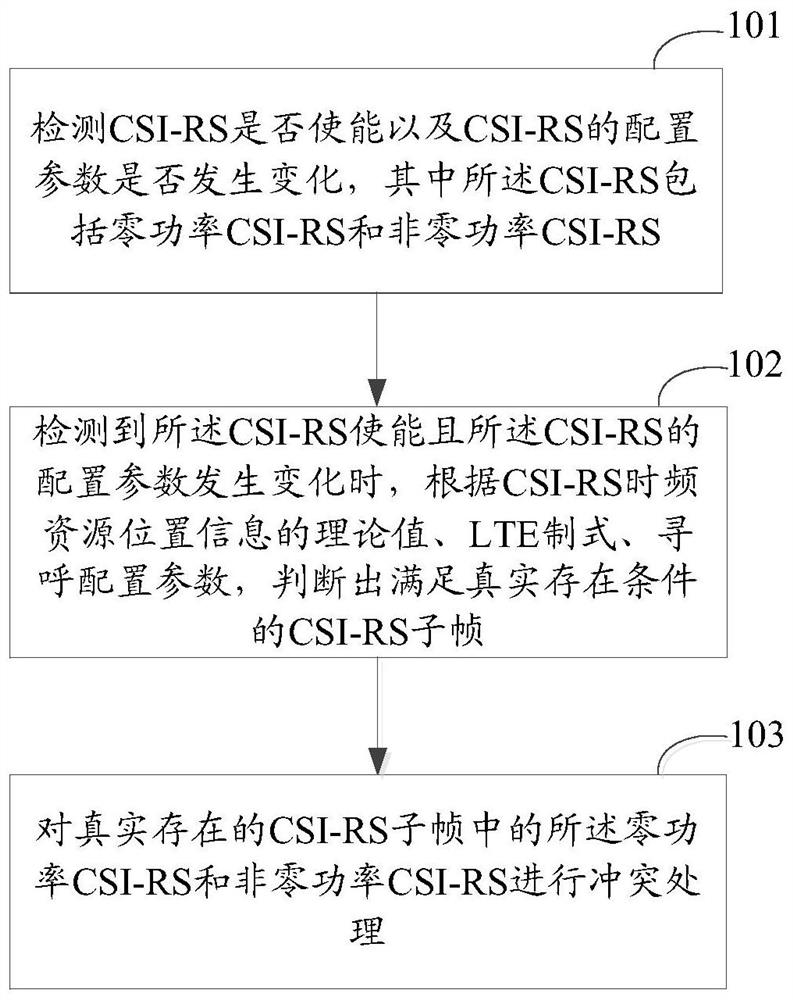

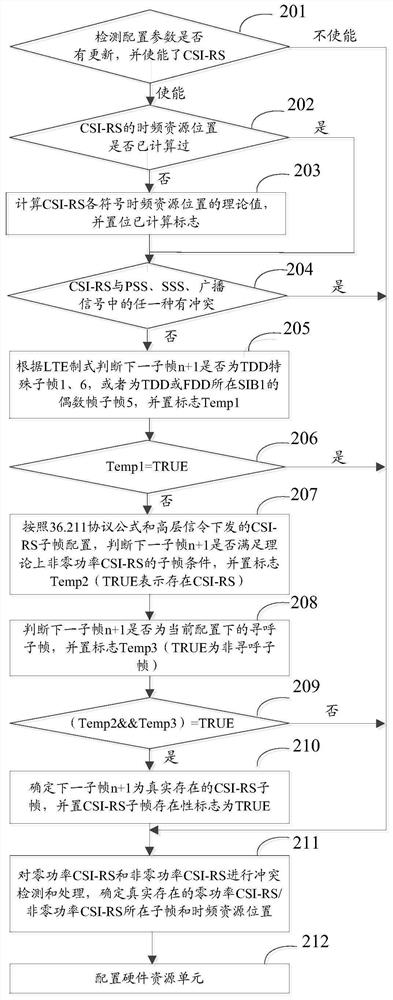

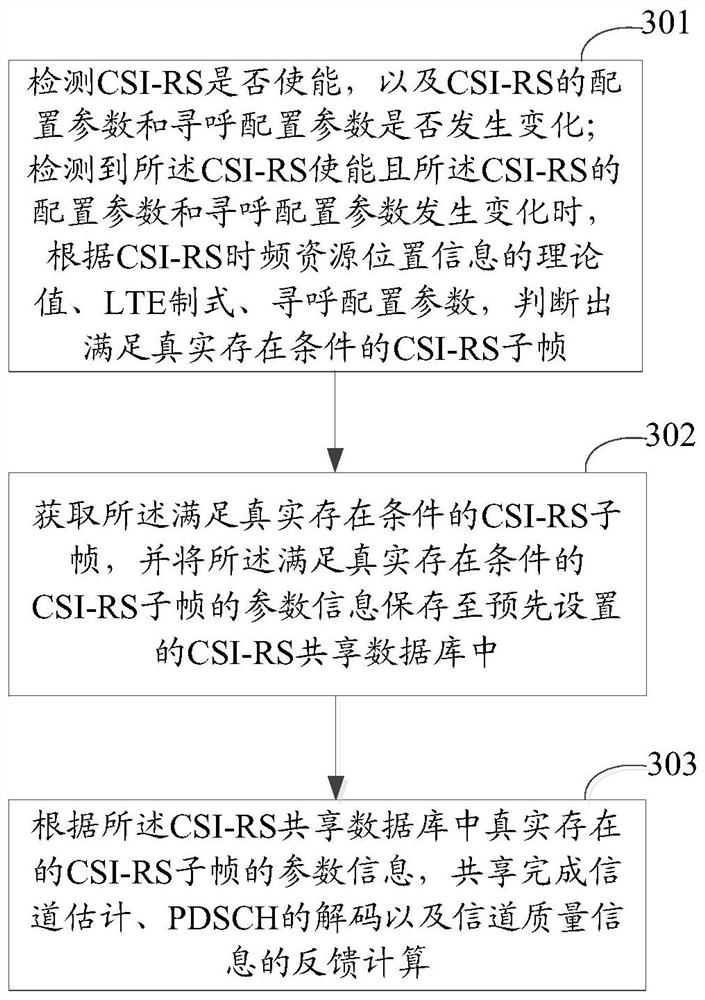

Channel state information reference signal processing method and device

ActiveCN108668300AAvoid calculationAccurate judgmentPilot signal allocationWireless communicationRSSChannel state information

The invention discloses a channel state information reference signal (CSI-RS) processing method. The method comprises the steps of detecting whether CSI-RSs are enabled or not and whether configuration parameters of the CSI-RSs are changed or not, wherein the CSI-RSs comprises a zero power CSI-RS and a non-zero power CSI-RS; judging CSI-RS subframes which satisfy a real existence condition according to a theoretical value of CSI-RS time-frequency resource location information, a long term evolution (LTE) system and a paging configuration parameter, when it is detected that the CSI-RSs are enabled and the configuration parameters of the CSI-RSs are changed; and carrying out conflict processing on the zero power CSI-RS and the non-zero power CSI-RS in the really existing CSI-RS subframes. The invention also discloses a CSI-RS processing device.

Owner:SANECHIPS TECH CO LTD

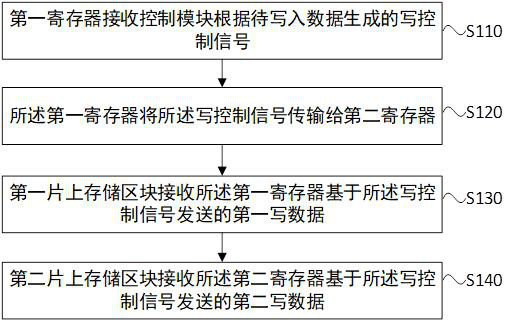

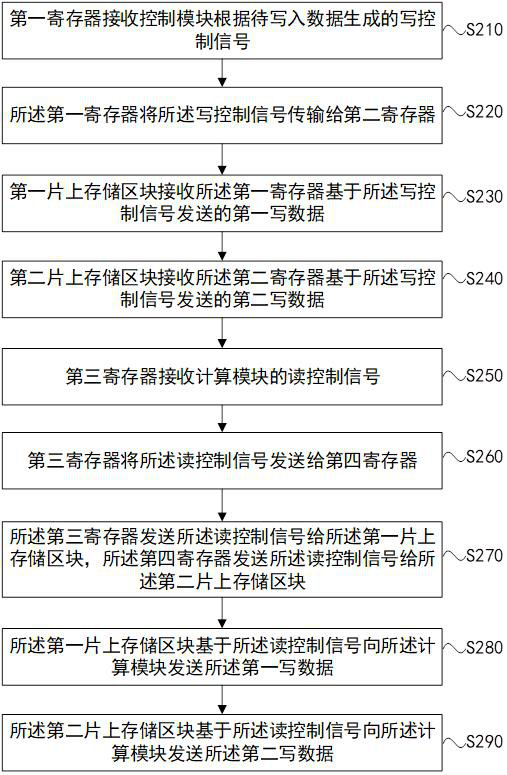

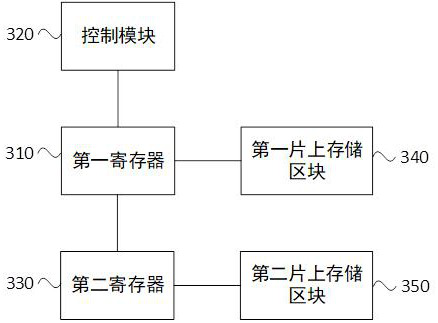

Control method and system for data transmission of data flow architecture neural network chip

PendingCN111860821AImprove chip performanceSave resourcesNeural architecturesPhysical realisationEmbedded systemData transmission

The embodiment of the invention discloses a control method and system for data transmission of a data flow architecture neural network chip. The method comprises the steps that a first register receives a write control signal generated by a control module according to-be-written data; the first register transmits the write control signal to a second register; a first on-chip storage block receivesfirst write data sent by the first register based on the write control signal; and a second on-chip storage block receives second write data sent by a second register based on the write control signal. According to the embodiment of the invention, the time sequence problem caused by control signal fan-out on the neural network chip based on data flow architecture design is solved, and the chip performance is improved.

Owner:SHENZHEN CORERAIN TECH CO LTD

A rs coding system based on cmmb and its realization method

ActiveCN103001736BSave internal resourcesReduce computationError preventionInternal memoryComputer architecture

The invention discloses a CMMB (China mobile multimedia broadcasting) based RS (reed-solomon) coding system and an implementing method thereof. The CMMB based RS coding system comprises an SDRAM (synchronous dynamic random access memory) controller, a byte interleaver, an internal memory and an RS coder, wherein the SDRAM controller is used for receiving information code streams and storing accessing check codes, the byte interleaver is used for subjecting accessing information codes and the check codes to byte interleaving, the internal memory is used for caching the accessing information codes and the check codes, and the RS coder is used for coding the information codes. The implementing method includes that the SDRAM controller receives the information code streams, the information codes are subjected to byte interleaving by the byte interleaver, the information codes interleaved are stored in the internal memory and are read and encoded and the like. By the CMMB based RS coding system and the implementing method thereof, internal resources of an FPGA (field programmable gate array) is effectively saved, and operation load is reduced, so that the problem about time sequence of the FPGA is solved, the low-end FPGA can be utilized for design, and normal work in complicated environment can be guaranteed.

Owner:ALLWIN TELECOMM

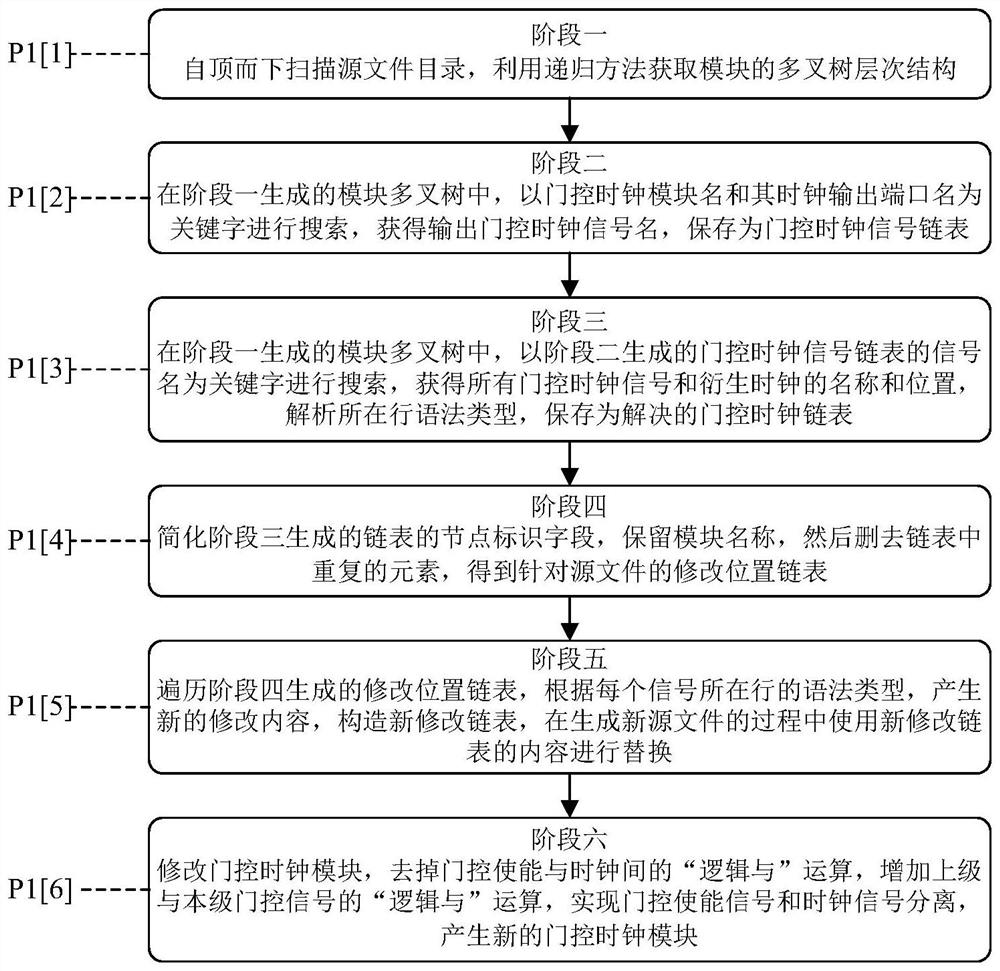

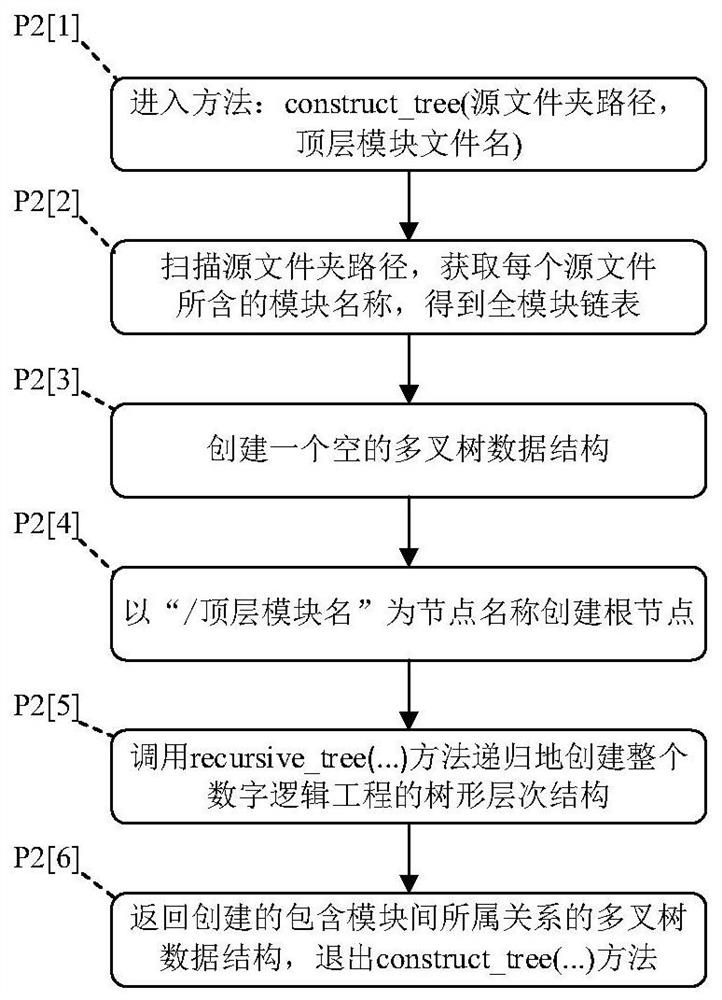

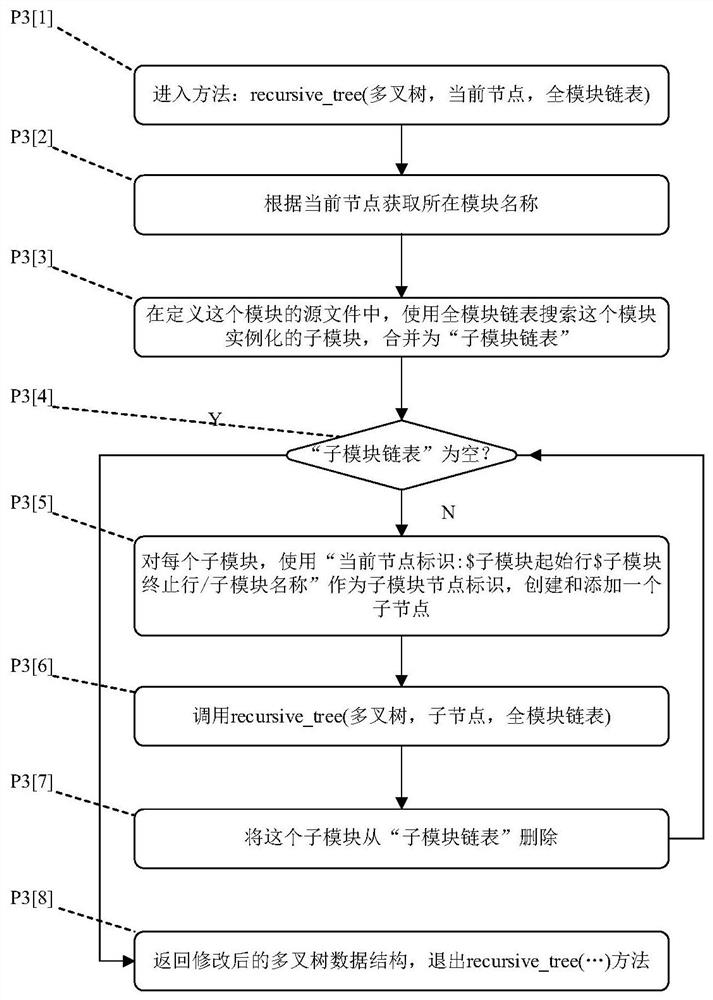

Gated clock conversion method based on recursive multi-way tree

ActiveCN112364579AShorten the timeFix timing issuesCAD circuit designEnergy efficient computingComputer architectureLogisim

The invention discloses a gated clock conversion method based on a recursive multi-way tree. The gated clock conversion method comprises the following steps: 1, acquiring a multi-way tree hierarchicalstructure of a module; 2, searching a gated clock module name and a clock output port name of the gated clock module to obtain a gated clock signal chain table; 3, searching a signal name of the gated clock signal linked list, obtaining names and positions of a gated clock signal and a derivative clock, analyzing the grammar type of the row, and storing the grammar type as a solved gated clock linked list; 4, simplifying linked list node identification fields, reserving module names, and deleting linked list repetitive elements to obtain a modified position linked list; 5, according to the grammar type of the modified position linked list signal, constructing a new modified linked list from the new modified content and replacing the new modified linked list; and 6, removing logic AND operation between the gating enable and the clock, and adding logic AND operation of the upper-level gating signal and the current-level gating signal. Platform verification of large-scale digital logic containing a gated clock becomes possible, and the method can be widely applied to the technical field of integrated circuit design.

Owner:武汉凌久微电子有限公司

Storage module test method and system

The invention discloses a storage module testing method and system, belonging to the technical field of communication. The present invention judges the information of acquiring the data signal of the storage module to be tested, so as to avoid timing problems, and further performs read and write operations on the storage module to be tested, obtains the window position information of the data signal, and adjusts the sampling clock to maximize the effective window of the data signal. Therefore, the purpose of automatically and quickly testing the storage module is improved, and the testing efficiency is improved.

Owner:AMOLOGIC (SHANGHAI) CO LTD

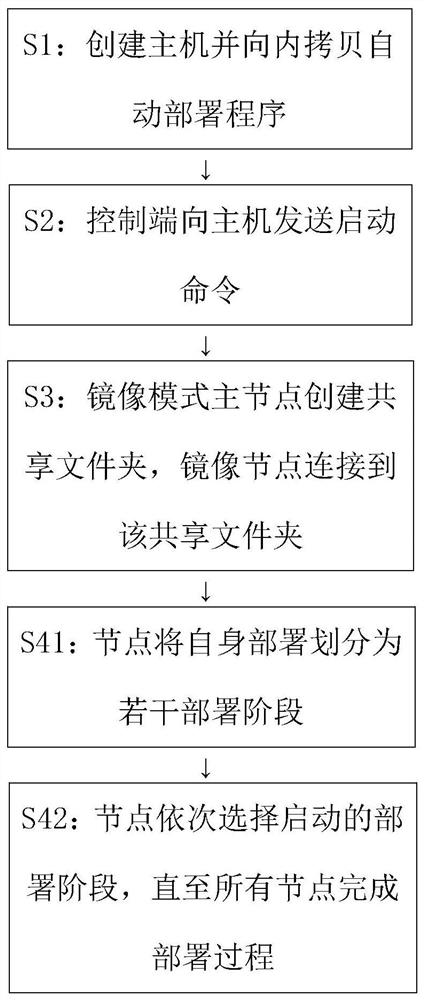

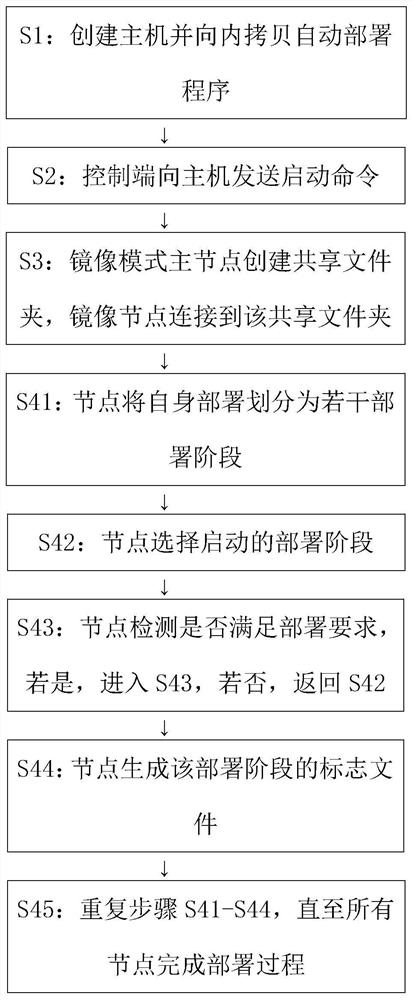

A method for automatic deployment of SQL Server database mirroring mode

ActiveCN107391640BImprove experienceSolve the cumbersome problem of data exchangeDatabase management systemsSpecial data processing applicationsStreaming dataQuality of service

The invention provides a method for achieving automatic deployment of a mirror mode of the SQL server database. According to the method, the file sharing function of Windows is used to communicate data among each node, so that automatic deployment of the mirror mode of the SQL server database is achieved. By means of the method, the problem that data communication among each node is tedious is solved, deployment time is reduced, the deployment efficiency is improved, and the service quality and user experience are promoted.

Owner:SHANDONG LANGCHAO YUNTOU INFORMATION TECH CO LTD

Method and device for processing channel state information reference signal

ActiveCN108668300BAvoid calculationAccurate judgmentPilot signal allocationWireless communicationChannel state informationTelecommunications

The invention discloses a channel state information reference signal (CSI-RS) processing method, including: detecting whether the CSI-RS is enabled and whether the configuration parameters of the CSI-RS are changed, wherein the CSI-RS includes zero-power CSI -RS and non-zero-power CSI-RS; when it is detected that the CSI-RS is enabled and the configuration parameters of the CSI-RS change, according to the theoretical value of the CSI-RS time-frequency resource location information, the long-term evolution (LTE) System, paging configuration parameters, determine the CSI-RS subframe that meets the real existence condition; perform collision processing on the zero-power CSI-RS and non-zero-power CSI-RS in the real CSI-RS subframe. The invention also discloses a CSI-RS processing device at the same time.

Owner:SANECHIPS TECH CO LTD

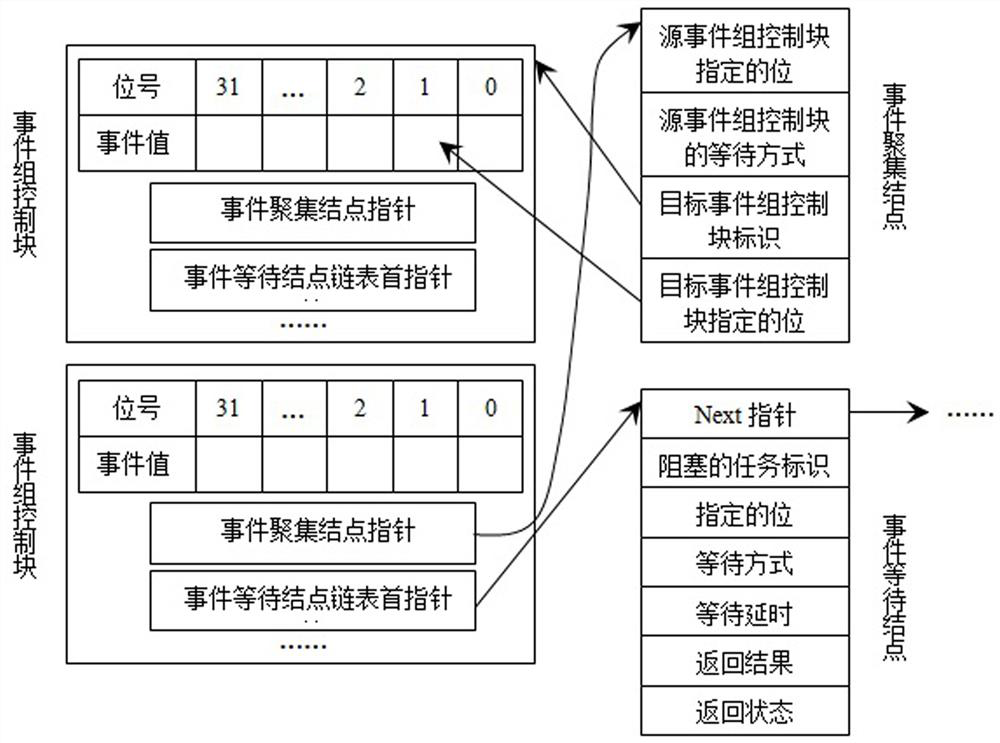

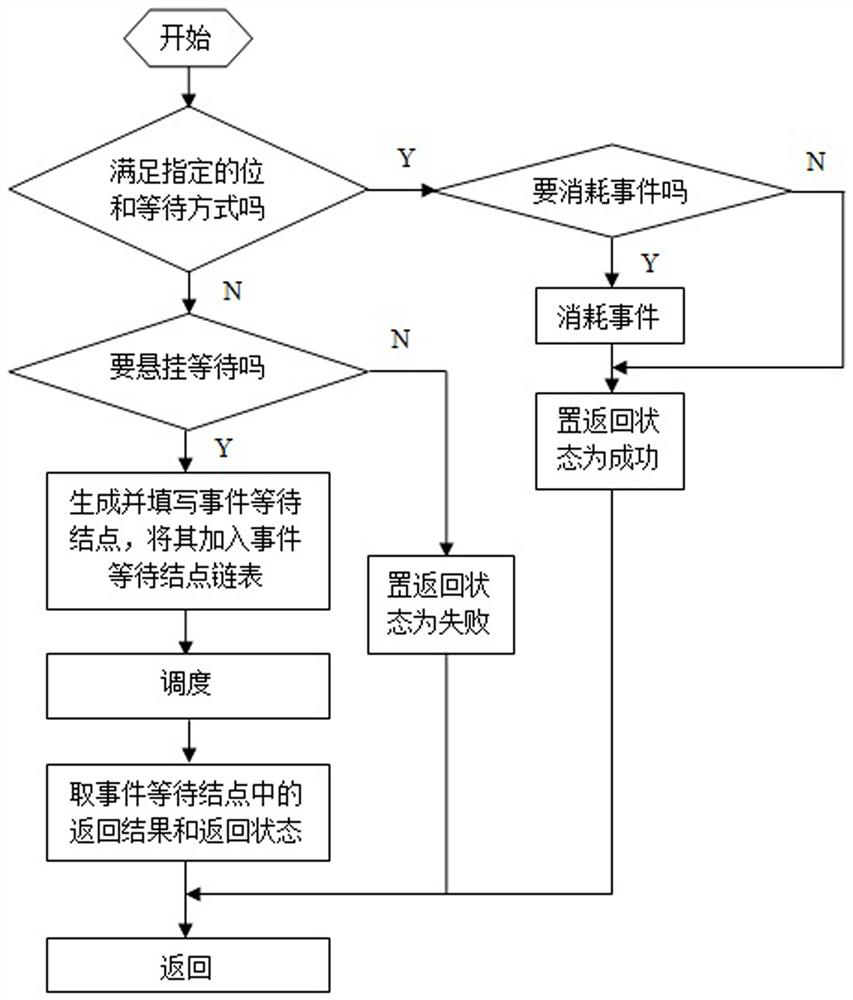

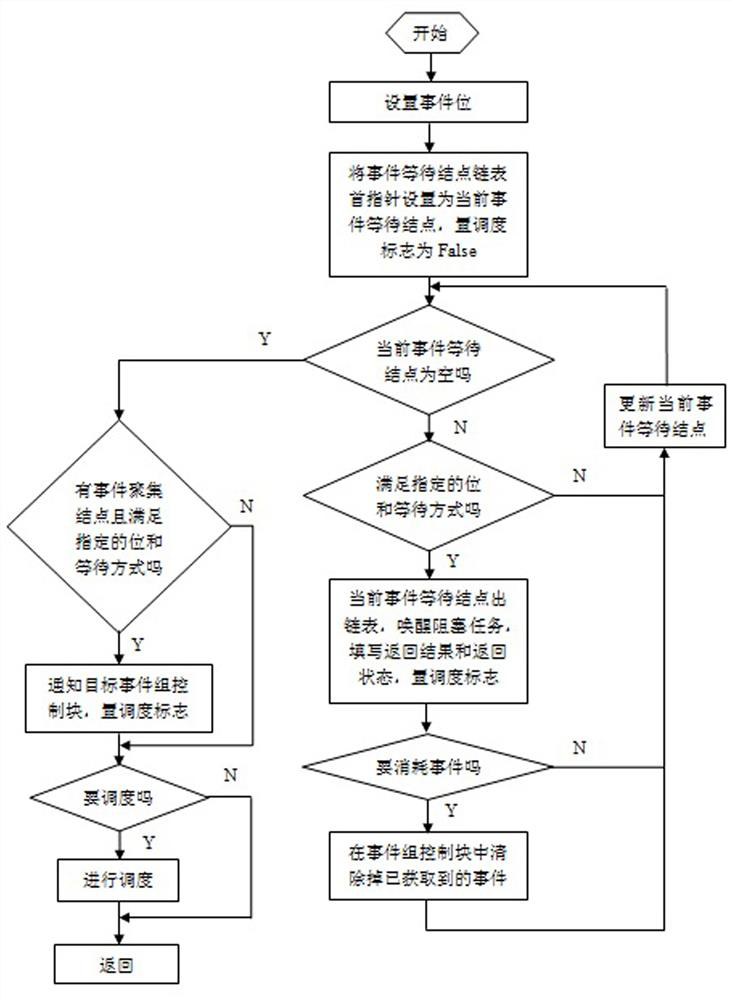

Event Processing Method of Real-Time Embedded Operating System

ActiveCN108009015BChoose accuratelyIncrease the number ofProgram initiation/switchingProgram synchronisationEmbedded operating systemProcessing

The invention is an event processing method of a real-time embedded operating system. Including three basic operations of creating event group control block, getting event and sending event. When sending an event, if the wait method in the event waiting node specifies the consumption event flag, the acquired event will be immediately cleared in the event value of the event group control block, and the update will be used in the processing of the next event waiting node The event value of the subsequent event group control block. The event group control block is divided into source event group control block and target event group control block. The target event group control block aggregates the source event group control block by associating an event aggregation node with the source event group control block, so as to expand the number of event group control blocks that the task can use at the same time.

Owner:烟台大学文经学院

A method and system for real-time detection of welding defects based on high-frequency time-series data

ActiveCN113870260BFix timing issuesIncrease training speedImage enhancementImage analysisAlgorithmNetwork structure

The invention discloses a method and system for real-time detection of welding defects based on high-frequency time-series data. The detection method includes: first sampling the collected high-frequency welding time-series data according to a set window length, and marking each sample Defect occurrence time period and defect type to generate a data sample set; then use the generated data sample set to train the ResNet and TCN fusion network model to obtain a trained detection model; finally obtain new real-time high-frequency welding data, according to the set window length Input it into the trained detection model for prediction, and output the welding defect category in real time. The present invention can apply ResNet to the field of timing detection by combining the network structure of the ResNet network and the TCN, aiming at the high-frequency welding timing data with a large amount of data and a long sequence length, through parallel convolution calculation, in the training process In the process, the training speed is accelerated, and in the prediction process, strong real-time prediction is achieved.

Owner:苏芯物联技术(南京)有限公司

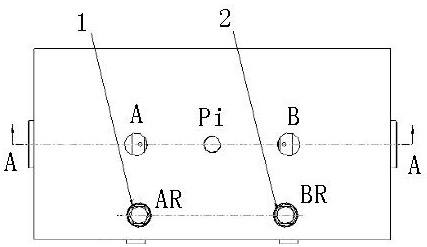

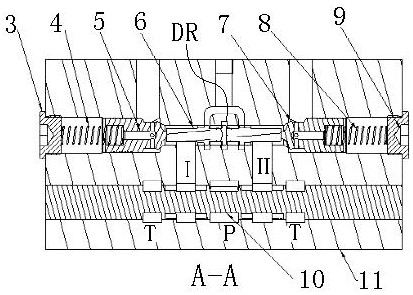

Oil path structure of embedded multifunctional two-way holding valve

PendingCN114183429AImprove stabilityImprove comfortServomotor componentsMultiple way valvesMarine engineeringMechanical engineering

The invention discloses an embedded multifunctional two-way holding valve oil way structure, and belongs to the technical field of hydraulic valves. A main valve rod is installed in the first valve element hole of the valve body in a matched mode. A left one-way valve element, a linkage valve rod and a right one-way valve element are sequentially installed in a second valve element hole of the valve body. The oil port P and the oil port T are communicated to the main valve rod; the oil port A is communicated with a left one-way valve core and a spring cavity thereof; the oil port B is communicated with a right one-way valve core and a spring cavity thereof; the oil port Pi and the oil port DR are communicated through a linkage valve rod; the other end of the oil duct I is communicated with the right end of the left one-way valve core and the left end of the linkage valve rod; and the other end of the oil duct II is communicated with the left end of the right one-way valve core and the right end of the linkage valve rod. The linkage valve rod has the function of linkage of the executing mechanism and the function of pressure selection, soft opening and soft braking of the executing mechanism are achieved, the impact of opening and closing of the executing mechanism is avoided, the operation stability of the executing mechanism is improved, and the operation comfort is improved.

Owner:徐州阿马凯液压技术有限公司

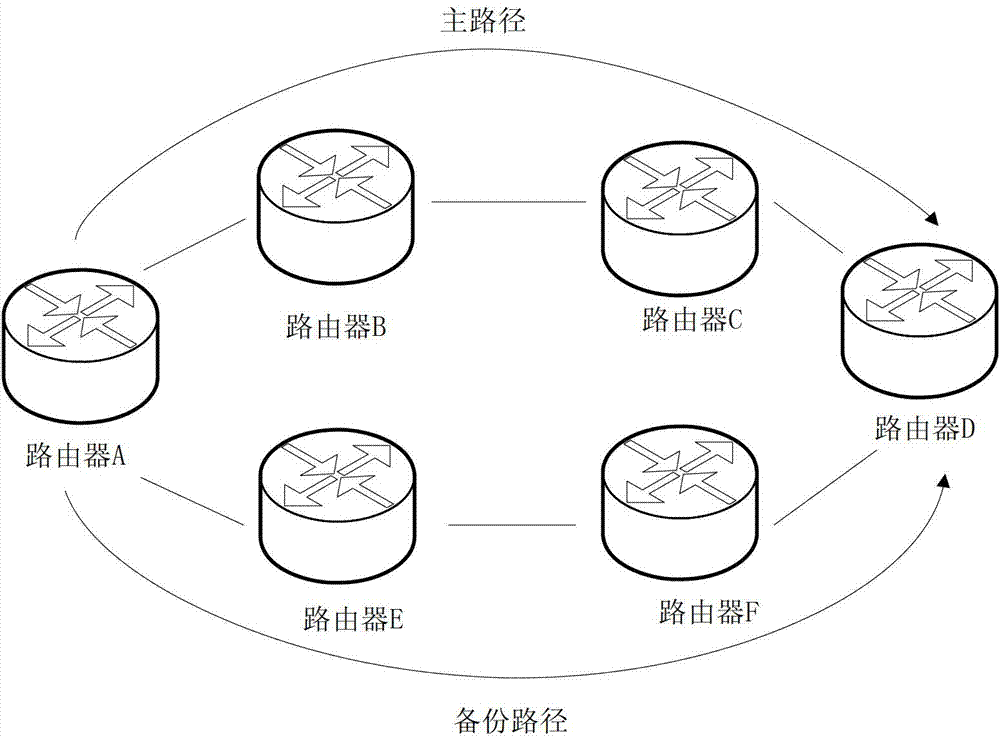

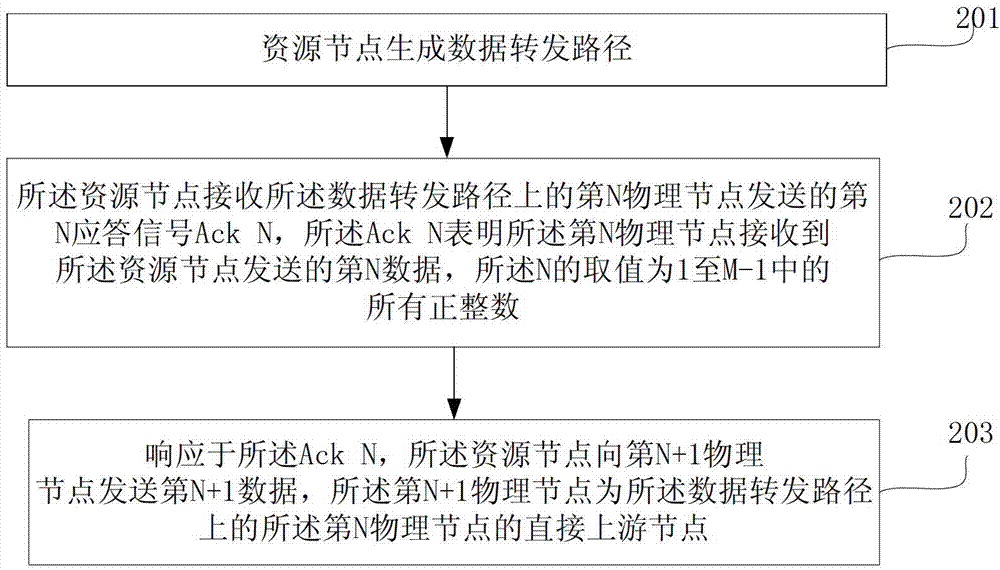

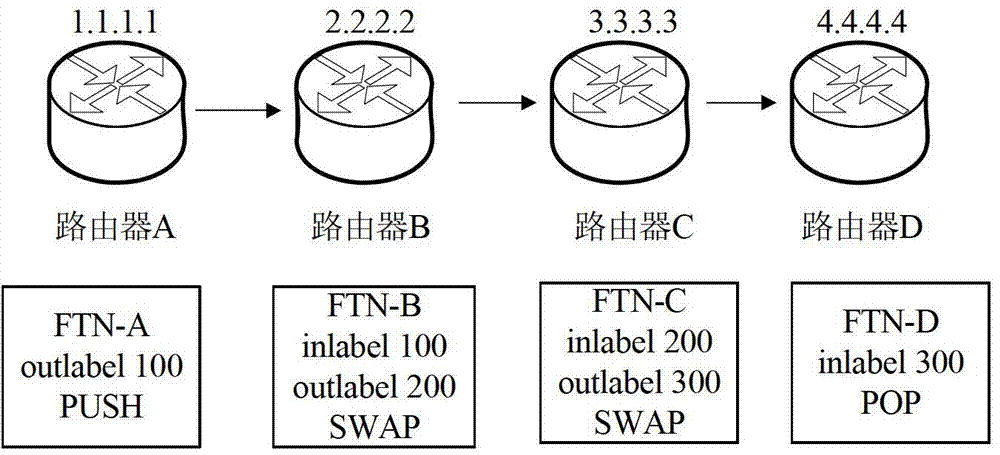

Data forwarding method and device

ActiveCN103534990AFix timing issuesNo packet lossHybrid transportNetworking protocolDistributed computing

The invention relates to a data forwarding method and device. The method comprises: a resource node generates a data forwarding path; the data forwarding path comprises M physical nodes, wherein M is a positive integer which is greater than one; the resource node receives an N-th answering signal Ack N transmitted by an N-th physical node on the data forwarding path, wherein the Ack N indicates that the N-th physical node receivs the N-th data transmitted by the resource node, and N is a positive integer which is located between one and M-1; and responding to the Ack N, the resource node transmits the (N+1)-th data to an (N+1)-th physical node which is a direct upstream node of the N-th physical node on the data forwarding path. The method and the device can solve a problem of the time sequence of the forwarding of table data of various physical data, thereby guaranteeing that a packet cannot be lost, needing no employment of additional networking protocol, and increasing no cost.

Owner:HUAWEI TECH CO LTD

A kind of SDN multi-thread timing control method, system, device and readable storage medium

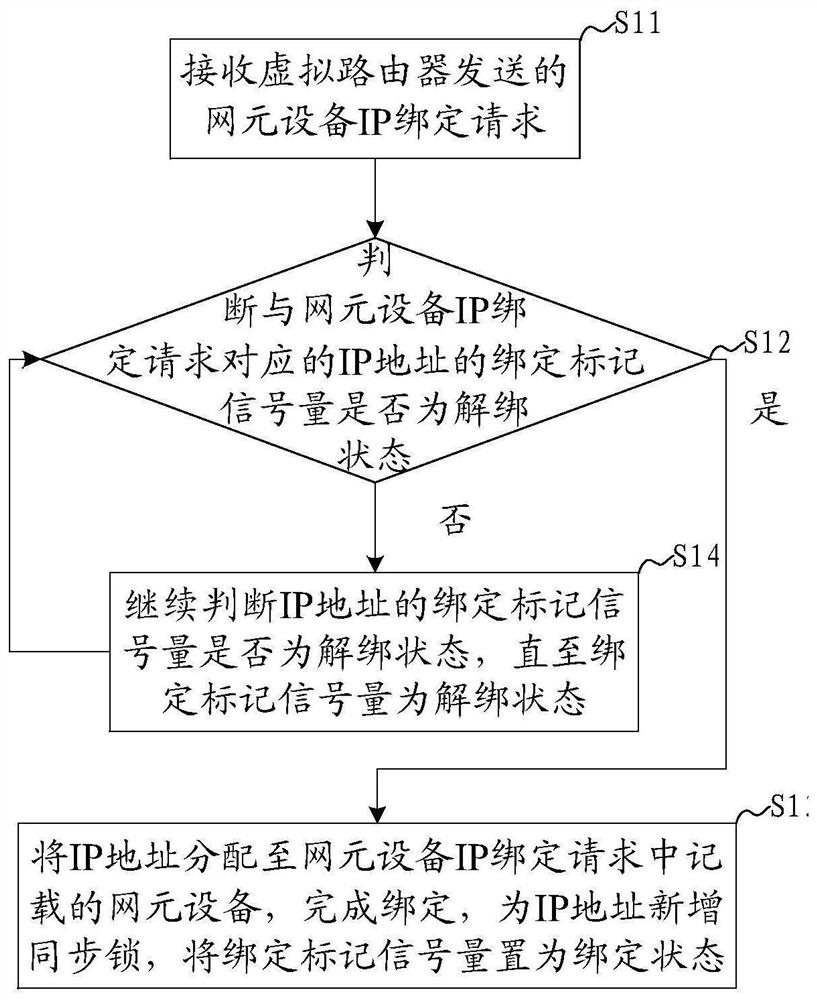

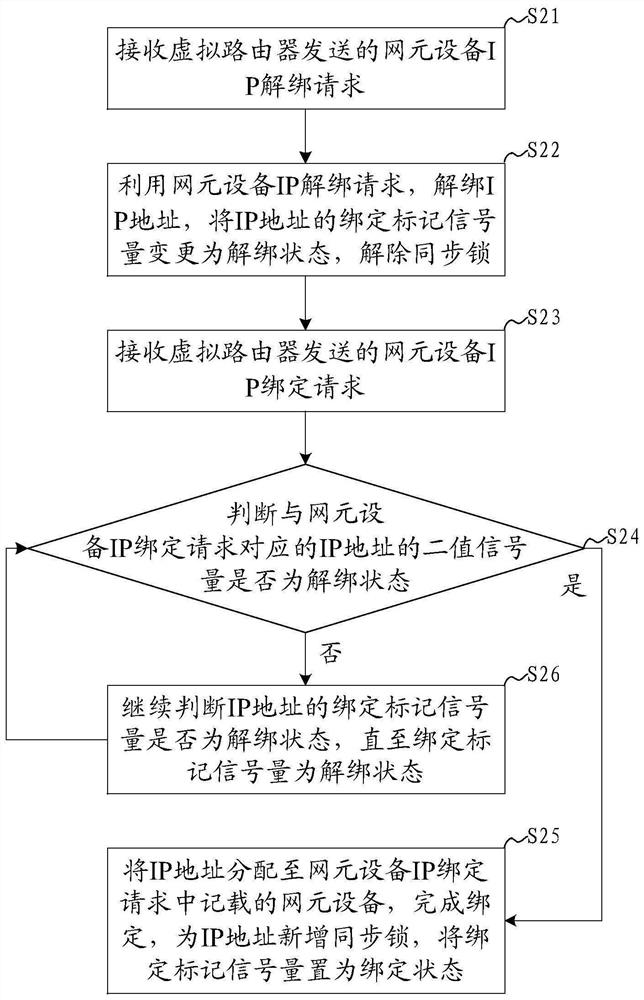

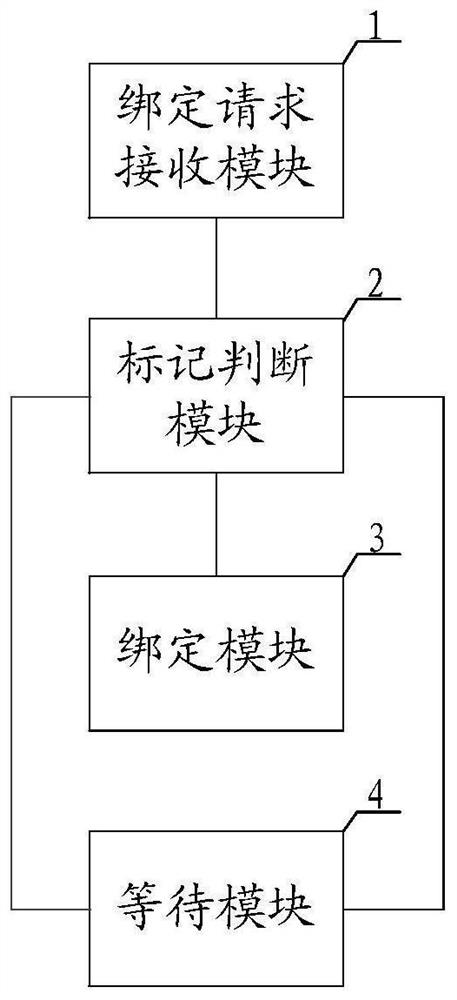

The present application discloses an SDN multi-thread timing control method, system, device and computer-readable storage medium, comprising: receiving a network element device IP binding request sent by a virtual router; judging an IP corresponding to the network element device IP binding request Whether the binding tag semaphore of the address is in the unbound state; if the binding tag semaphore is in the unbound state, the IP address is allocated to the network element device recorded in the IP binding request of the network element device to complete the binding; If the fixed marked semaphore is not in the unbound state, continue to judge whether the bound marked semaphore of the IP address is in the unbound state; this application adds a binding marked semaphore for the IP address in advance for processing the IP binding of the network element device. Determine the binding state of the IP address when requesting, and do not perform an incorrect binding operation when the binding flag semaphore is not in the unbound state, and perform the binding operation until the binding flag semaphore is in the unbound state to ensure that the network element equipment is in the unbound state. The IP binding request can be effectively executed, which solves the timing problem.

Owner:北京浪潮数据技术有限公司