A time sequence path correction method

A timing and path technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as the inability to optimize timing targets, achieve the effect of optimizing timing paths and ensuring normal operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

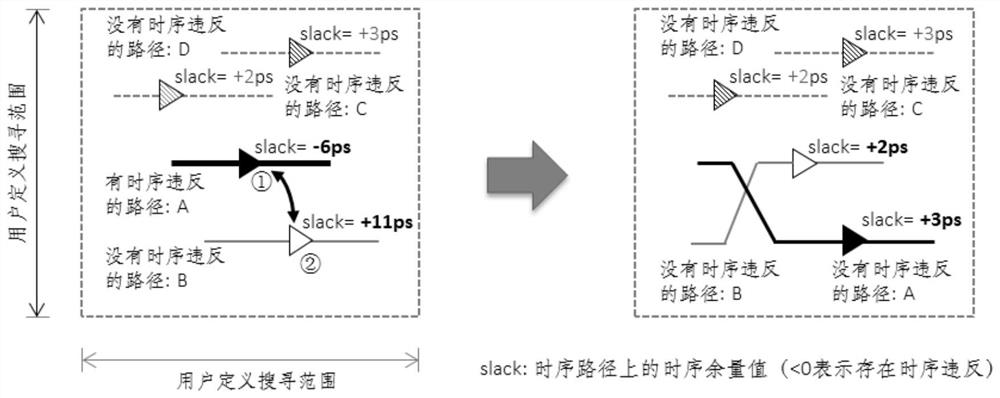

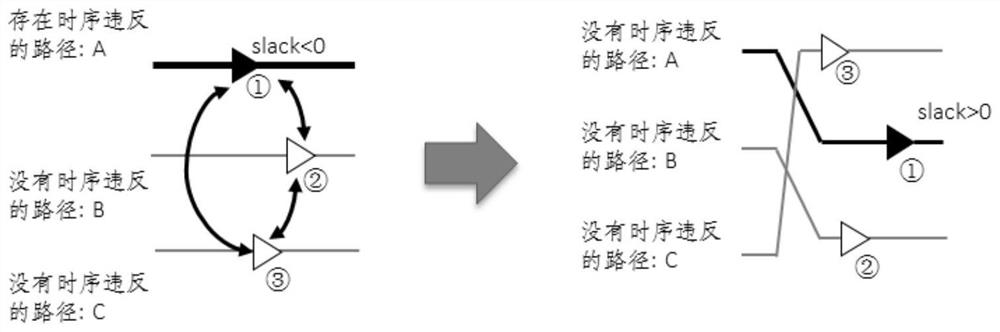

[0029] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

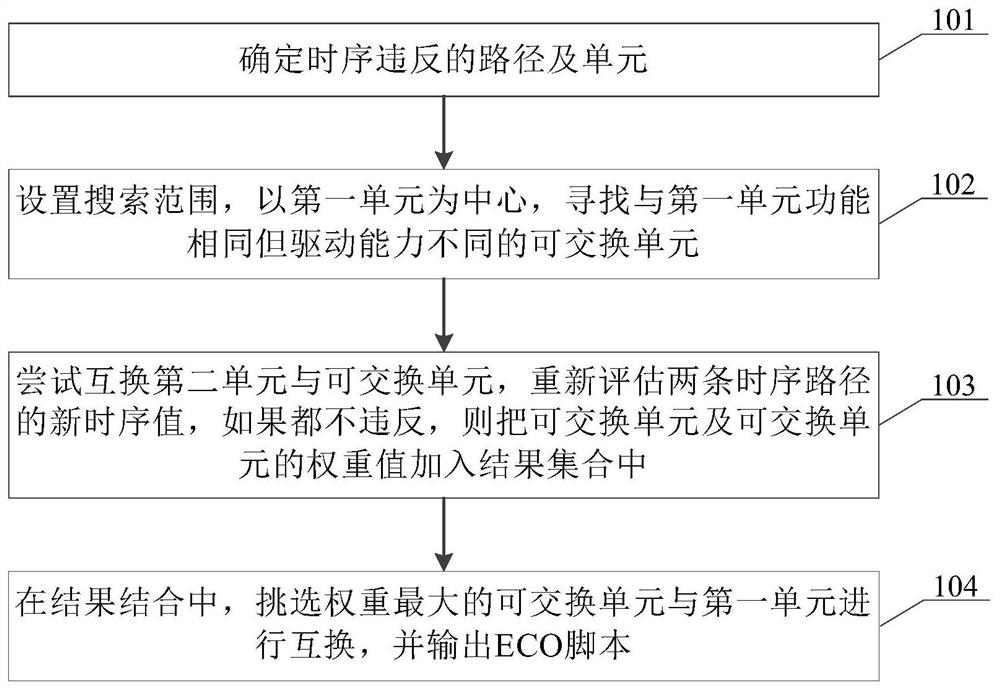

[0030] figure 1 It is a flow chart of the modification method of the timing path according to the present invention, and the following will refer to figure 1 , the method for modifying the timing path of the present invention is described in detail.

[0031] First, in step 101, determine the paths and units that violate timing.

[0032] Preferably, a timing path with a timing problem is determined, a unit that needs timing adjustment is found, and the unit type and physical location on the chip are obtained.

[0033] In this embodiment, it is assumed that the chip design enters the post-mask late stage, and it is no longer allowed to change the physical layout of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More