Patents

Literature

33results about How to "Save internal resources" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

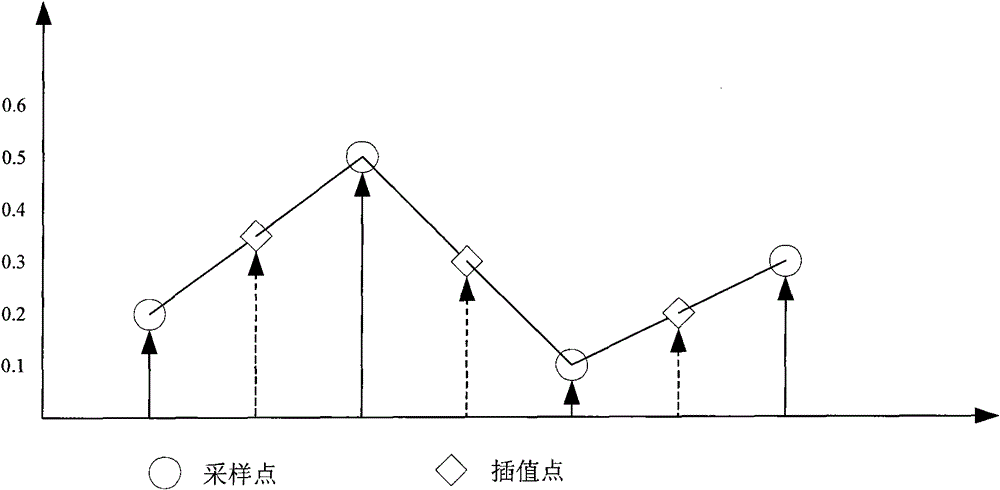

Digital oscilloscope capable of configuring multiplex digital interpolating and digital filtering functions

ActiveCN102109542AImprove waveform refresh rateSave internal resourcesDigital variable displayFpga implementationsDigital filter

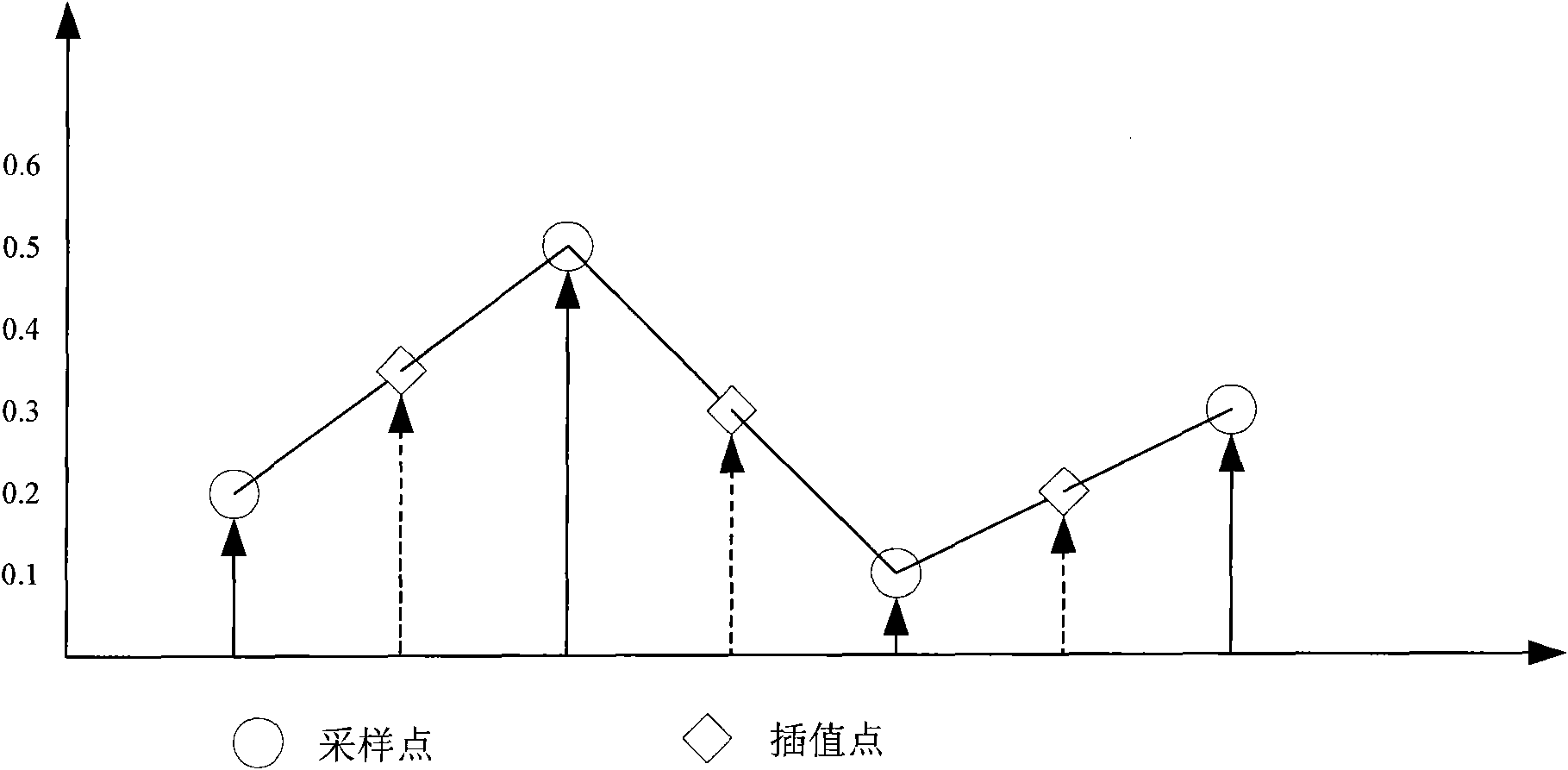

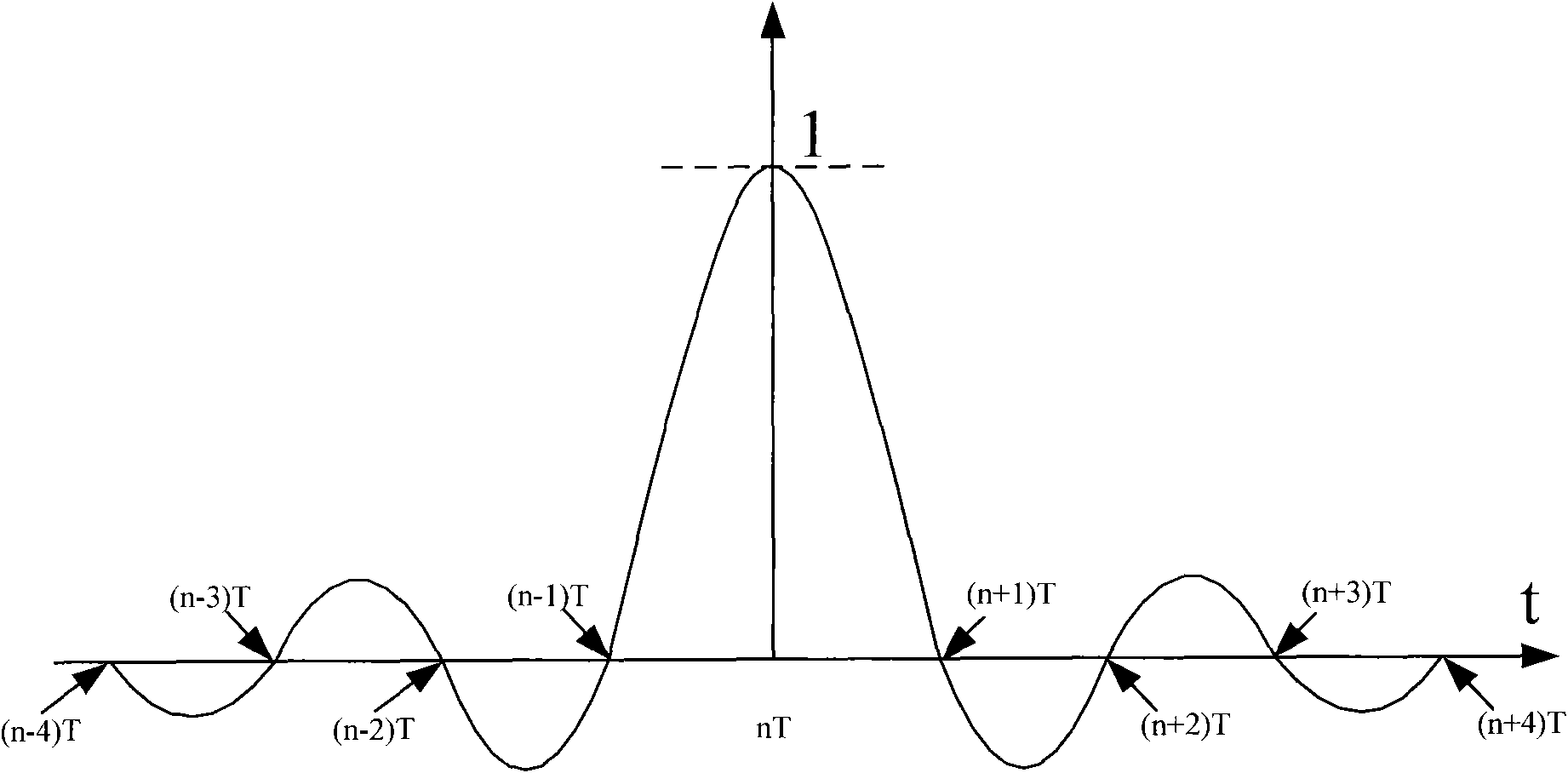

The invention discloses a digital oscilloscope capable of configuring multiplex digital interpolating and digital filtering functions. The digital oscilloscope comprises a digital interpolating and filtering module realized by an FPGA (field programmable gate array), wherein, the digital interpolating and filtering module determines the current operation mode according to an interpolating / filtering gating signal, receives and stores input data, transfers the delayed data and filtering coefficients into a multiply and accumulate (MAC) calculating unit for calculation, and then transfers calculated results into a subsequent calculating unit; the subsequent calculating unit decides whether accumulation is required according to the current operation mode; when the operation mode is digital interpolating operation, the calculated results are directly taken as interpolation results to be output; and when the operation mode is digital filtering operation, digital filtering operation results are output after accumulation. The digital oscilloscope combines two signal processing modes such as digital interpolating and digital filtering into one by means of multiplexing mode configuration, thus effectively saving internal resources of the FPGA and being very economical and efficient.

Owner:RIGOL

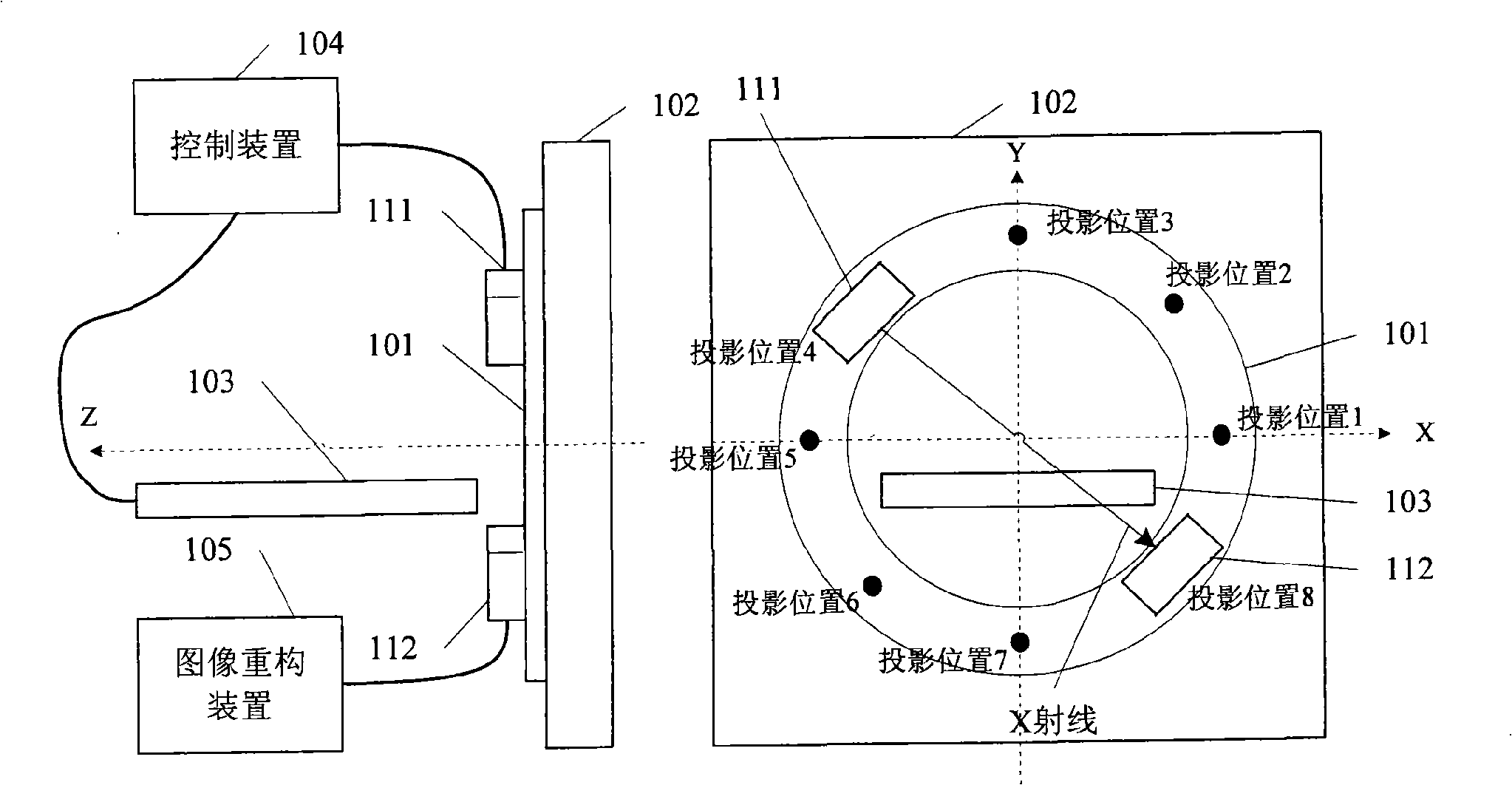

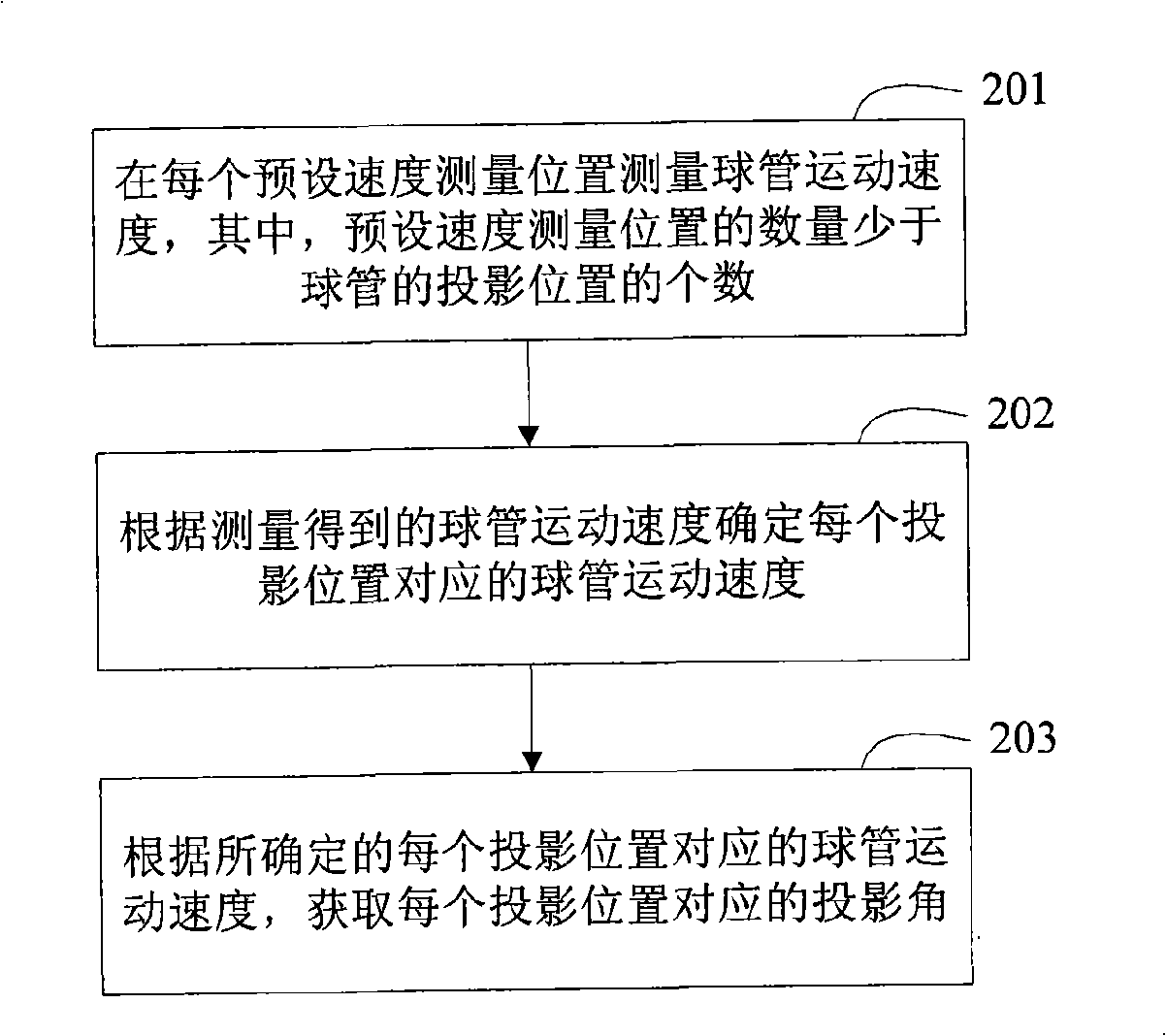

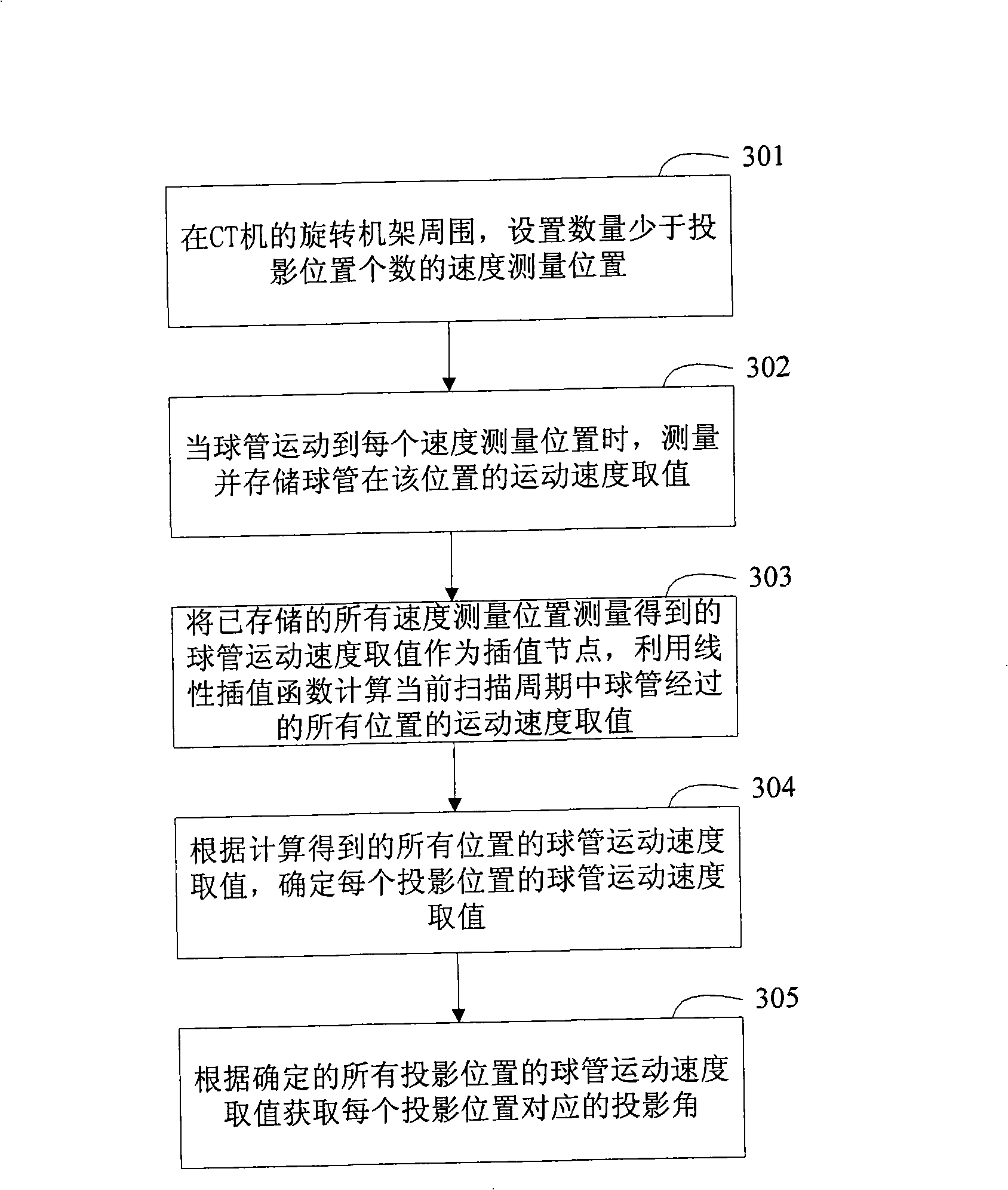

Method and apparatus for acquiring projected angle in image reconstruction

ActiveCN101327127AHigh precisionGuaranteed accuracyComputerised tomographsTomographyComputer graphics (images)Computer vision

The present invention discloses a projection angle acquisition method in the image reconstruction and a projection angle acquisition device for the image reconstruction. The present invention measures the moving speed of a bulb tube in the preset speed position of the moving track of the bulb tube, determines the moving speed of each projection position according to the measured moving speed of the bulb tube and acquires the corresponding projection angle of each projection position. Compared with the prior time-triggered scanning process, the present invention increases the accuracy of the projection angle; compared with the prior position-triggered scanning process, the present invention not only increases the accuracy of the projection angle but also reduces the realization cost. In addition, the moving speed of the bulb tube is premeasured and stored so as not to redetermine the speed of the projection position in each scanning process under the condition that the moving speed of the bulb tube has no great change, thus saving the internal resources of the CT machine; or the measurement of each scanning period further ensures the accuracy of the moving speed of each projection position, thus ensuring the accuracy of the projection angle.

Owner:SIEMENS SHANGHAI MEDICAL EQUIP LTD

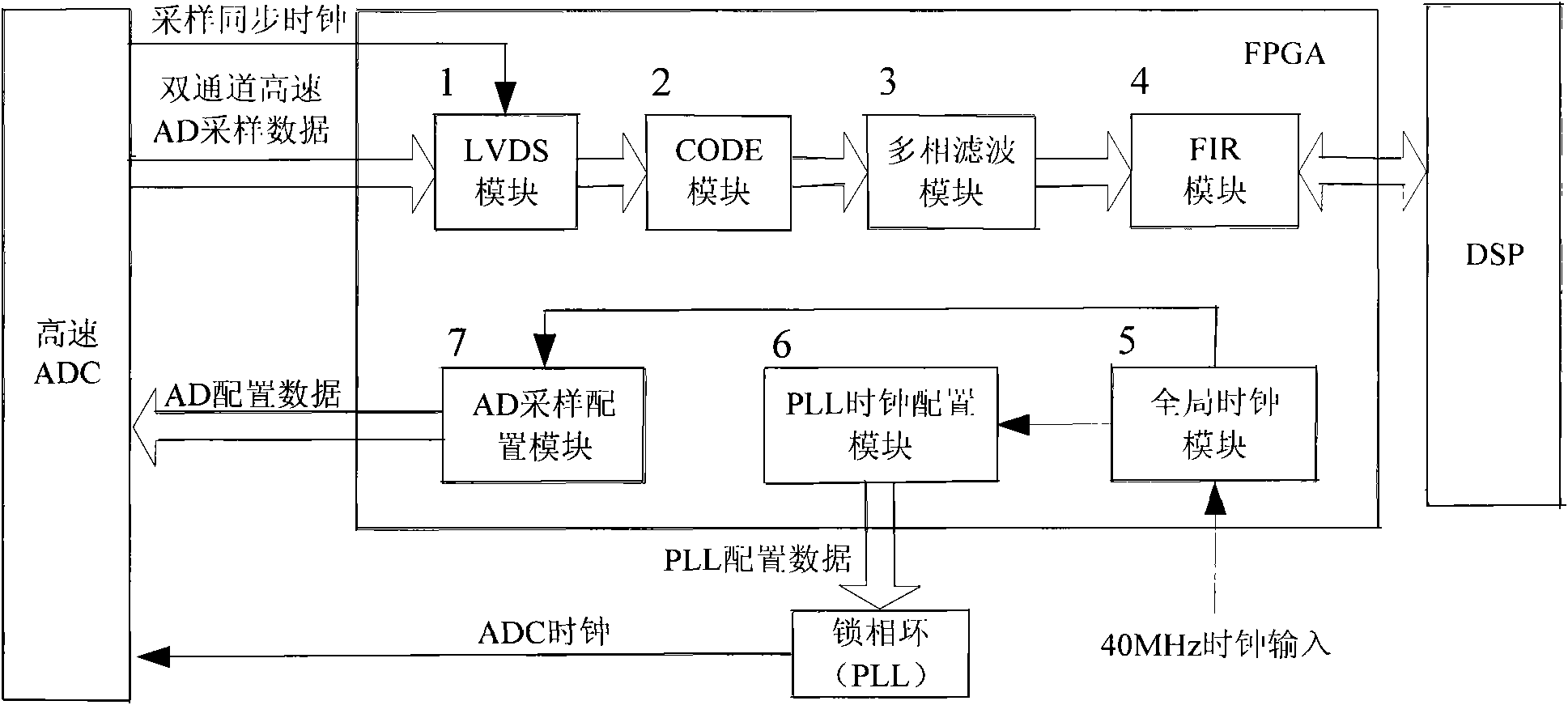

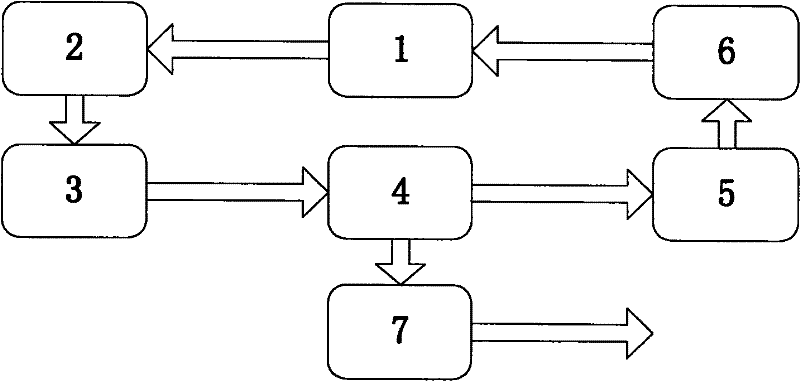

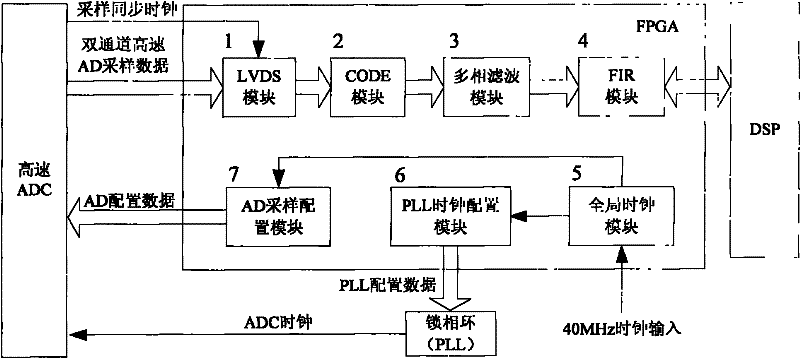

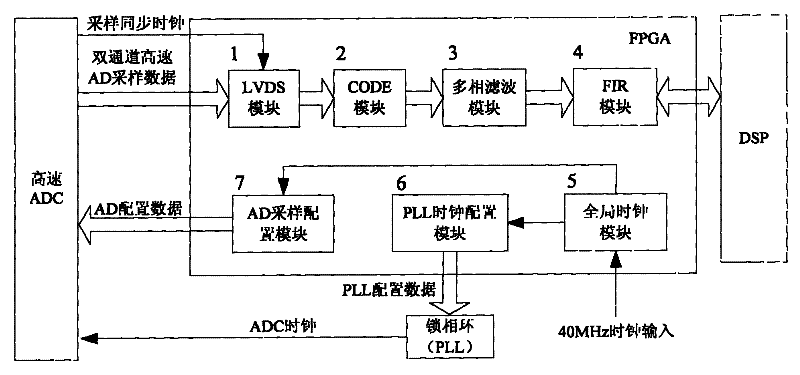

Broadband digital receiver suited for pulse compression signal

InactiveCN101571588ASave internal resourcesReduce power consumptionWave based measurement systemsCode moduleFpga implementations

The invention provides a broadband digital receiver suited for pulse compression signals, which comprises a high-speed A / D sampling module, FPGA, DSP, a global clock module, a PLL configuration module, an AD sampling configuration module and the like, wherein the FPGA comprises an LVDS module, a CODE module, a multiphase wave filtering module and an FIR wave filter module. The broadband digital receiver digitally receives the broadband signals, divides the signals in the frequency domain in a channelizing way, reduces the data transfer rate, and makes use of the FPGA to realize the suited receiving of the pulse compression signals. The DSP is responsible for the calculation and dynamic loading of the weight coefficient of the suited wave filter. Compared with the analogy method, the receiver has the characteristics of better equipment quantity and reliability, and high sensitivity and dynamic loading.

Owner:HARBIN ENG UNIV

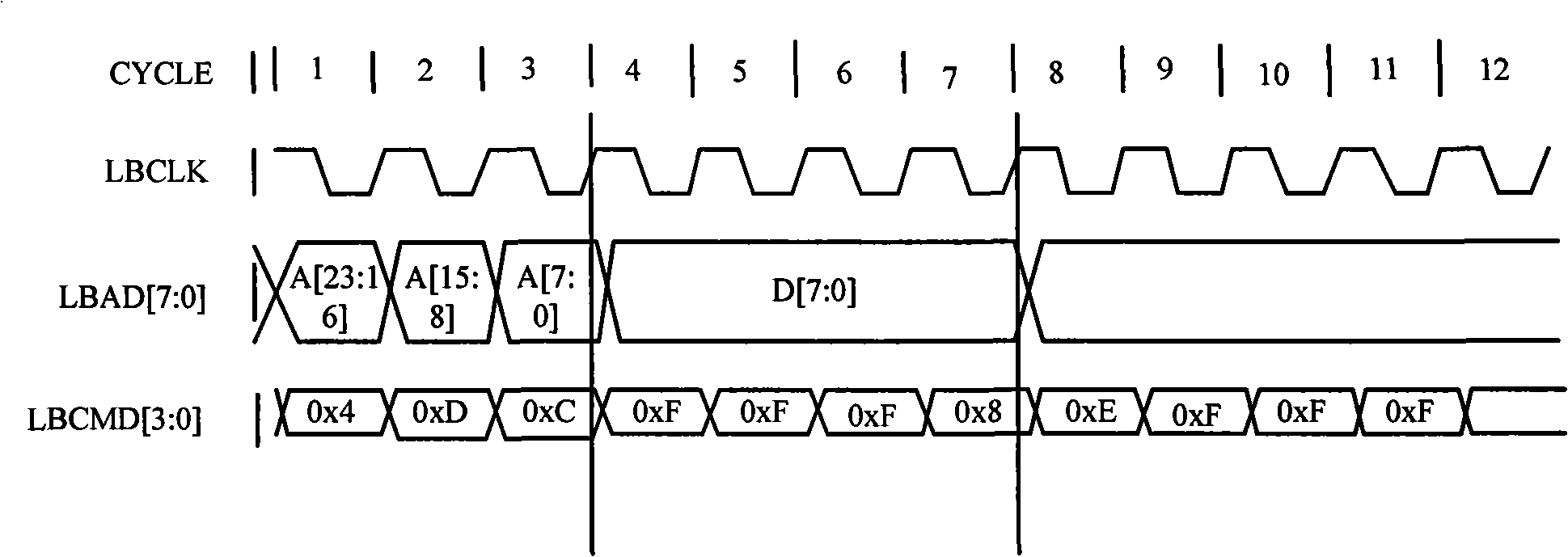

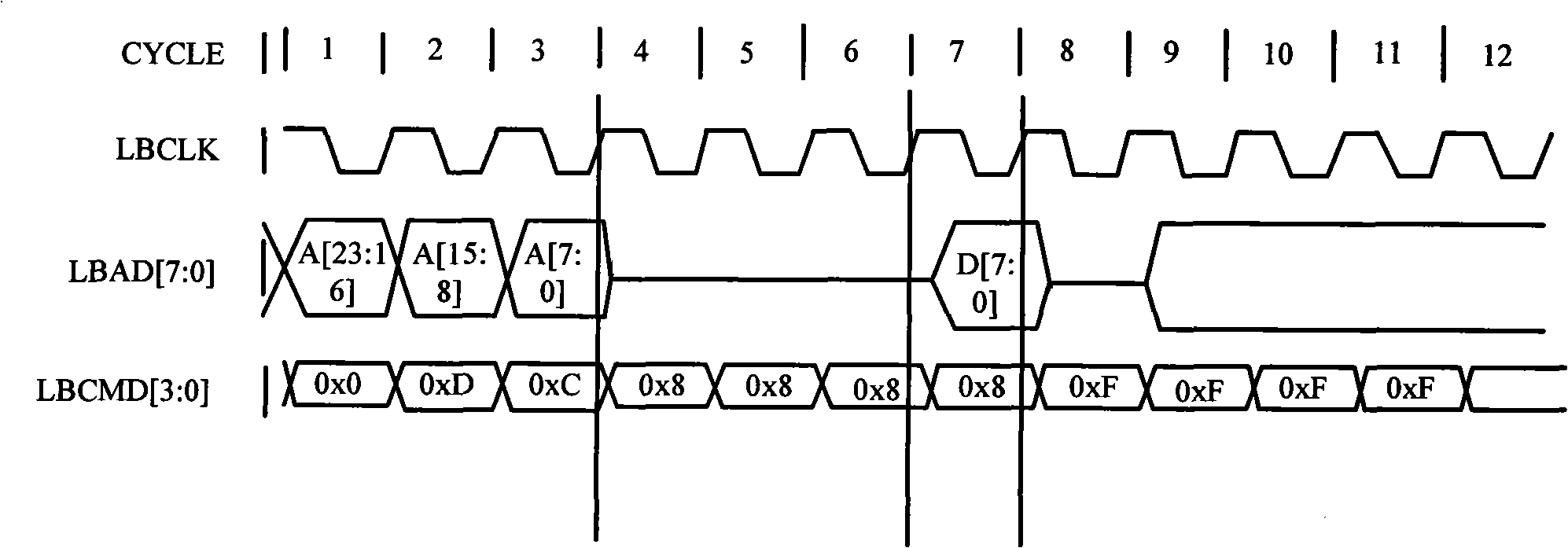

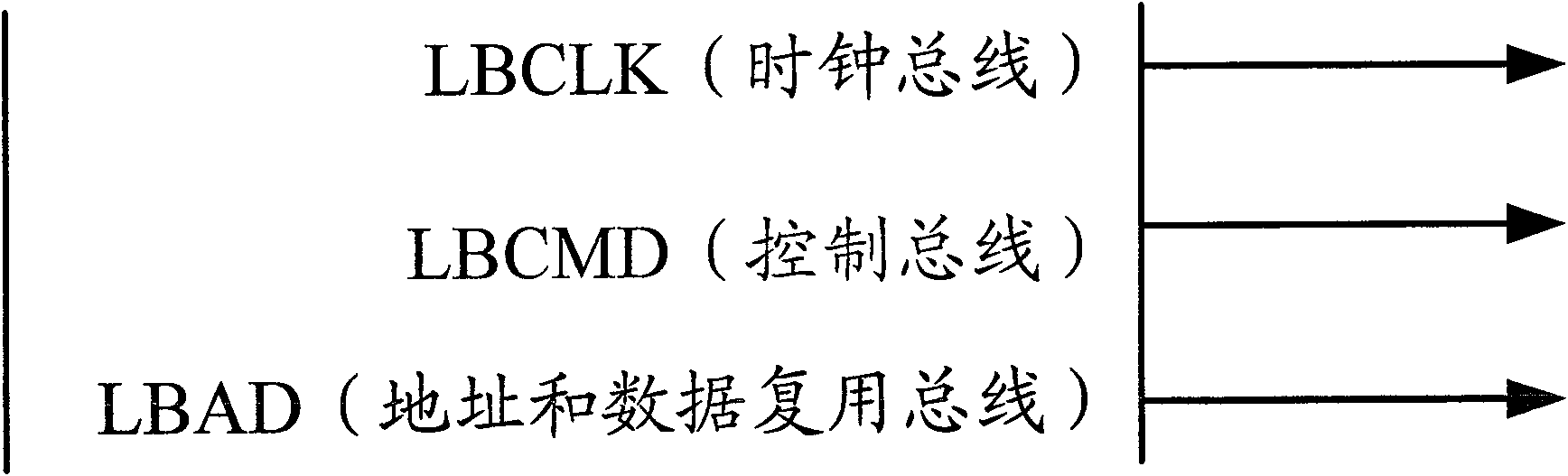

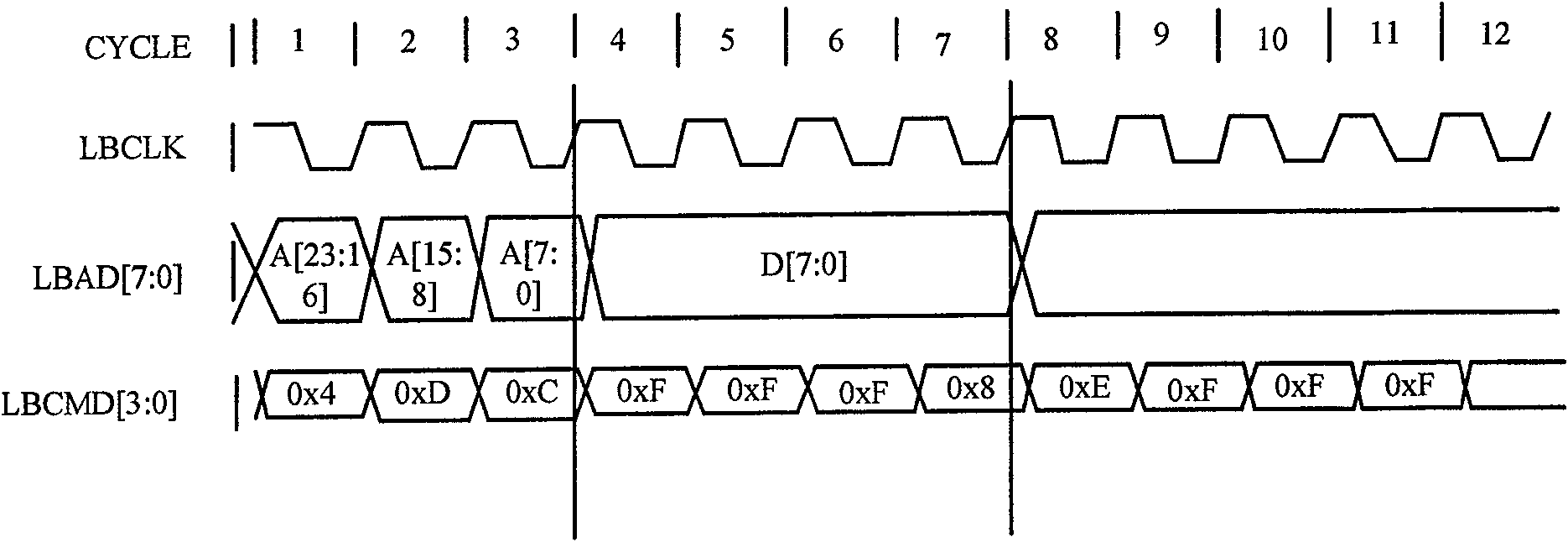

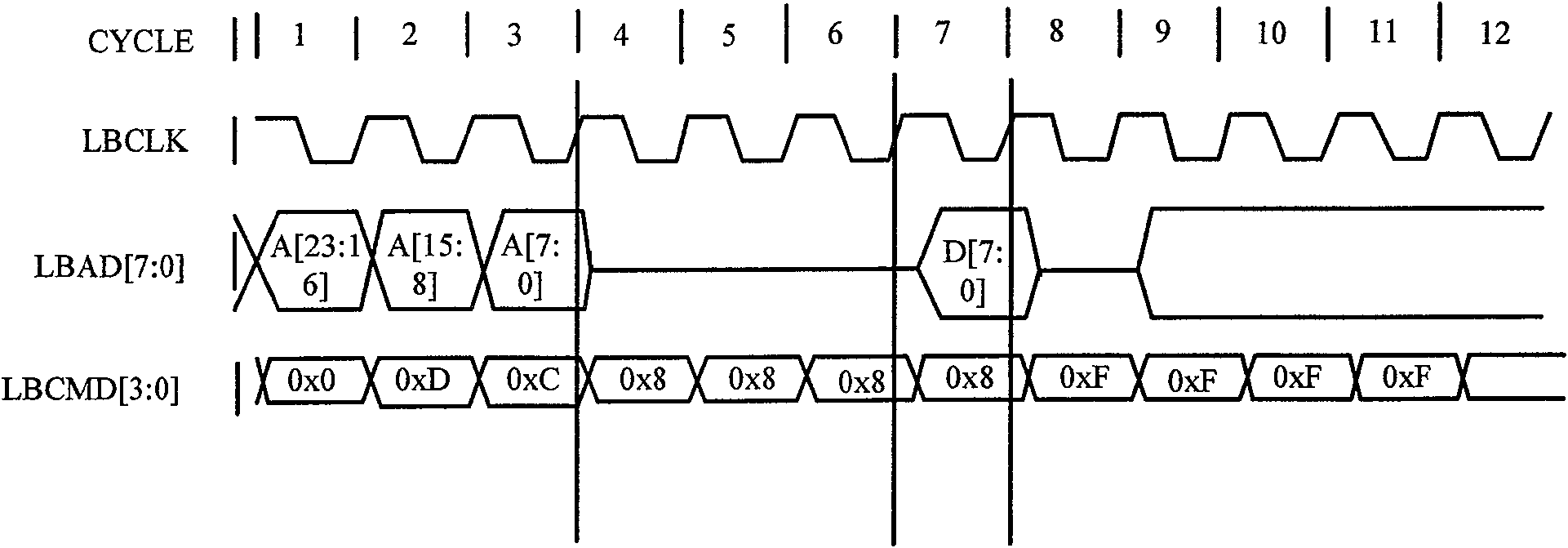

Data processing system and data processing method

ActiveCN101271441ASpeed is not affectedSave internal resourcesElectric digital data processingMultiplexingData processing system

The present invention discloses a data processing system and a data processing method. The address and data multiplexing bus pin of a CPU processor is connected with the data bus pin of a data storage device. When operating the data, the CPU processor sends control commands and address information by controlling the bus pin, the address and data multiplexing bus pin. A converter converts the control commands and the address information into control signals and address signals in the format of a data storage device and sends to the data storage device after receiving the control commands and the address information. The data storage device responds to the data operation of the CPU processor which is carried out by the address and data multiplexing bus pin and the data bus pin of the data storage device according to the control signals and the address signals. Through the present invention, the data operation speed of the CPU processor on peripheral components is not affected by the converter; when in the data operation, the data is processed without the converter, thus saving the internal resources of the converter.

Owner:广东北斗南方科技有限公司

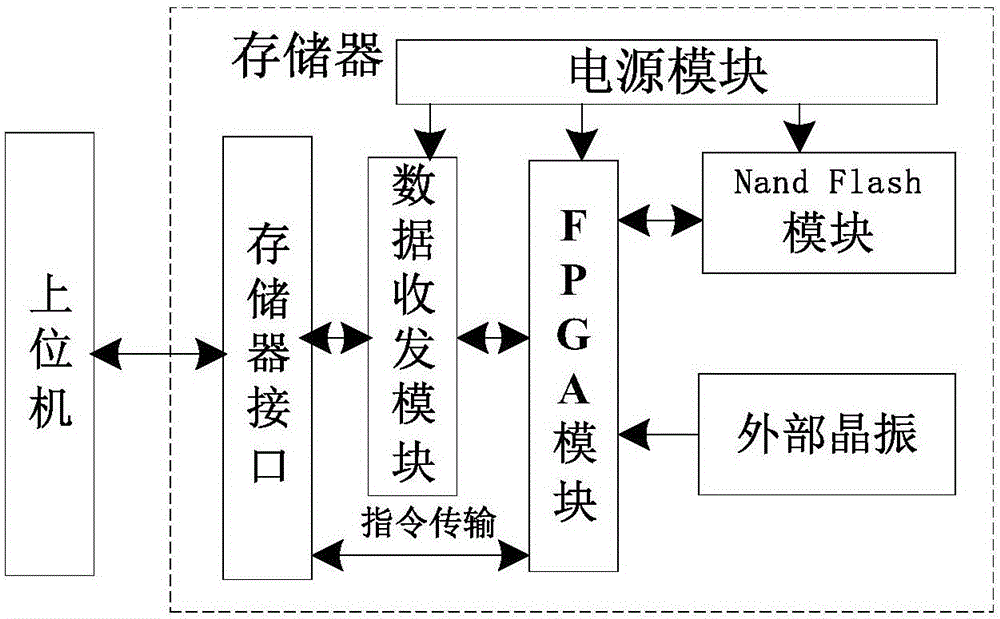

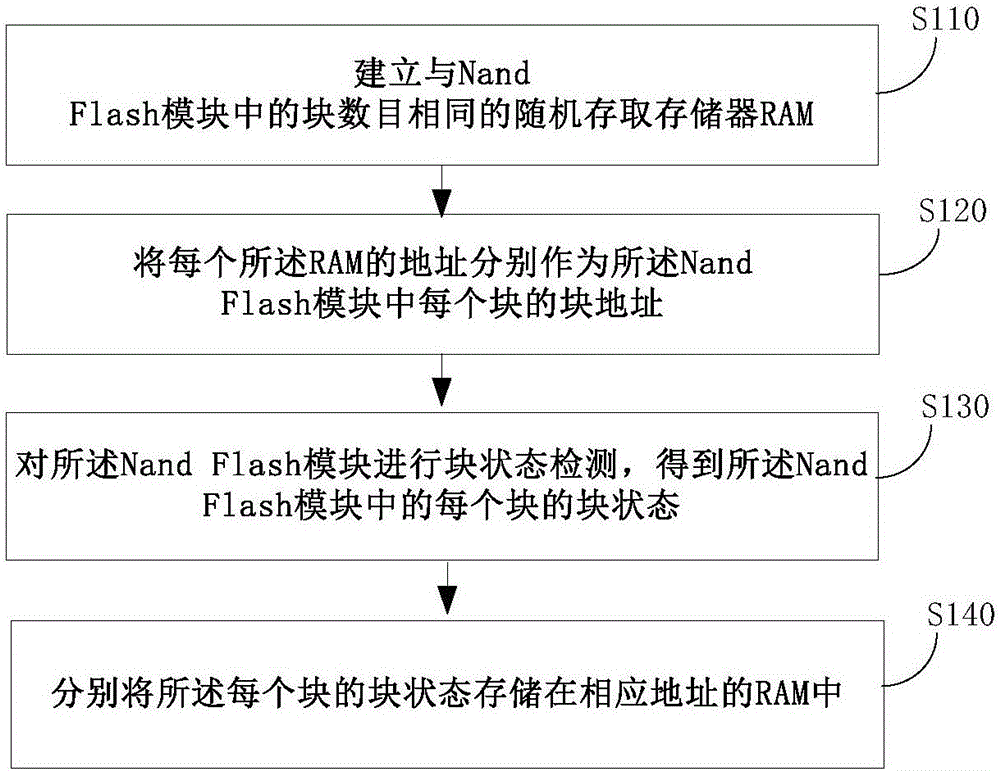

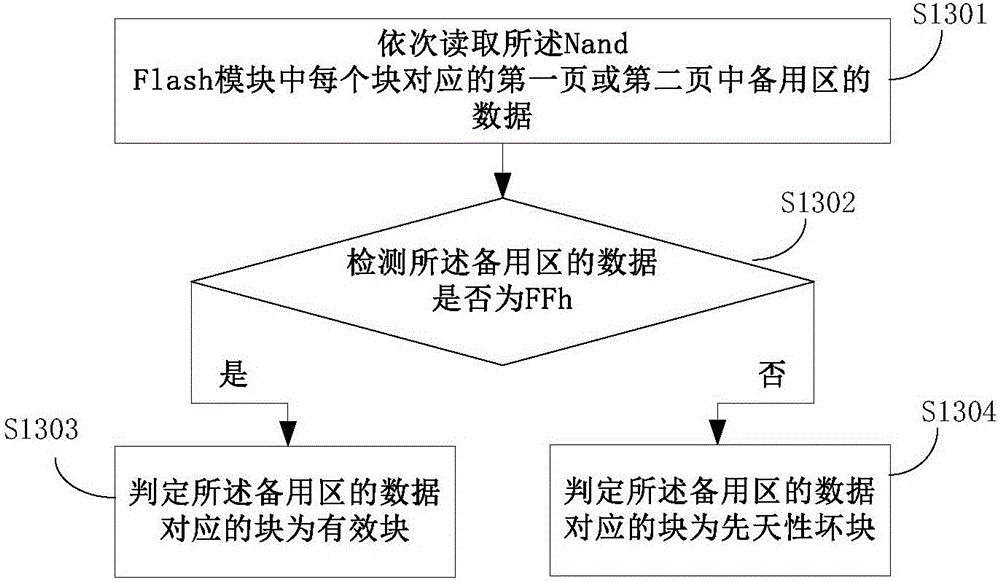

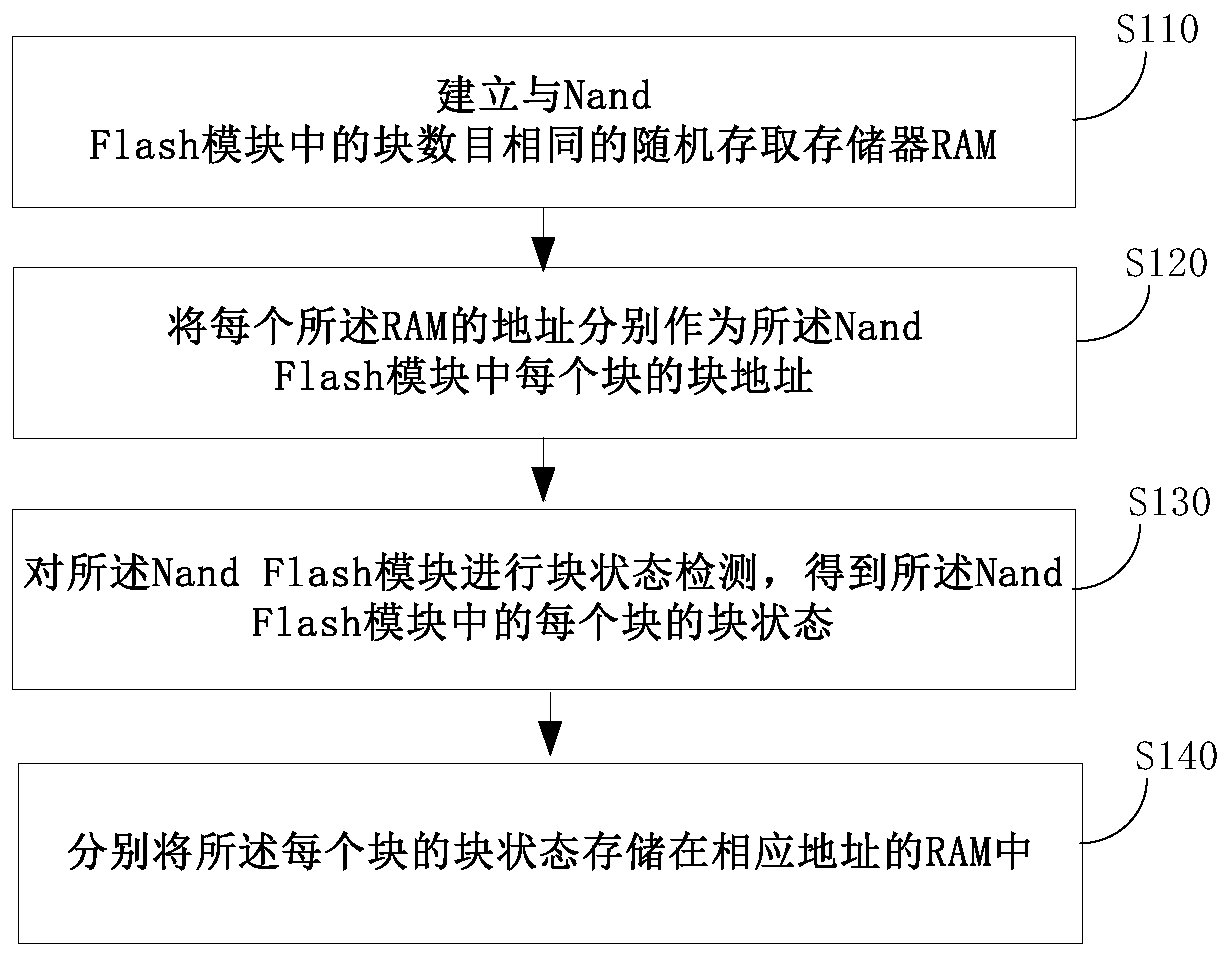

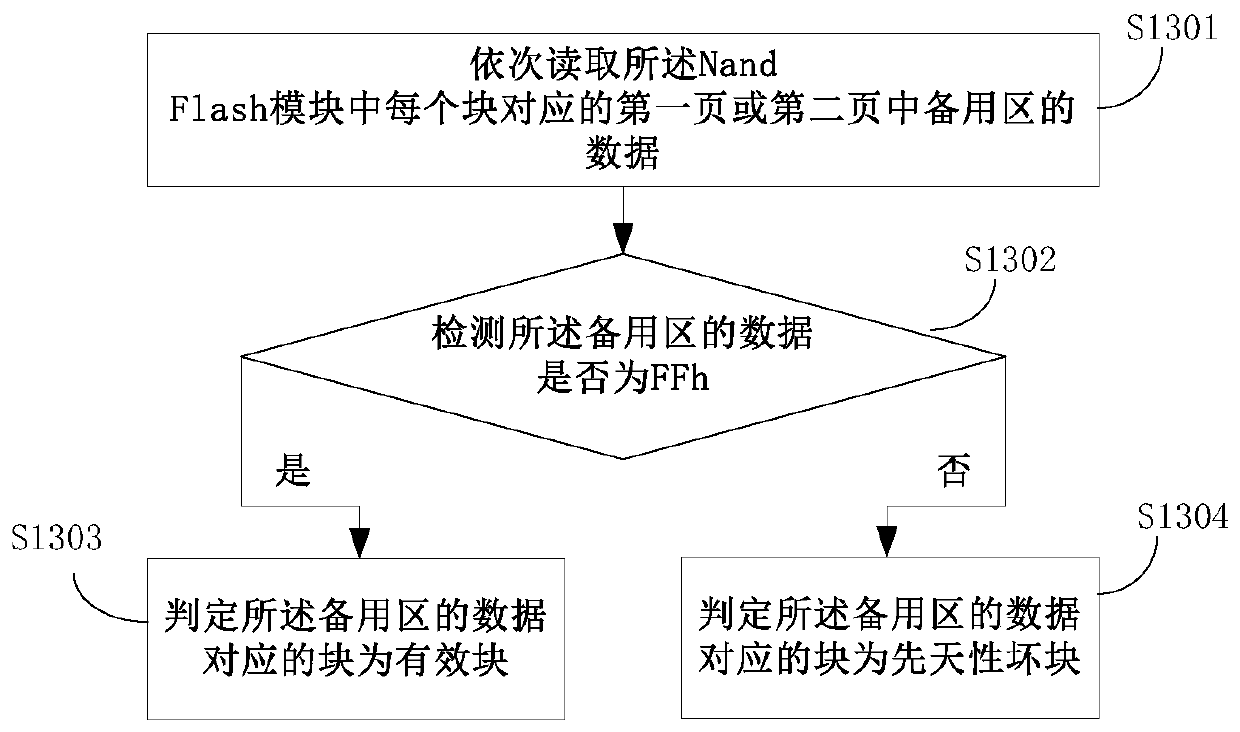

Nand Flash bad block management method and device and memory

ActiveCN106649137ADoes not take up storage spaceSave internal resourcesMemory adressing/allocation/relocationRandom access memoryData storing

The invention discloses a Nand Flash bad block management method and device and a memory. The bad block management method comprises the steps of establishing a random access memory RAM in an FPGA module with the same block number as a Nand Flash module, adopting an address of each RAM as a block address of each block in the Nand Flash module, then, storing a detected block state of the each block in the Nand Flash module into a RAM of the corresponding address so that corresponding writing and reading operation can be conducted according to the address of the each RAM and block state data stored in the RAM. According to the Nand Flash bad block management method and device and the memory, the address of the RAM is adopted as the block address of the each block in the Nand Flash module, and thus the space occupied by the RAM storage block address is saved; moreover, the RAM address needs to be shown with only one counter, thus the storage space of the FPGA module is not occupied, and the inner resource of the FPGA module is further saved.

Owner:BEIJING LUSTER LIGHTTECH

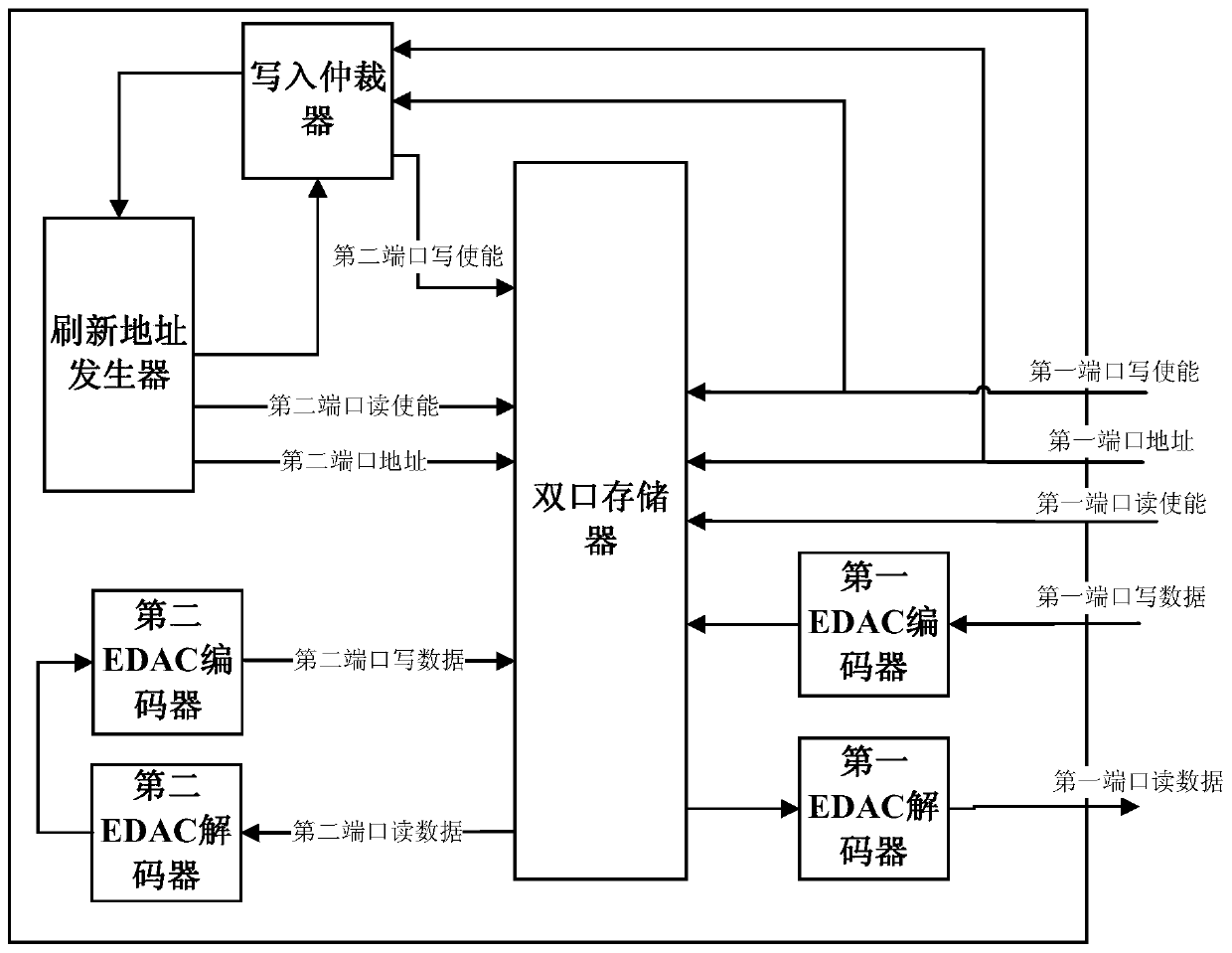

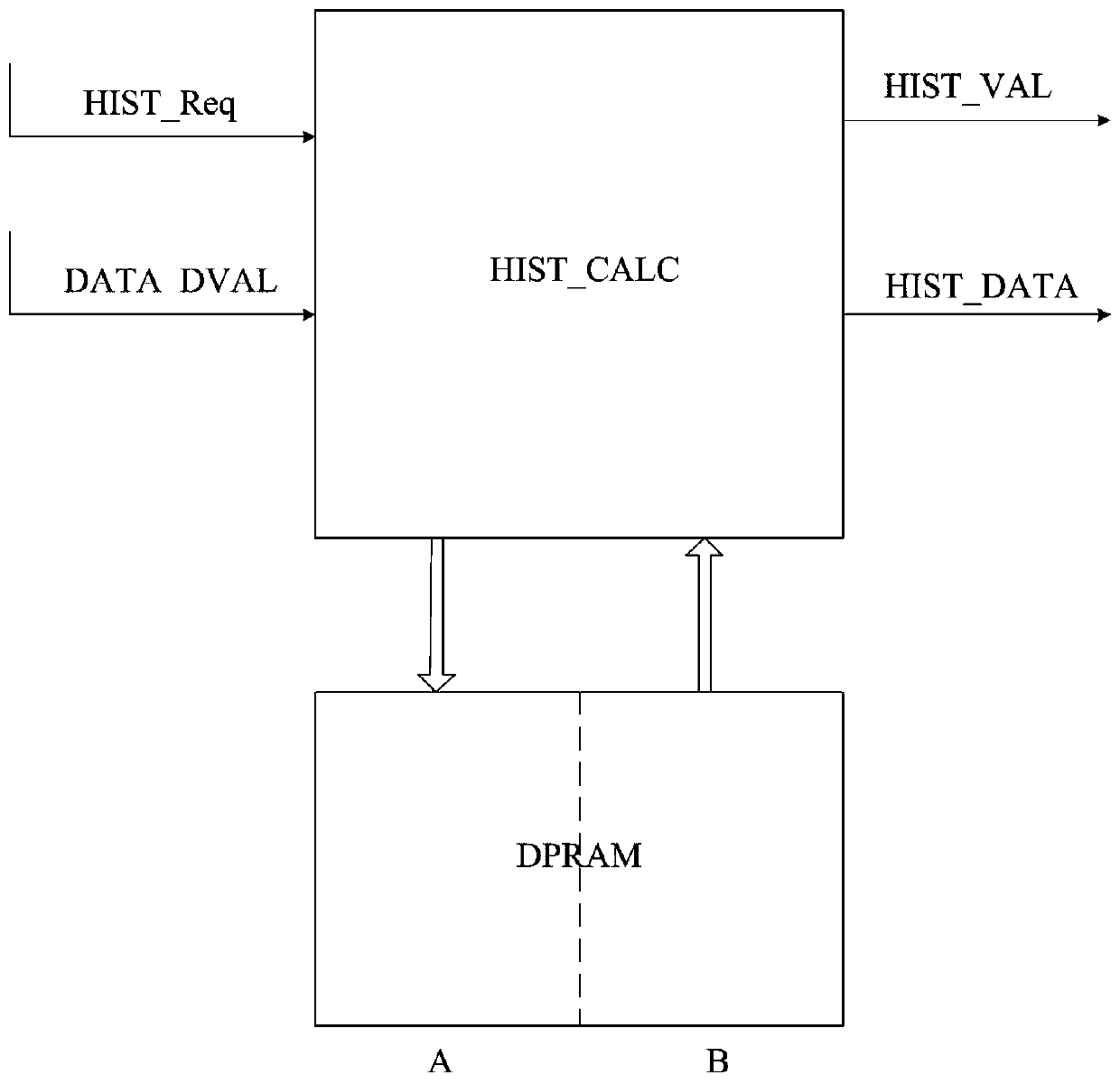

SRAM type FPGA double-port RAM single event upset prevention reinforcing device for spacecraft

ActiveCN110111826ASolve the problem of flip reinforcementReduce overheadDigital storageComputer moduleControl line

The invention relates to an SRAM type FPGA double-port RAM single event upset prevention reinforcing device for a spacecraft, and belongs to the technical field of aerospace electronics. The single event upset prevention reinforcing device comprises a double-port RAM module and an arbitration refresher. The double-port RAM module comprises two sets of completely independent ports which are a firstport and a second port respectively, and each port comprises a data line, an address line, a read enable control line and a write enable control line. The user data is written into and read out of the double-port RAM module through the first port. The arbitration refresher reads the user data stored in the double-port RAM module through the second port and then writes the user data into the double-port RAM again under the condition that the user access data is not influenced, so that the double-port RAM is refreshed. According to the device, the problem of single event upset prevention reinforcement of the BlockRAM in the spacecraft SRAM type FPGA is solved.

Owner:BEIJING INST OF SPACECRAFT SYST ENG

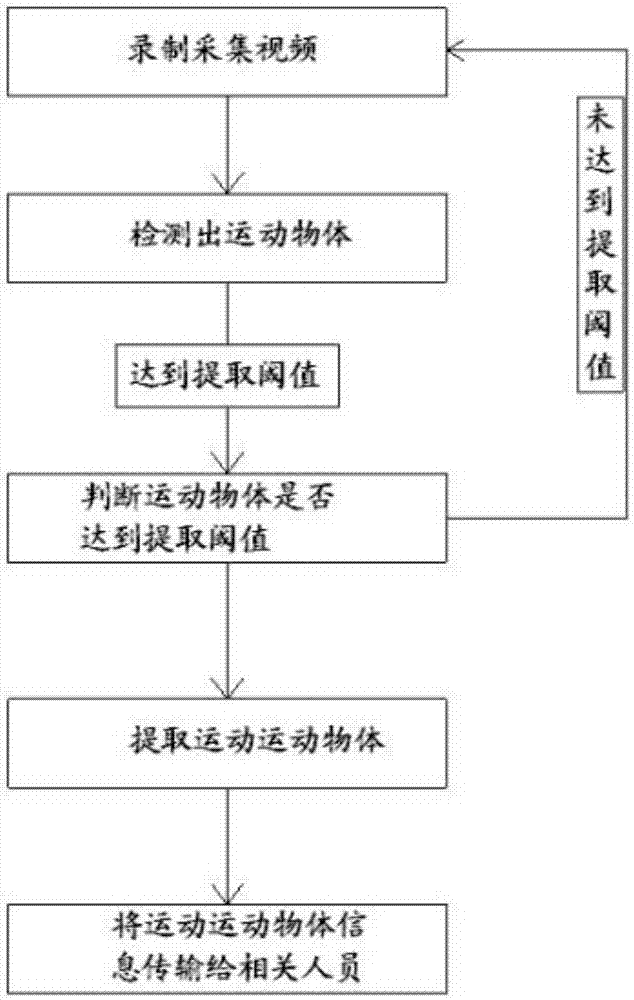

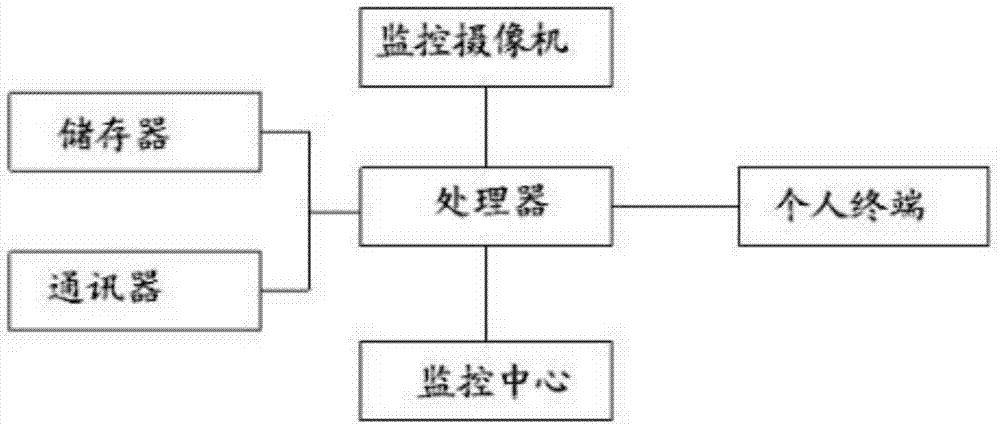

Smart home monitoring method and system based on motion detection

InactiveCN105450992ASave internal resourcesImprove home securityClosed circuit television systemsBurglar alarmEmbedded systemMotion detection

The invention discloses a smart home monitoring method and system based on motion detection, and the system comprises a monitoring camera, a processor, a monitoring center, and a personal terminal, wherein the processor is connected with the monitoring camera, the monitoring center and the personal terminal. The system detects and judges a moving object through employing a three-frame difference method, extracts the moving object in a mode of hybrid Gaussian model background after the moving object reaches the standard, and transmits an image of the moving object to a home owner and other related persons in real time. The system does not carry out extraction when the object reaches a threshold value, saves the internal resources of the processor, can transmit a monitoring image to the related persons in real time after the moving object reaches the standard and is extracted, and improves the household safety.

Owner:王丽华

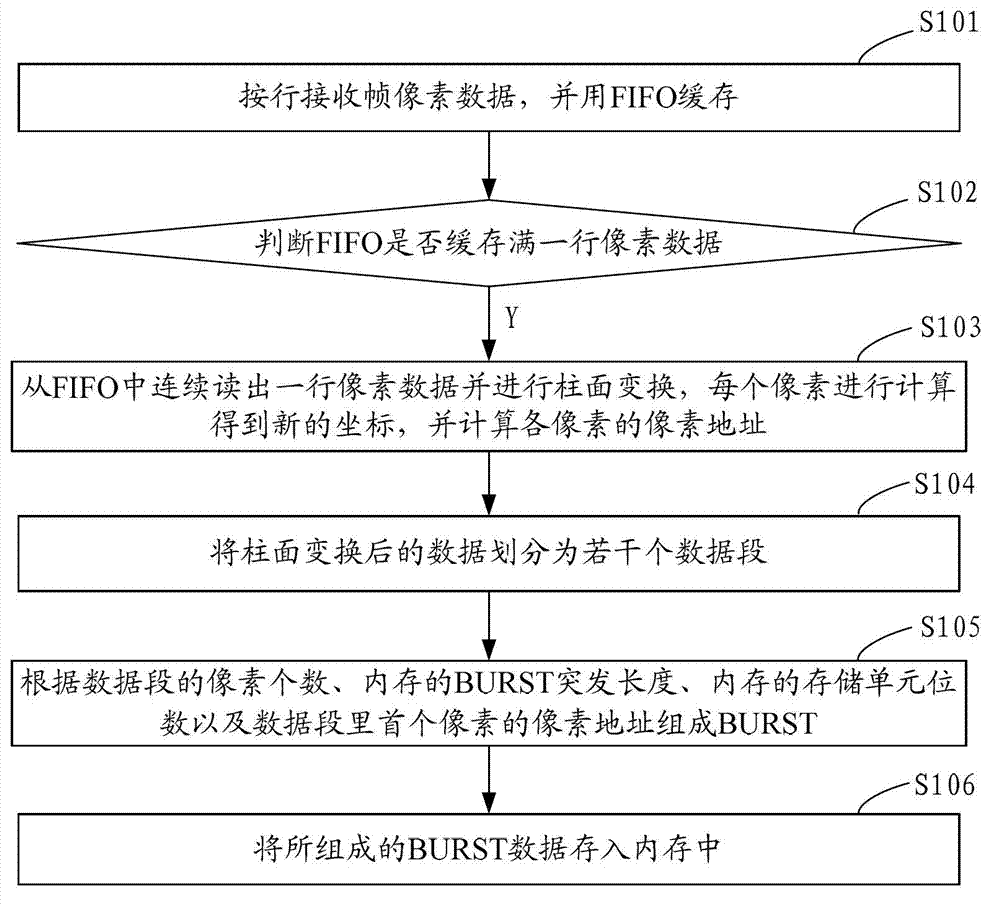

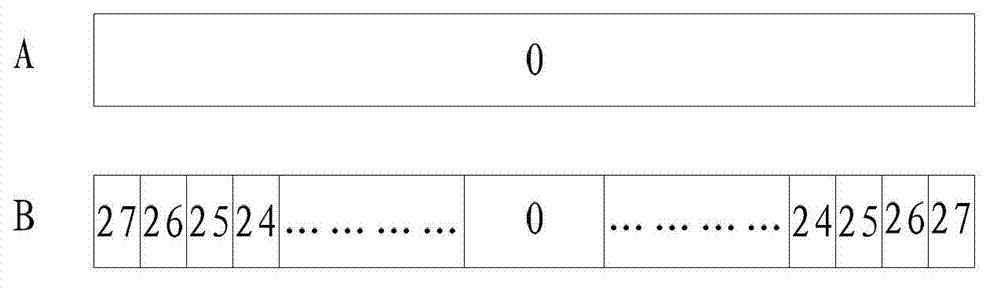

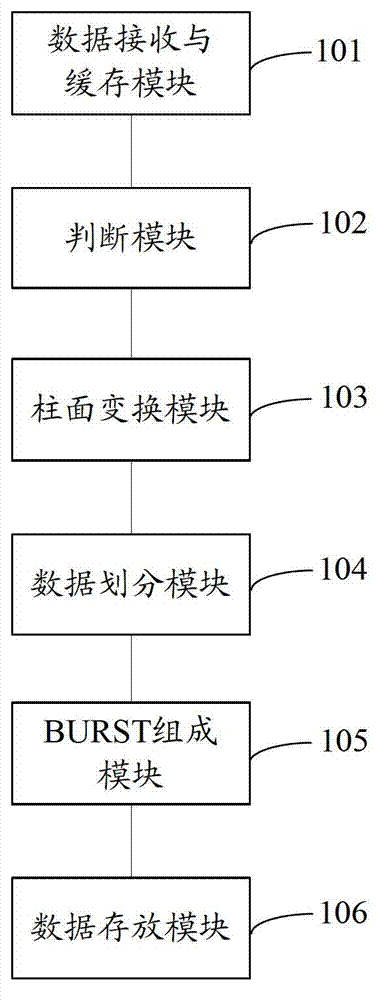

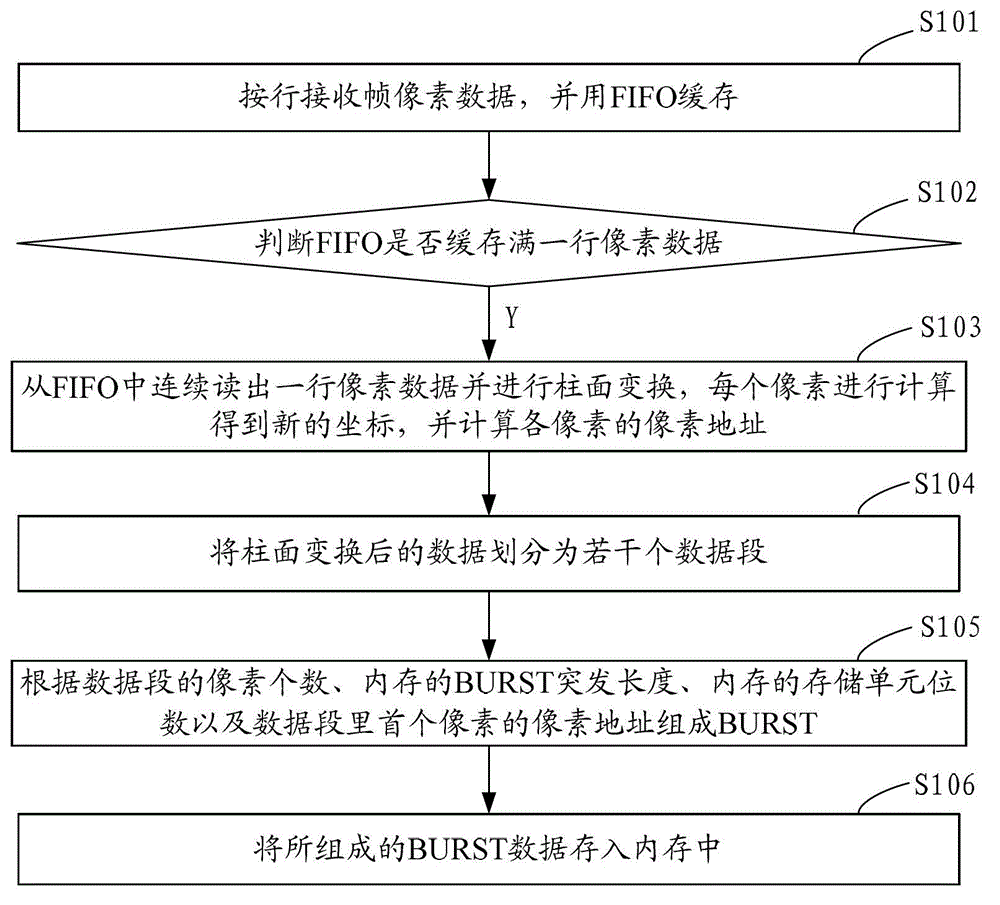

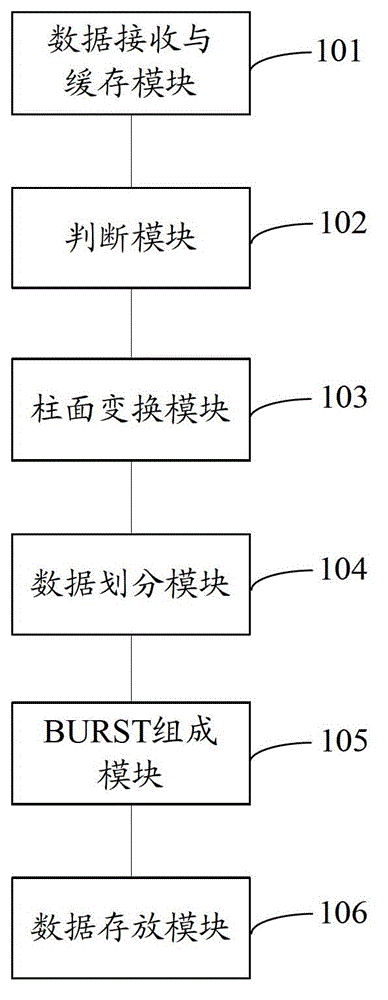

Full view video cylindrical surface image storage method and system

The invention provides a full view video cylindrical surface image storage method and a system. The method includes that pixel data is received by row and first in,first out (FIFO) is used for caching. Whether an FIFO is full of the caching pixel data or not is judged. If it is full, a row of pixel data is continuously read out from the FIFO and the cylindrical surface transformation is carried out. New coordinates are obtained by calculating each pixel and the pixel addresses of each pixel are calculated. Data after the transformation of the cylindrical surface is divided into a plurality of data sections, wherein, among the divided data sections, the pixel address in every data section is consecutive and the next data sections belong to different rows. BURST is formed by the pixel numbers in the data section, the BURST proruption length in the internal memory, the storage unit digit of the internal memory and the pixel address of the first pixel in the data sections. The composed BURST data is stored into the internal memory. The full view video cylindrical surface image storage method and the system achieve the transformation of the cylindrical surface of the video image as well as improve the bandwidth availability ratio.

Owner:GUANGDONG VTRON TECH CO LTD

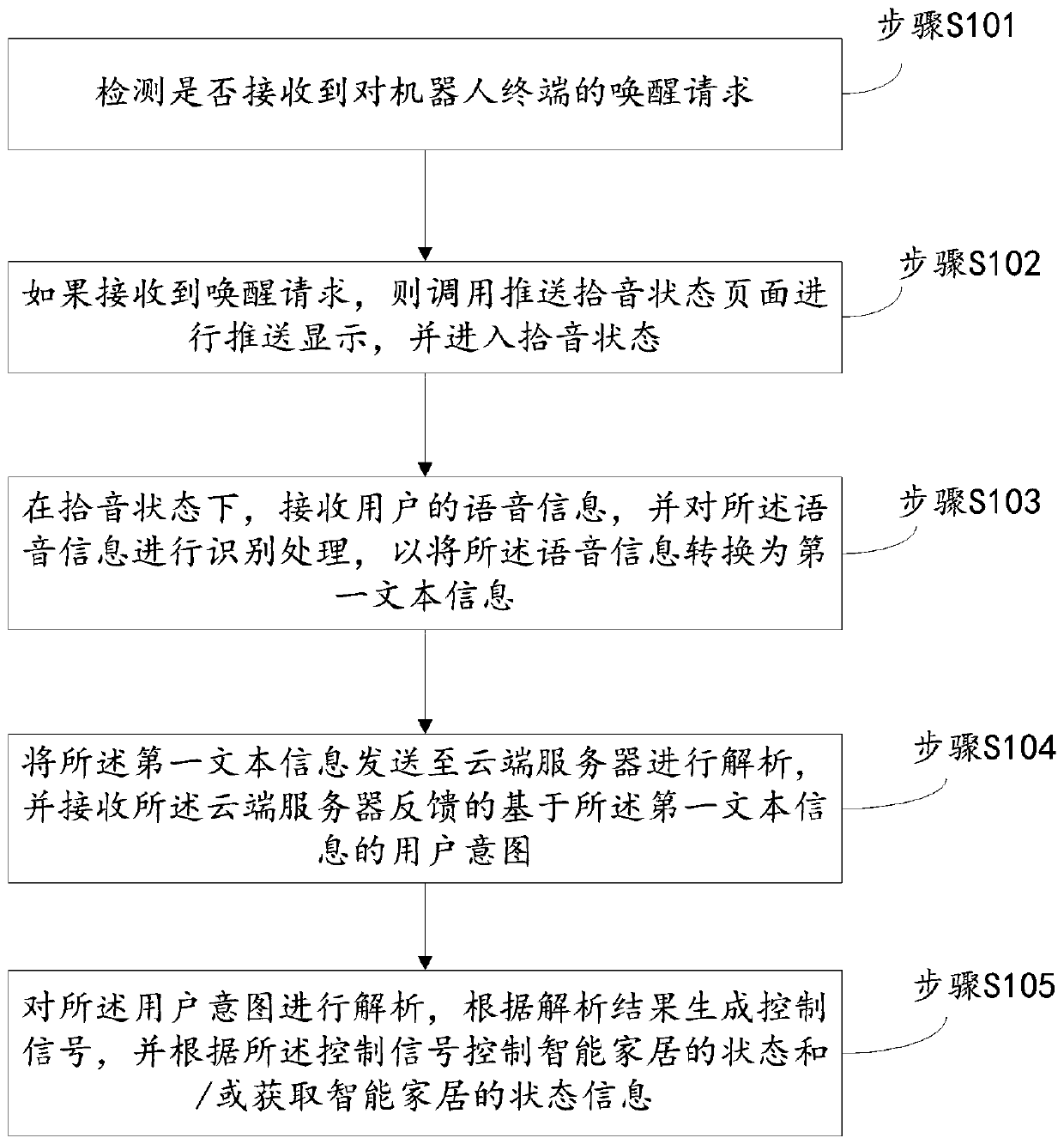

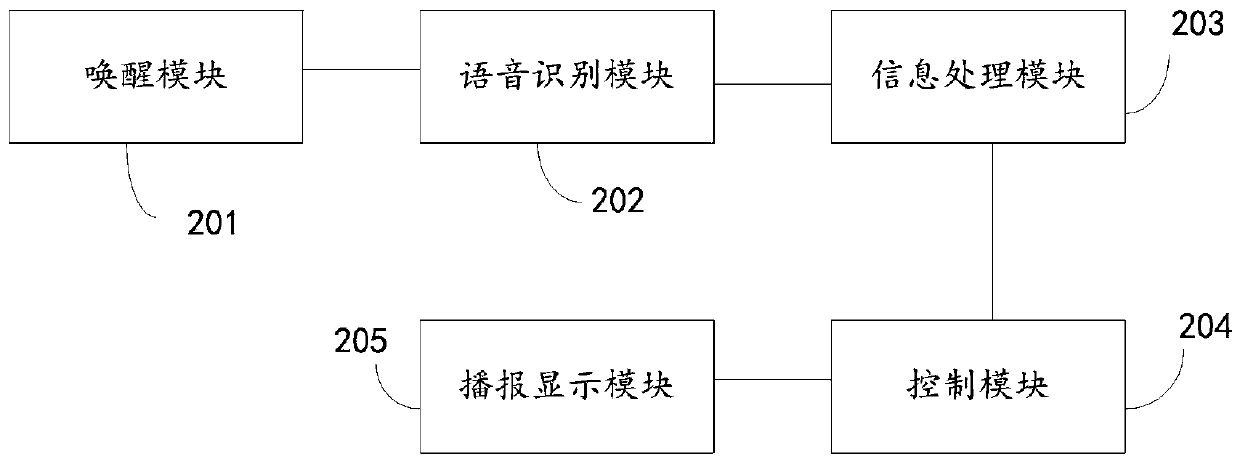

Smart home control method and device, robot and smart home control system

InactiveCN110738994ASave internal resourcesImprove accuracySpeech recognitionHome automation networksControl signalHome control

The invention discloses a smart home control method and device, a robot and a smart home control system. The method comprises the following steps: detecting whether a wakeup request for a robot terminal is received; if the wakeup request is received, calling a push pickup state page for push display, and entering the pickup state; in the pickup state, receiving voice information of a user, and carrying out recognition processing on the voice information so as to convert the voice information into first text information; sending the first text information to a cloud server for analysis, and receiving user intention based on the first text information fed back by the cloud server; analyzing the user intention, generating a control signal according to the analysis result, and controlling thestate of the smart home and / or acquiring the state information of the smart home according to the control signal; and the method can effectively improve the accuracy and convenience of smart home control.

Owner:北京爱接力科技发展有限公司

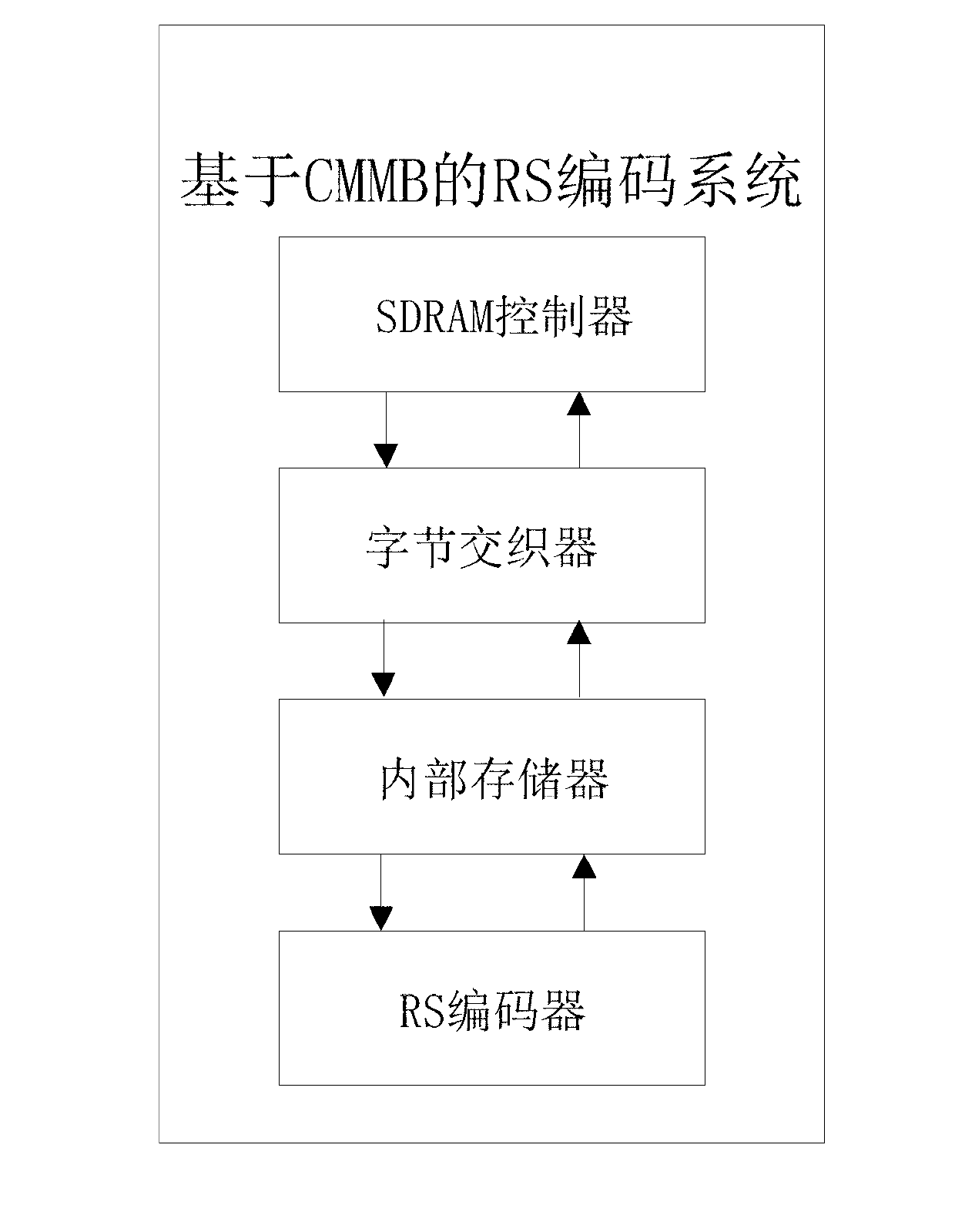

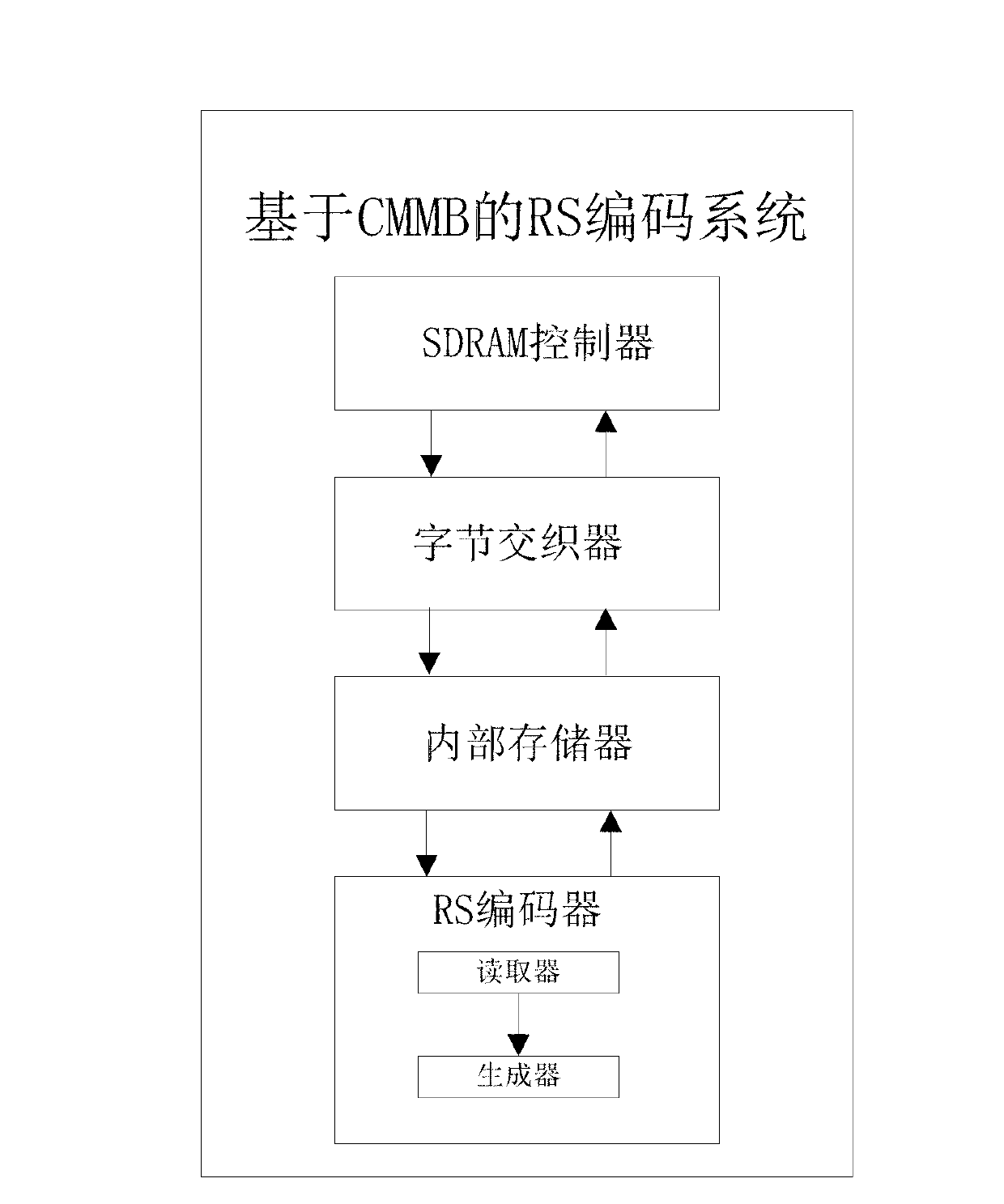

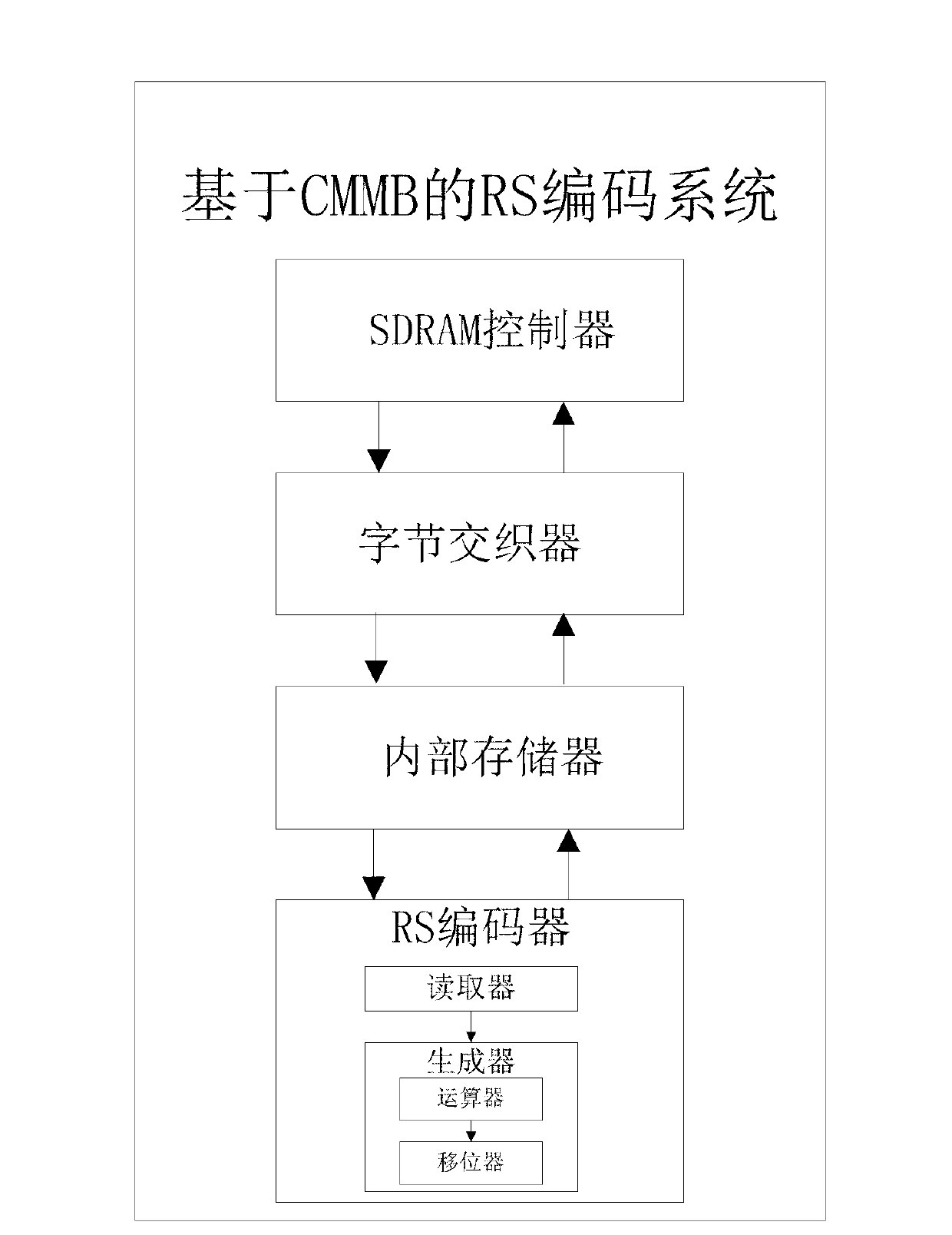

CMMB (China mobile multimedia broadcasting) based RS (reed-solomon) coding system and implementing method thereof

ActiveCN103001736ASave internal resourcesReduce computationError preventionInternal memorySynchronous dynamic random-access memory

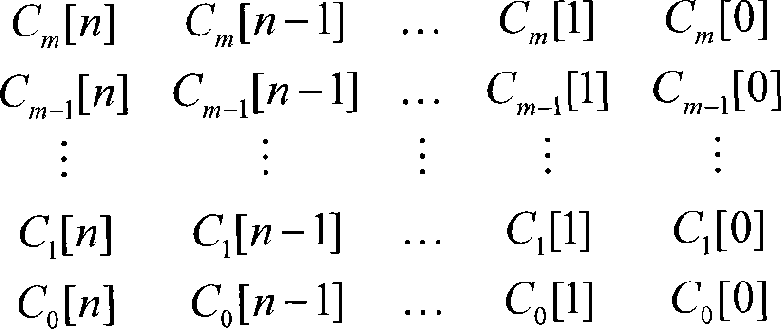

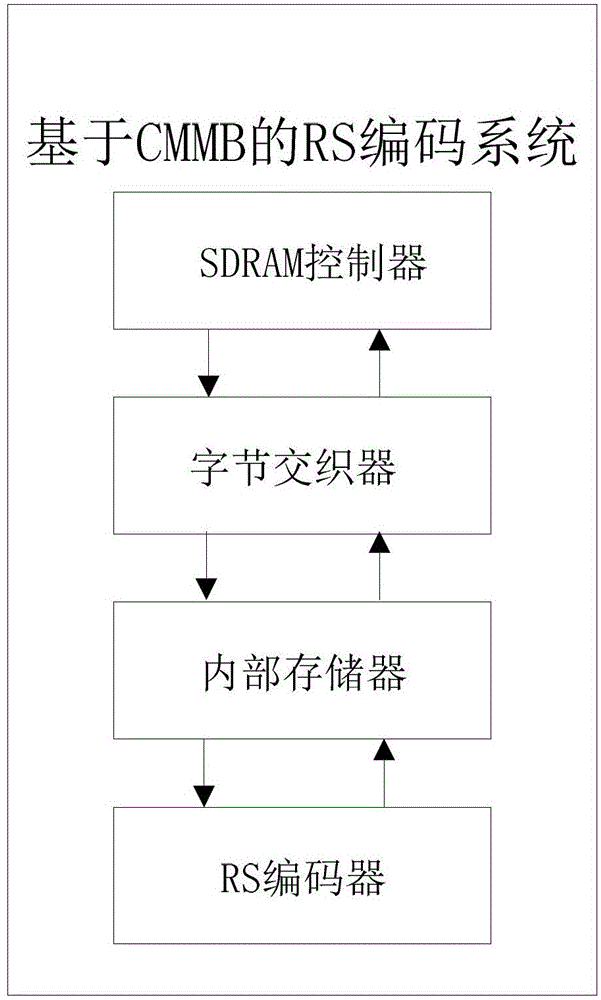

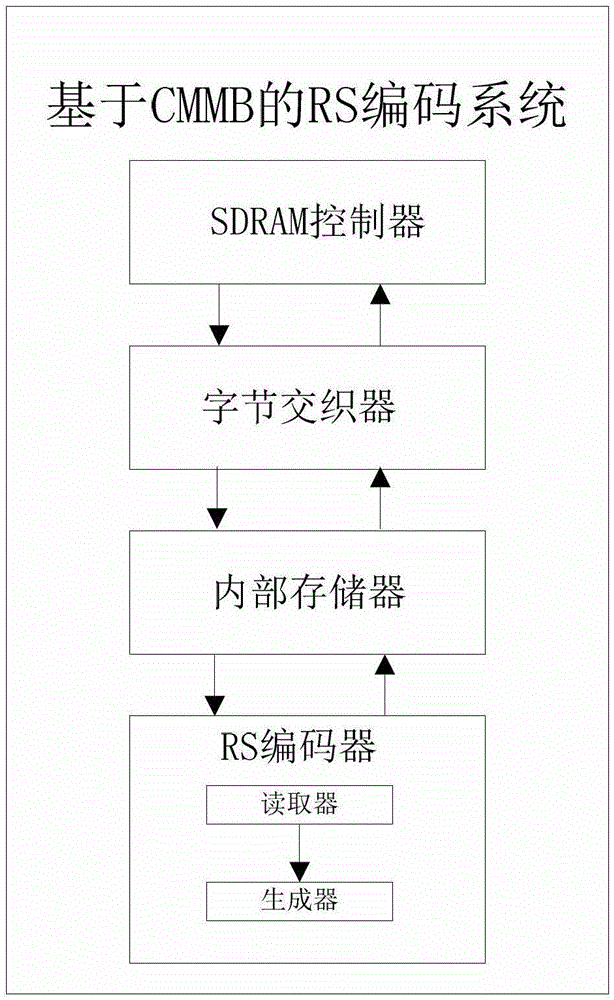

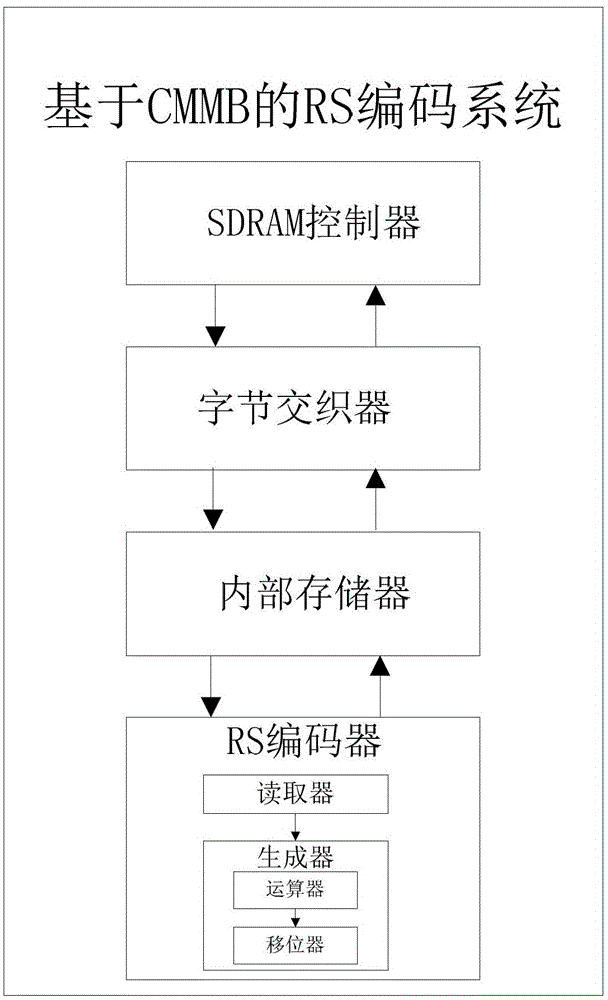

The invention discloses a CMMB (China mobile multimedia broadcasting) based RS (reed-solomon) coding system and an implementing method thereof. The CMMB based RS coding system comprises an SDRAM (synchronous dynamic random access memory) controller, a byte interleaver, an internal memory and an RS coder, wherein the SDRAM controller is used for receiving information code streams and storing accessing check codes, the byte interleaver is used for subjecting accessing information codes and the check codes to byte interleaving, the internal memory is used for caching the accessing information codes and the check codes, and the RS coder is used for coding the information codes. The implementing method includes that the SDRAM controller receives the information code streams, the information codes are subjected to byte interleaving by the byte interleaver, the information codes interleaved are stored in the internal memory and are read and encoded and the like. By the CMMB based RS coding system and the implementing method thereof, internal resources of an FPGA (field programmable gate array) is effectively saved, and operation load is reduced, so that the problem about time sequence of the FPGA is solved, the low-end FPGA can be utilized for design, and normal work in complicated environment can be guaranteed.

Owner:ALLWIN TELECOMM

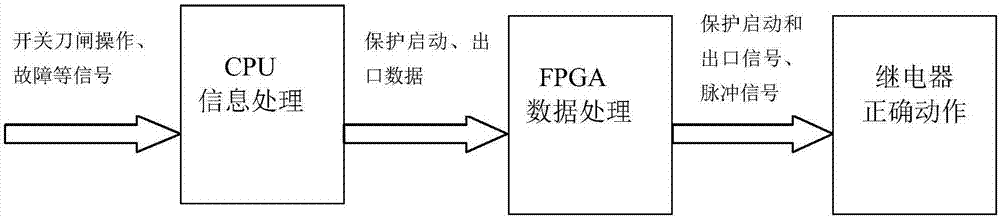

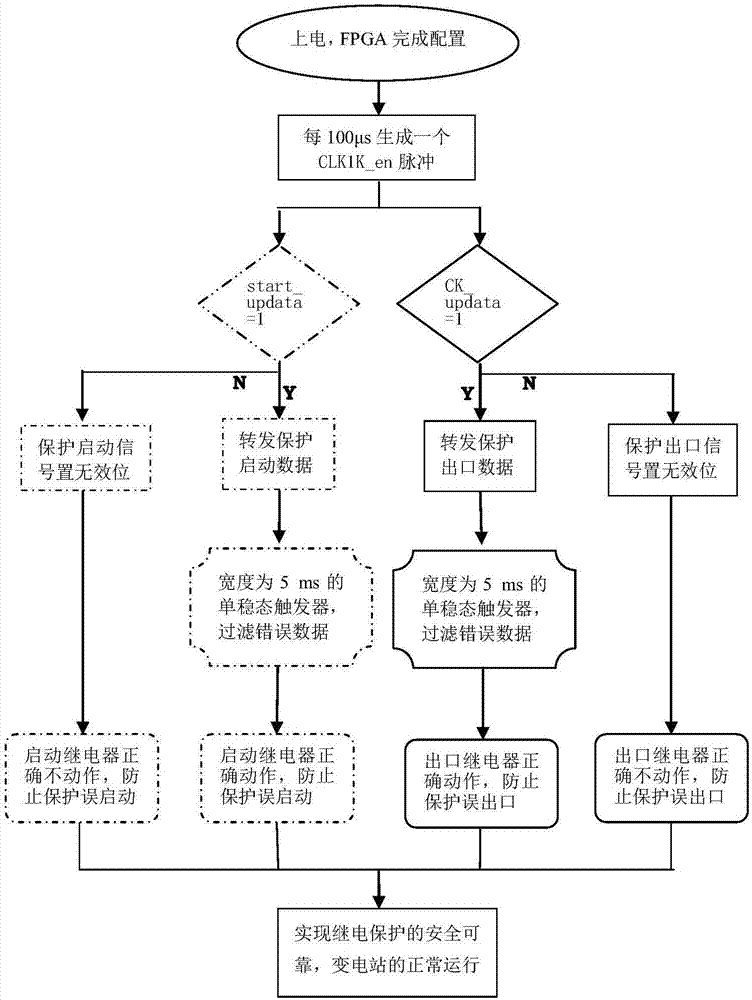

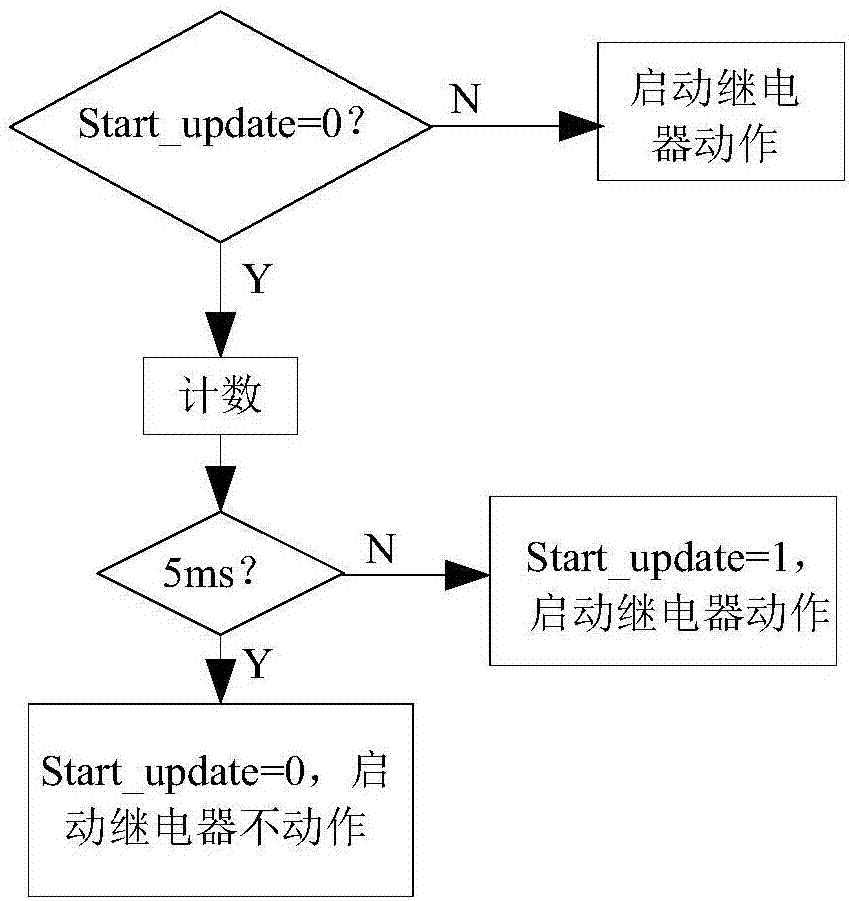

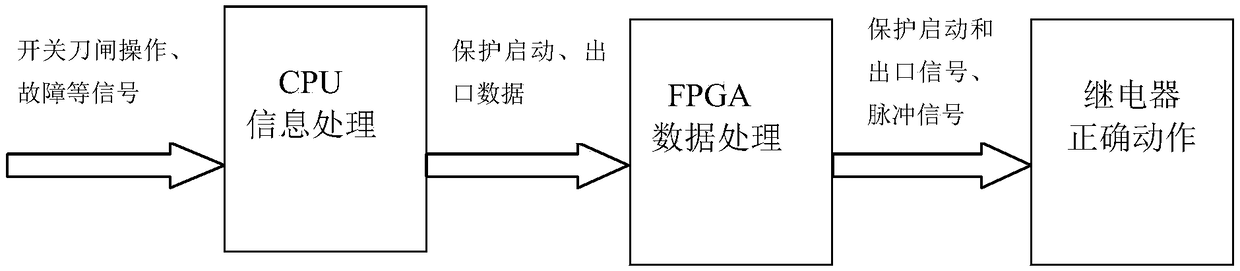

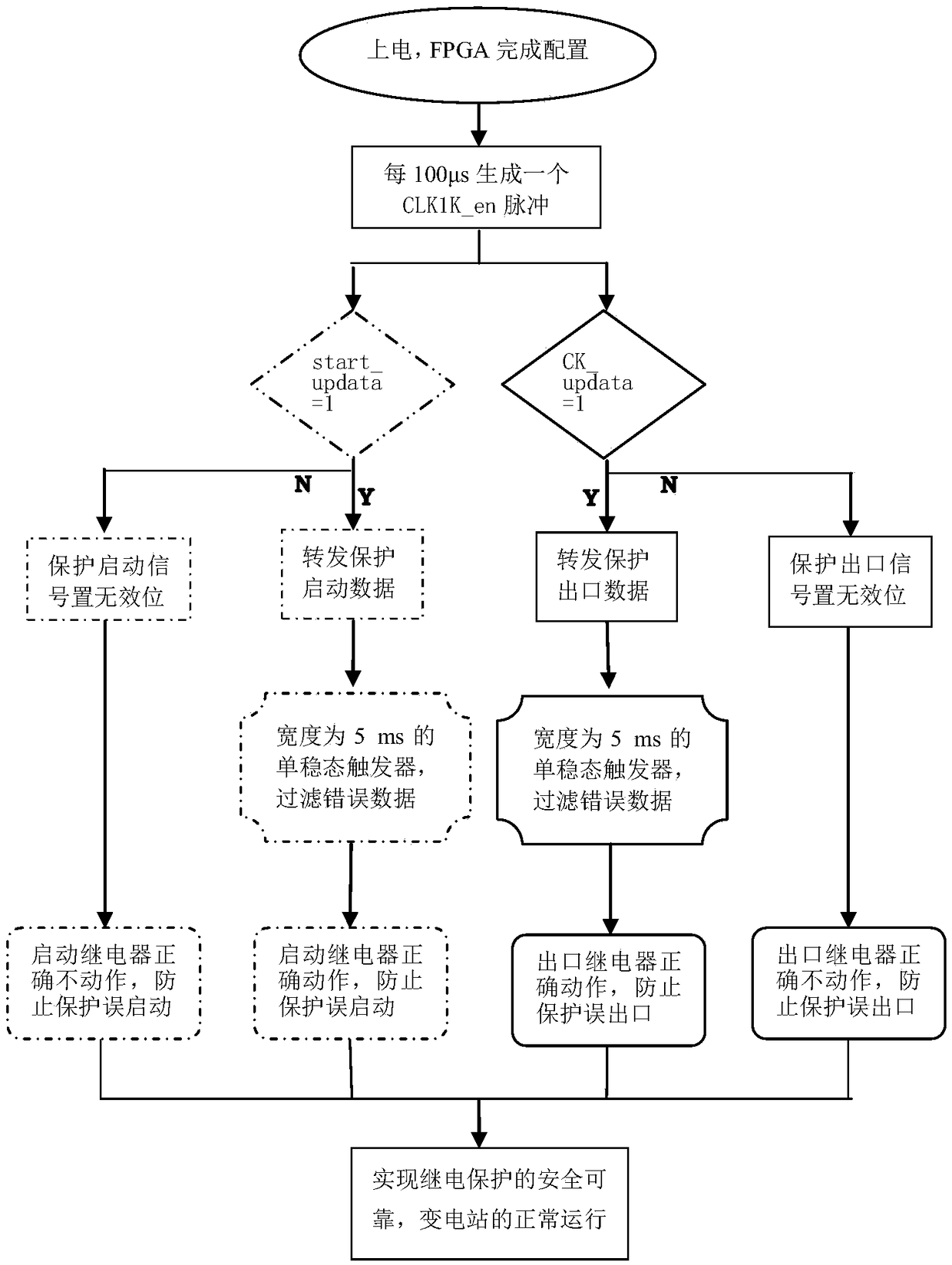

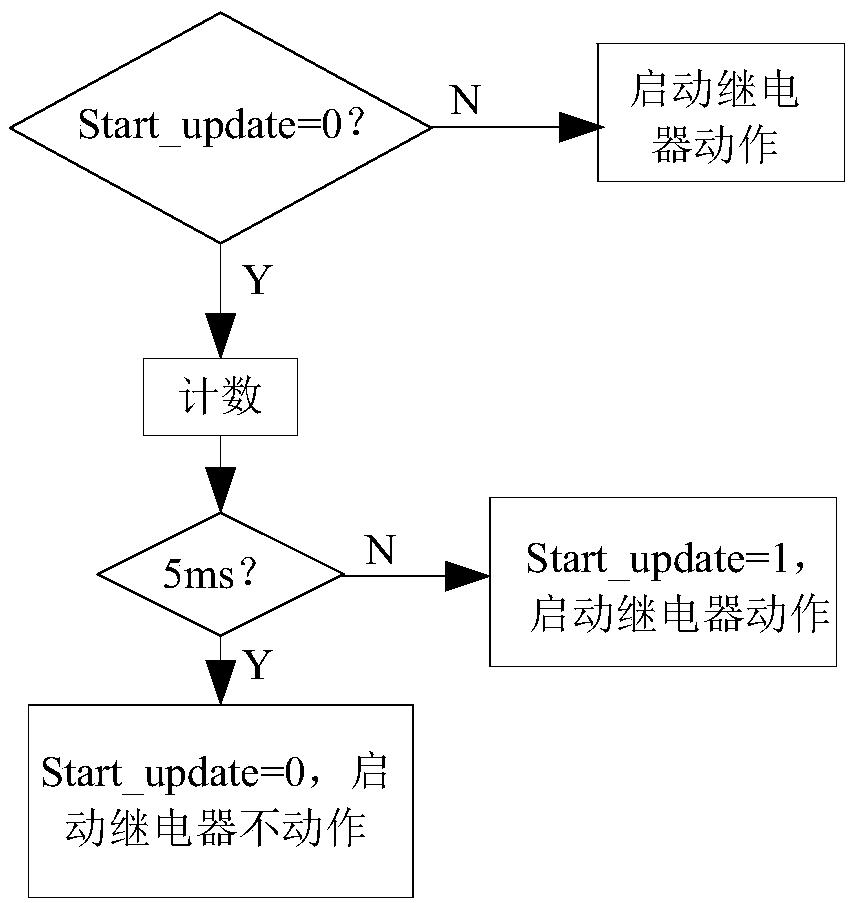

FPGA-based method and system for preventing relay protection misoperation

ActiveCN107171297AImprove accuracyImprove reliabilityEmergency protective circuit arrangementsDependabilityRelay

The invention provides an FPGA-based method and system for preventing relay protection misoperation. A CPU periodically transmits protection starting / outlet data to an FPGA, and when the FPGA detects that the protection starting / outlet data is valid, a starting / outlet relay is controlled to act; when the FPGA detects that a protection outlet state signal is invalid, and after a timed non-continued set time, the FPGA detects that the protection starting / outlet data is valid, the starting / outlet relay is controlled to act; or when the data is invalid, and after the timed non-continued set time, the starting / outlet relay is controlled not to act. By virtue of the method and the system, the protection starting / outlet data accuracy and relay protection action reliability are improved; in addition, the protection starting and outlet signals are sent out directly through the FPGA, without through an outlet plug-in, so that multilayer data transfer is reduced, and speed, reliability and accuracy of relay protection are improved; and furthermore, the periodical judgment on the protection data is simple in logic, troublesome signal content analysis is omitted, and the FPGA internal resource is saved.

Owner:XUJI GRP +3

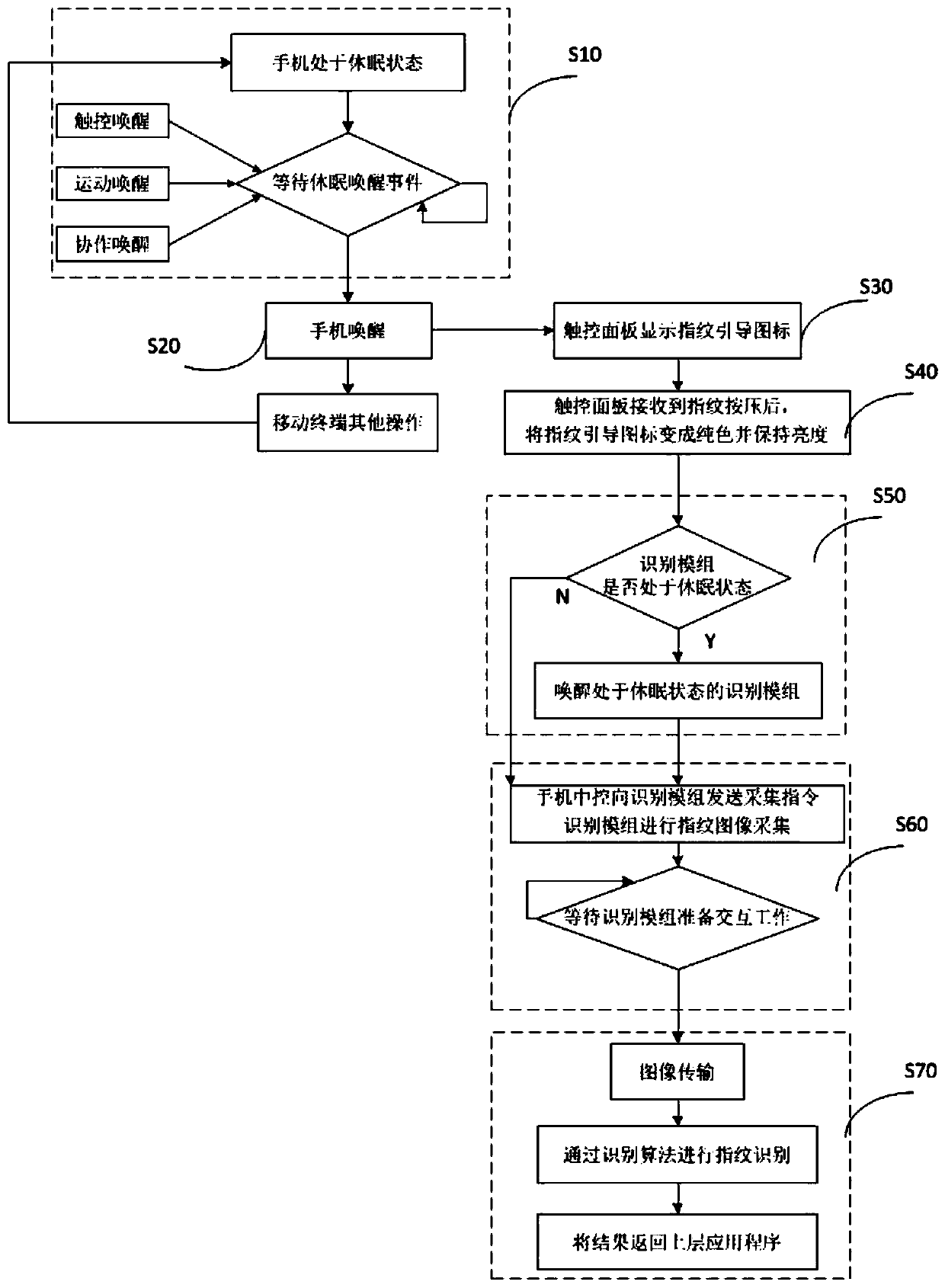

A low-energy consumption fingerprint identification method under a mobile phone screen

InactiveCN109862191AReduce volumeSave internal spacePower managementUnauthorised/fraudulent call preventionRecognition algorithmTouch panel

The invention discloses a low-energy-consumption fingerprint identification method under a mobile phone screen, which comprises the following steps: a mobile phone is in a dormant state and waits fora dormant wake-up event; the mobile phone is awakened and enters a fingerprint identification mode; the touch panel displays a fingerprint guide icon; after the touch panel receives the fingerprint pressing, the fingerprint guide icon is changed into pure color and the brightness is kept; the fingerprint identification module is awakened in a dormant state; after waking up, the mobile phone central controller sends an acquisition instruction to the fingerprint identification module, and the fingerprint identification module performs fingerprint image acquisition; after the collected image is interacted with the mobile phone center control, fingerprint recognition is carried out through a recognition algorithm, and a result is returned to the upper-layer application program. A good recognition environment is provided by utilizing the conditions of the mobile phone, so that the optical fingerprint sensor can carry out fingerprint recognition in any external environment; by combining theawakening mobile phone, the awakening fingerprint identification module and the mobile phone central control, the internal resources of the mobile phone can be effectively saved, and the limited endurance time of the mobile phone is ensured.

Owner:SHANGHAI FINGER TECH CO LTD

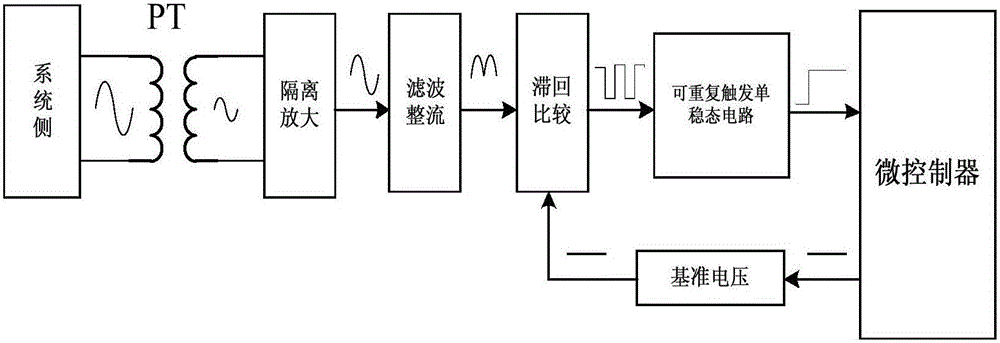

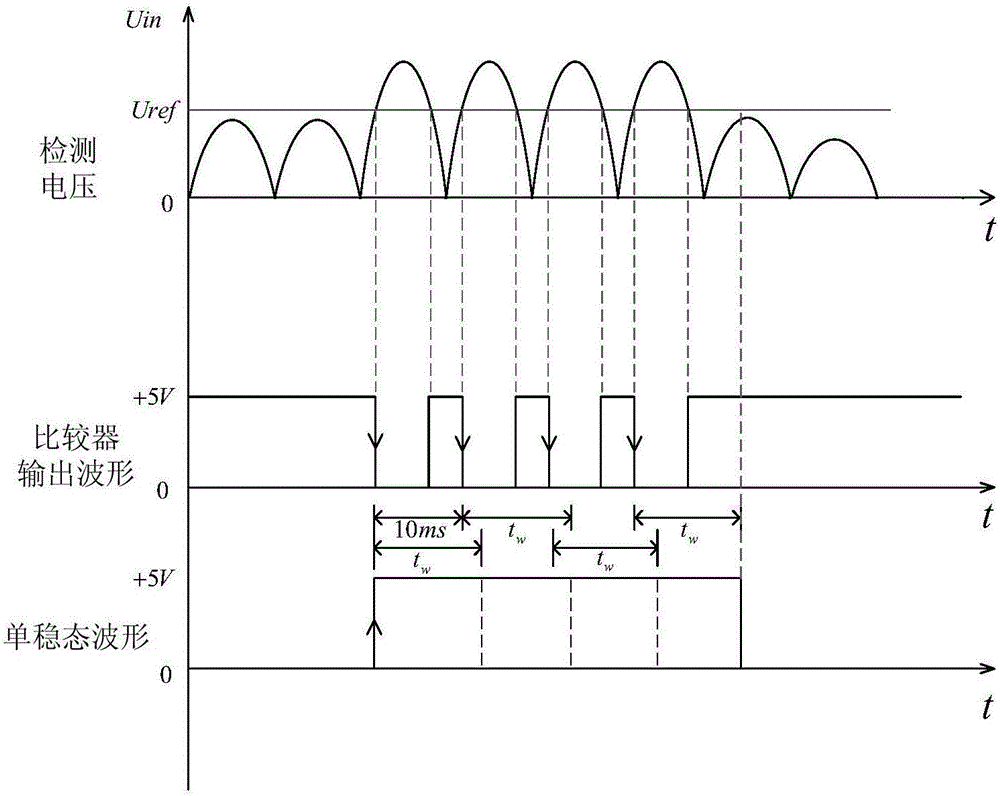

System and method for rapidly determining single phase earth fault

InactiveCN106405309AEasy to detectSave internal resourcesElectrical testingSingle phaseIsolation amplifier

The invention discloses a system and method for rapidly determining a single phase earth fault. A structure of the system comprises a voltage transformer connected with electric signals, an isolation amplifier, a filtering rectifier, a hysteresis comparator, a monostable circuit capable of being repeatedly triggered and a microcontroller, wherein the microcontroller is connected with the hysteresis comparator and the monostable circuit capable of being repeatedly triggered. According to the system and method for rapidly determining the single phase earth fault, a characteristic of rapid responding and determining of hardware can be realized, and an advantage of flexible threshold value setting of software can be retained; during single phase earth fault determining operation, alternating current voltage signals are converted into a continuous pulse string via combination of a filtering rectification circuit and the hysteresis comparator; specifically the monostable circuit capable of being repeatedly triggered is adopted, and the pulse string is shaped into a signal pulse having a rising edge characteristic via which determining operation can be conducted via the microcontroller; via the method, a problem of threshold value jitter in a conventional hardware method can be effectively prevented, flexible threshold value setting can be realized via the microcontroller, strong universality can be realized, and high transferability is achieved.

Owner:WUHAN HAIO ELECTRIC

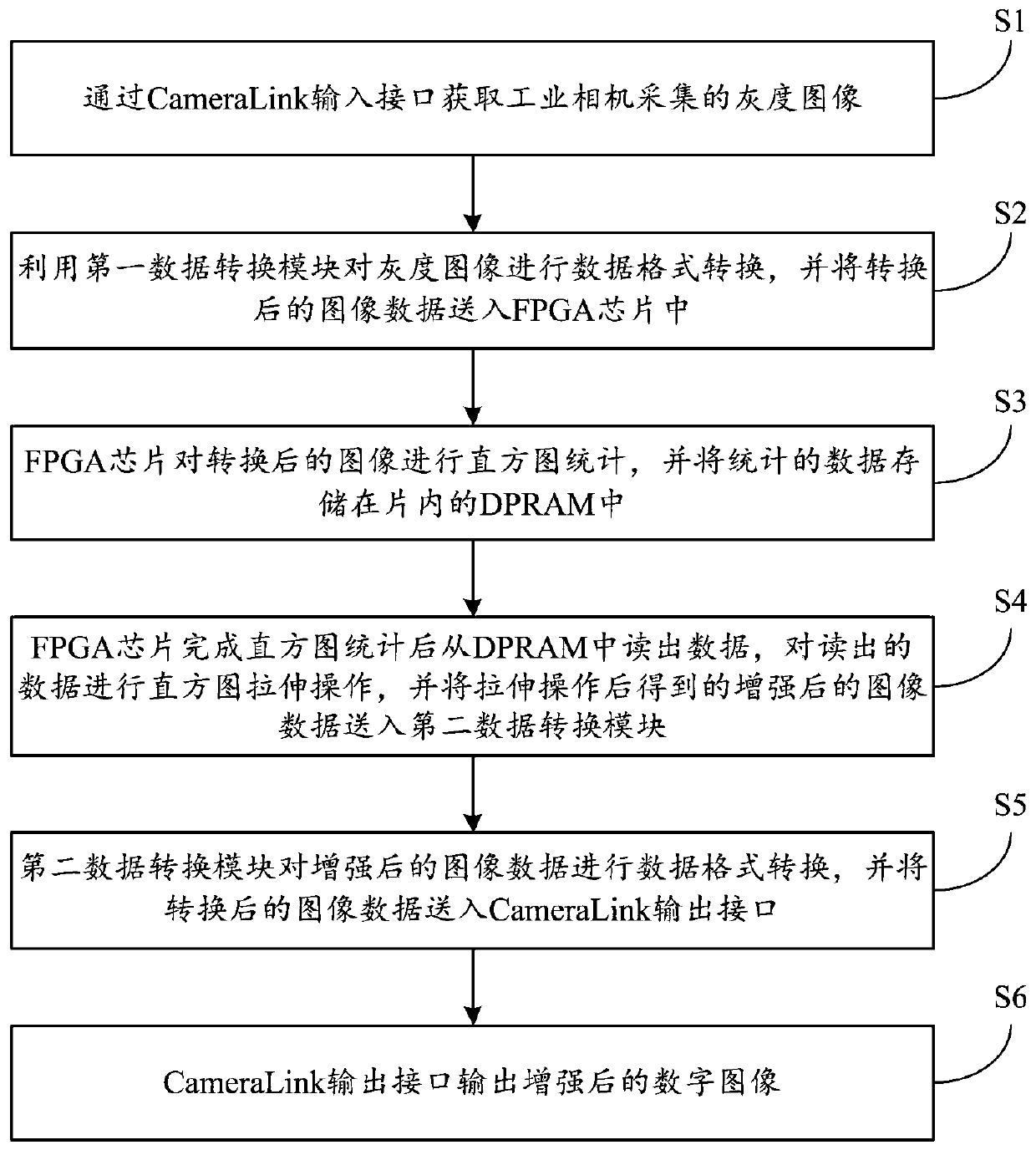

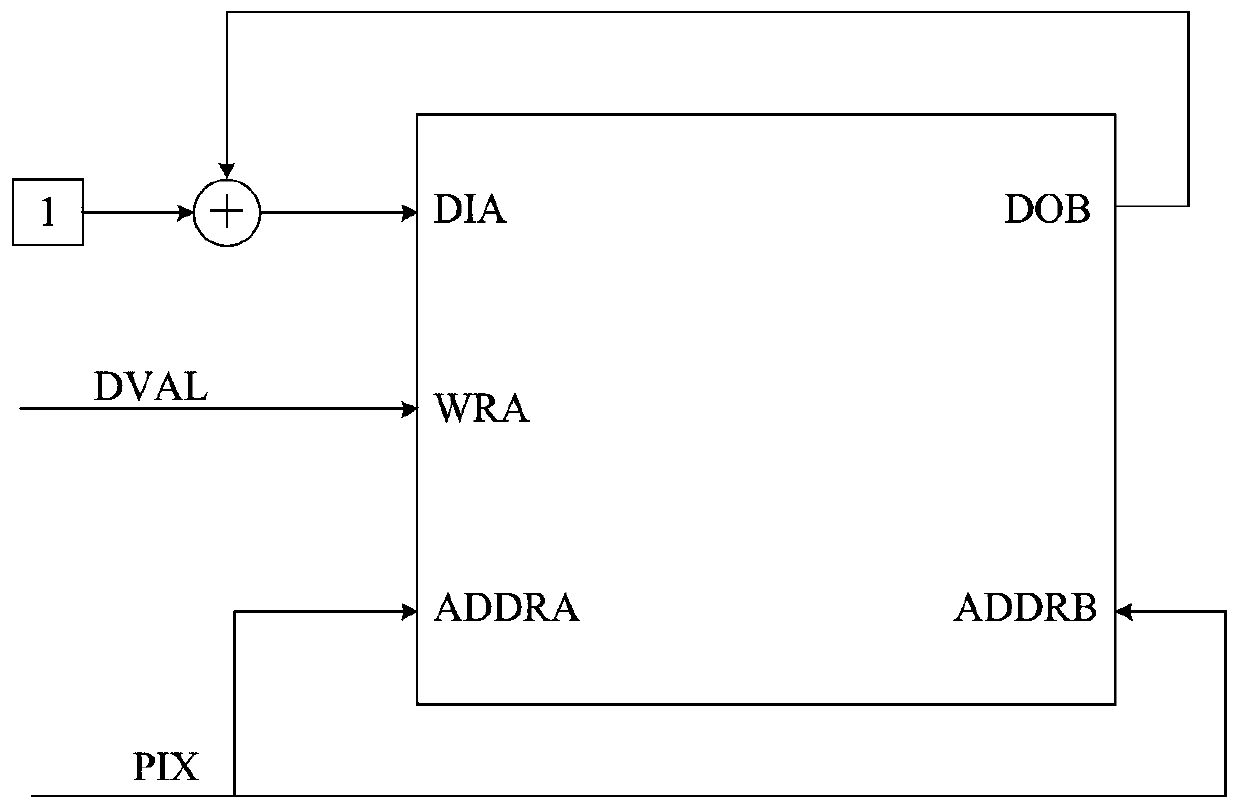

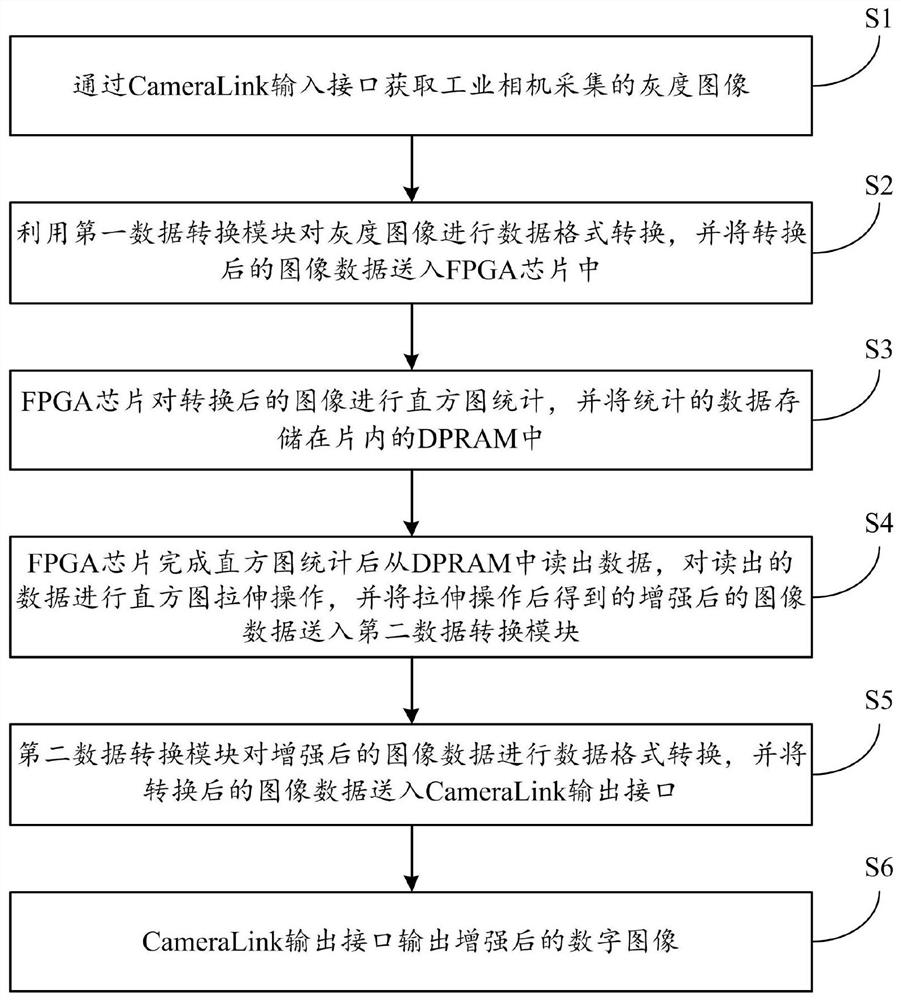

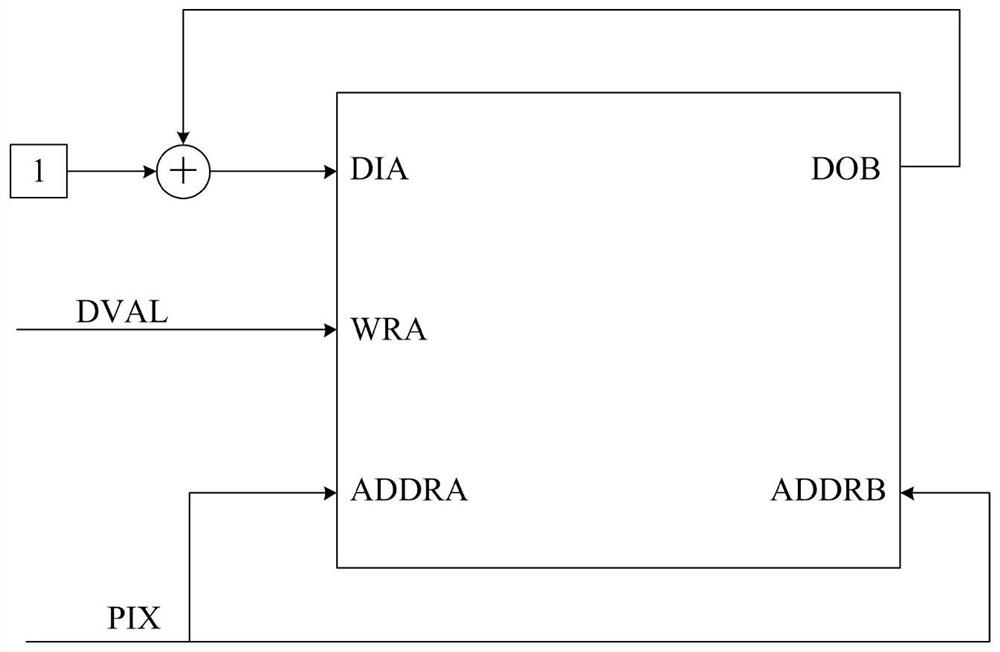

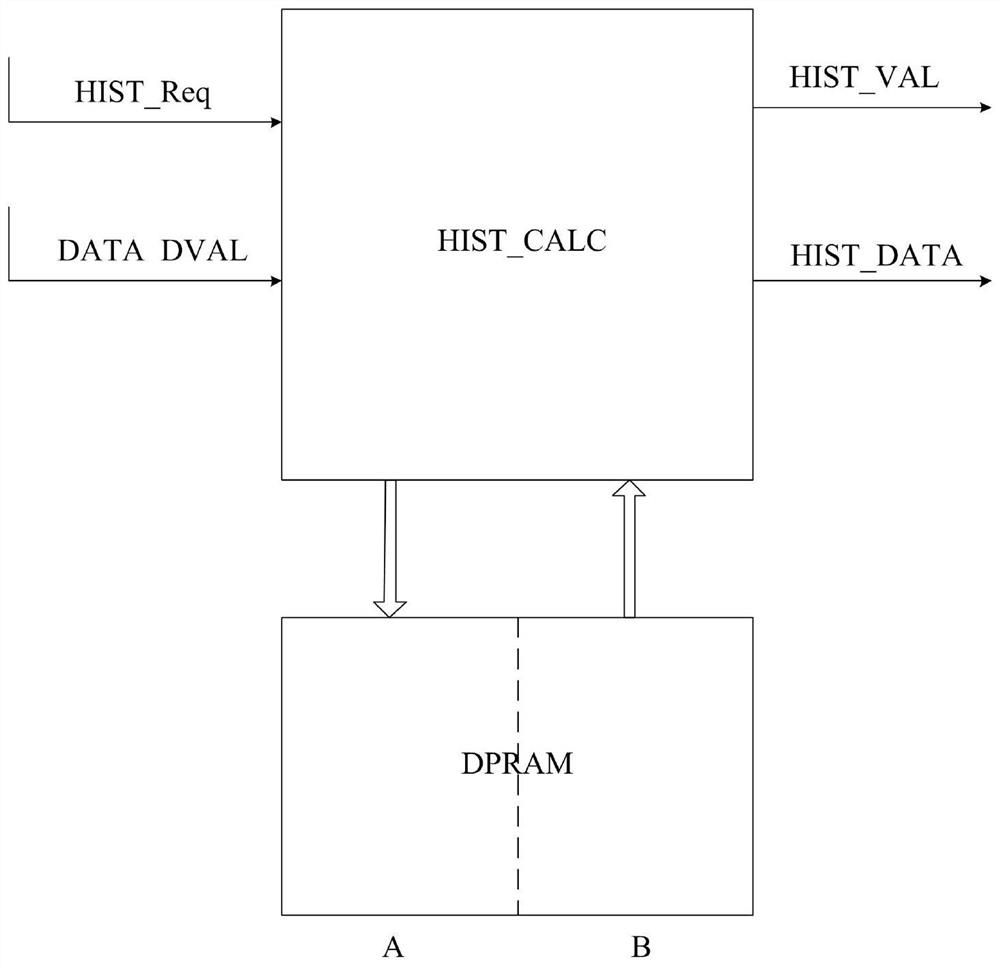

Real-time digital image enhancement method and system

ActiveCN110996005AProcessing speedSave internal resourcesTelevision system detailsColor television detailsComputer hardwareData transformation

The invention relates to a real-time digital image enhancement method and system. The invention belongs to the technical field of digital image processing. The invention discloses a method for processing a digital image. Acquiring a grayscale image acquired by an industrial camera; the data is transmitted to the first data conversion module through the Camera Link input interface for serial-parallel conversion; then, the signals are transmitted into an FPGA chip; and the FPGA chip is used as a core processing unit and a main control unit to carry out logic sequential control on the whole system, processes the images, transmits the image data to the second data conversion module to carry out serial-parallel conversion again, and outputs the enhanced images through the Camera Link output interface. The method is mainly realized by utilizing internal resources of the FPGA, and data processing is carried out by adopting an assembly line mode, so that the image processing speed is improved,less resources are occupied, and the power consumption of the FPGA is reduced.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

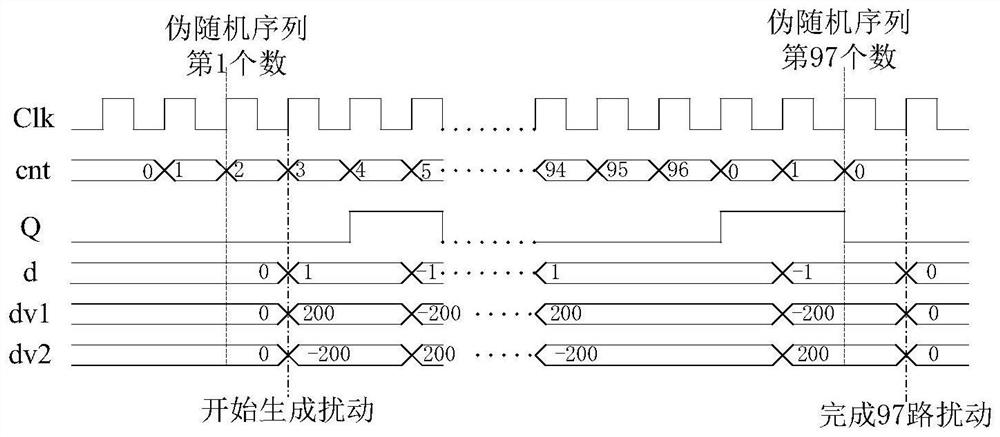

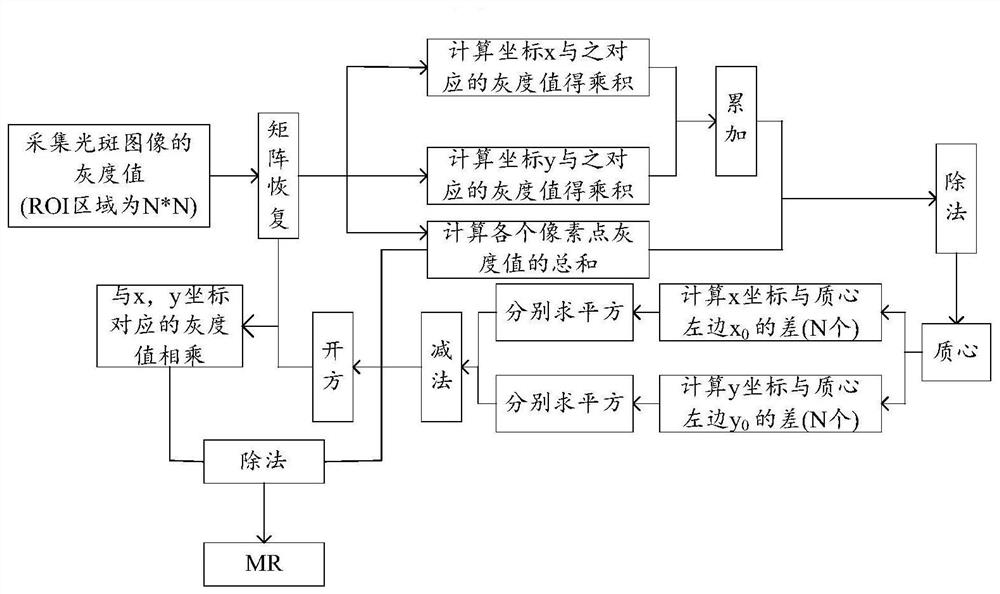

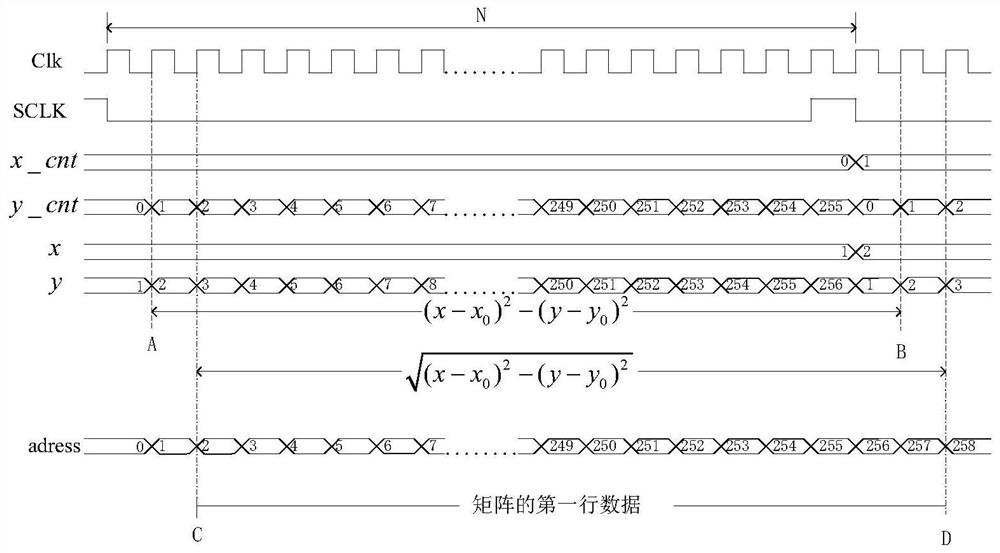

Realization method of adaptive optics spgd control algorithm based on fpga

ActiveCN111103686BEasy to implementFlexibleImage enhancementRandom number generatorsPerformance indexGradient estimation

The present invention is a kind of realization method of adaptive optics SPGD control algorithm without wavefront detection based on FPGA, and its realization steps are as follows: random perturbation perturbation module, by means of Matlab software (not limited to Matlab) produces multiple groups of pseudo-random sequences, in FPGA Multiply each set of sequences by the disturbance voltage and add corresponding signs to generate positive and negative disturbances; the performance index function calculation module selects the average radius MR‑Mean Radius of the far-field spot as the performance index function; calculates the deformation mirror voltage control module , after the disturbance is applied, the image data is collected and the performance index function is calculated, and the calculated performance index function is used for gradient estimation, and then the control voltage is calculated according to the formula. The method of the invention has a wide range of applications and is suitable for any adaptive optical system with any number of units, improves the generality of the way FPGA implements the SPGD control algorithm, and ensures the correction capability of the adaptive optical system without wavefront detection.

Owner:JIANGSU OCEAN UNIV +1

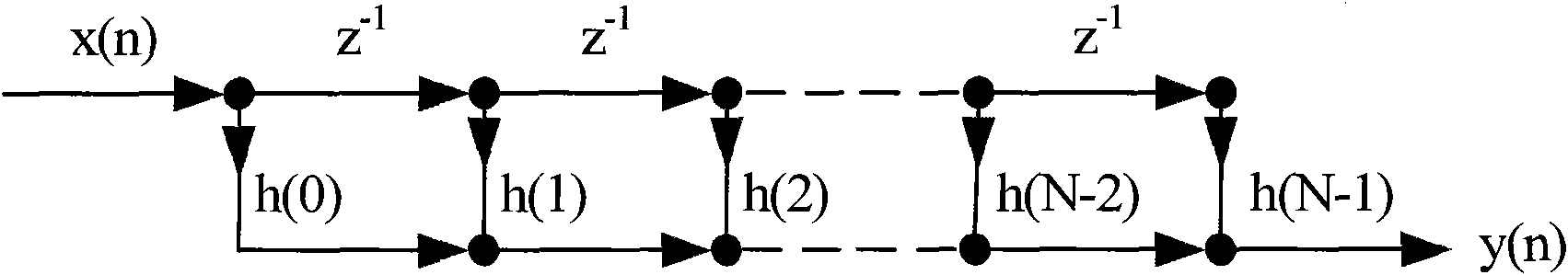

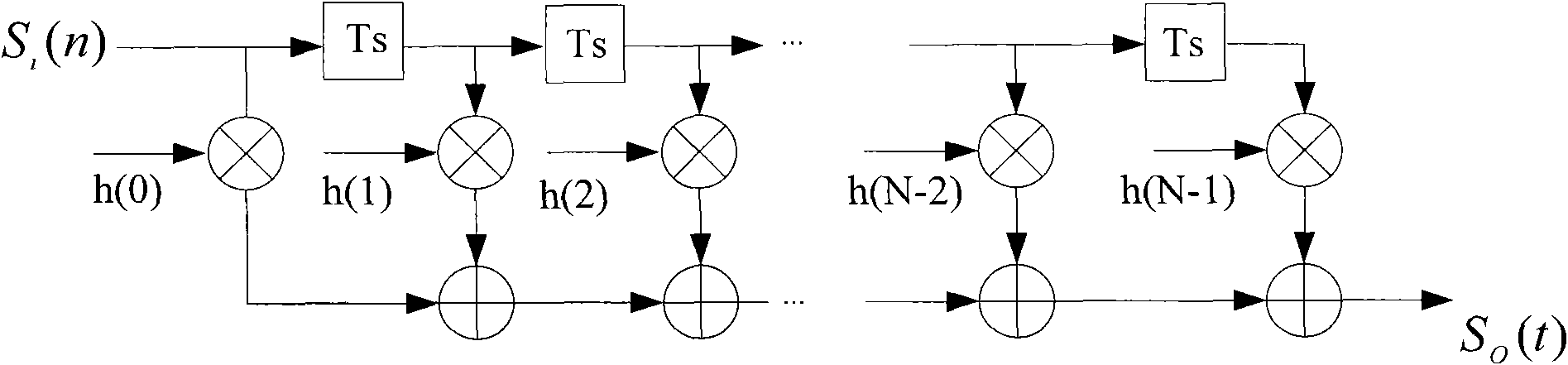

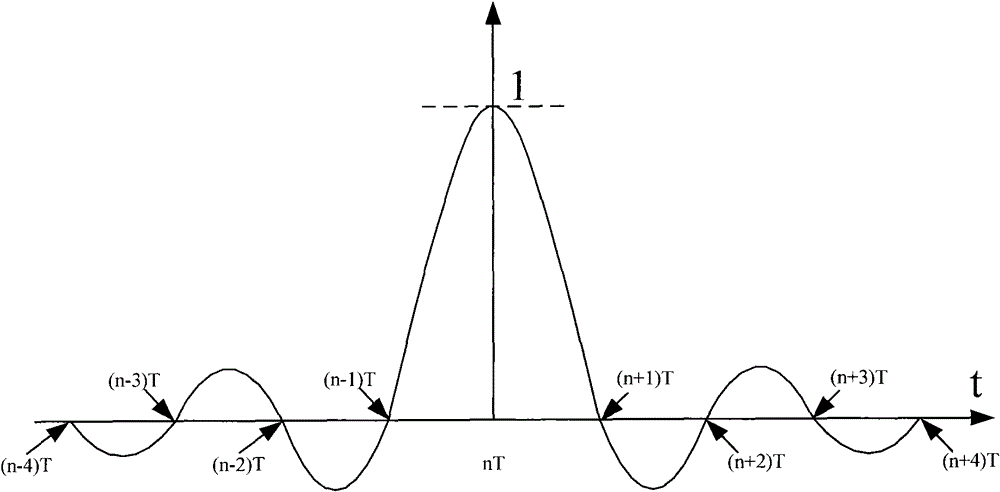

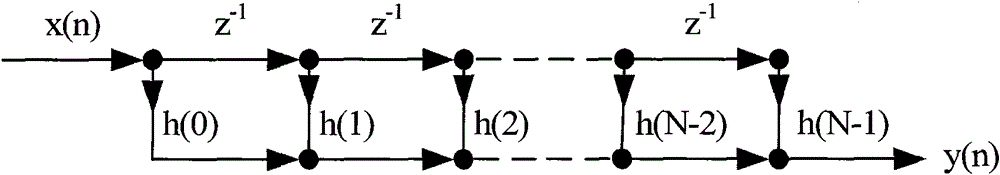

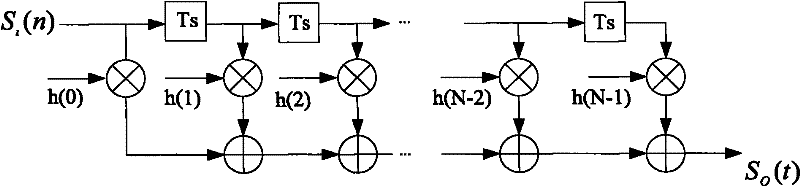

A design method for limited impact response filter

InactiveCN101150306AReduce usageSave internal resourcesDigital technique networkFinite impulse responseImpulse response

This invention discloses a designing method for a limit impulse response filter, which expresses cofficients of a FIR filter in a binary system mode and displays it to a cofficnent array and then splits it to generate several new sub-arrays with a special rule, in which, each sub-array corresponds to a sub-shearch list, the output value of which is composed of corresponding bits of its input data directly, so a 1ut unit is not needed, finally, outputs of the sub-lists are accumulated to get output value of a total list.

Owner:SHANDONG UNIV

A rs coding system based on cmmb and its realization method

ActiveCN103001736BSave internal resourcesReduce computationError preventionInternal memoryComputer architecture

The invention discloses a CMMB (China mobile multimedia broadcasting) based RS (reed-solomon) coding system and an implementing method thereof. The CMMB based RS coding system comprises an SDRAM (synchronous dynamic random access memory) controller, a byte interleaver, an internal memory and an RS coder, wherein the SDRAM controller is used for receiving information code streams and storing accessing check codes, the byte interleaver is used for subjecting accessing information codes and the check codes to byte interleaving, the internal memory is used for caching the accessing information codes and the check codes, and the RS coder is used for coding the information codes. The implementing method includes that the SDRAM controller receives the information code streams, the information codes are subjected to byte interleaving by the byte interleaver, the information codes interleaved are stored in the internal memory and are read and encoded and the like. By the CMMB based RS coding system and the implementing method thereof, internal resources of an FPGA (field programmable gate array) is effectively saved, and operation load is reduced, so that the problem about time sequence of the FPGA is solved, the low-end FPGA can be utilized for design, and normal work in complicated environment can be guaranteed.

Owner:ALLWIN TELECOMM

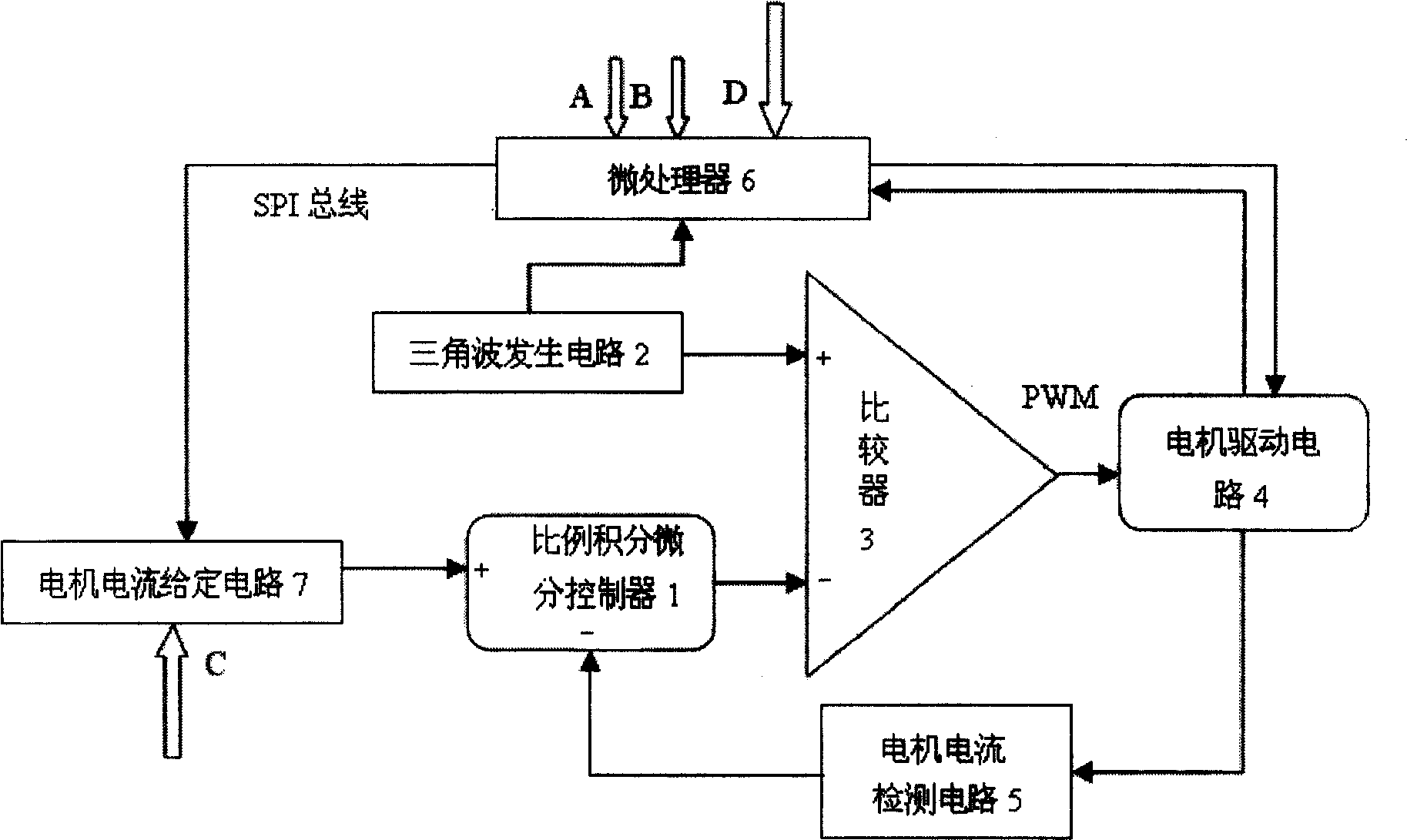

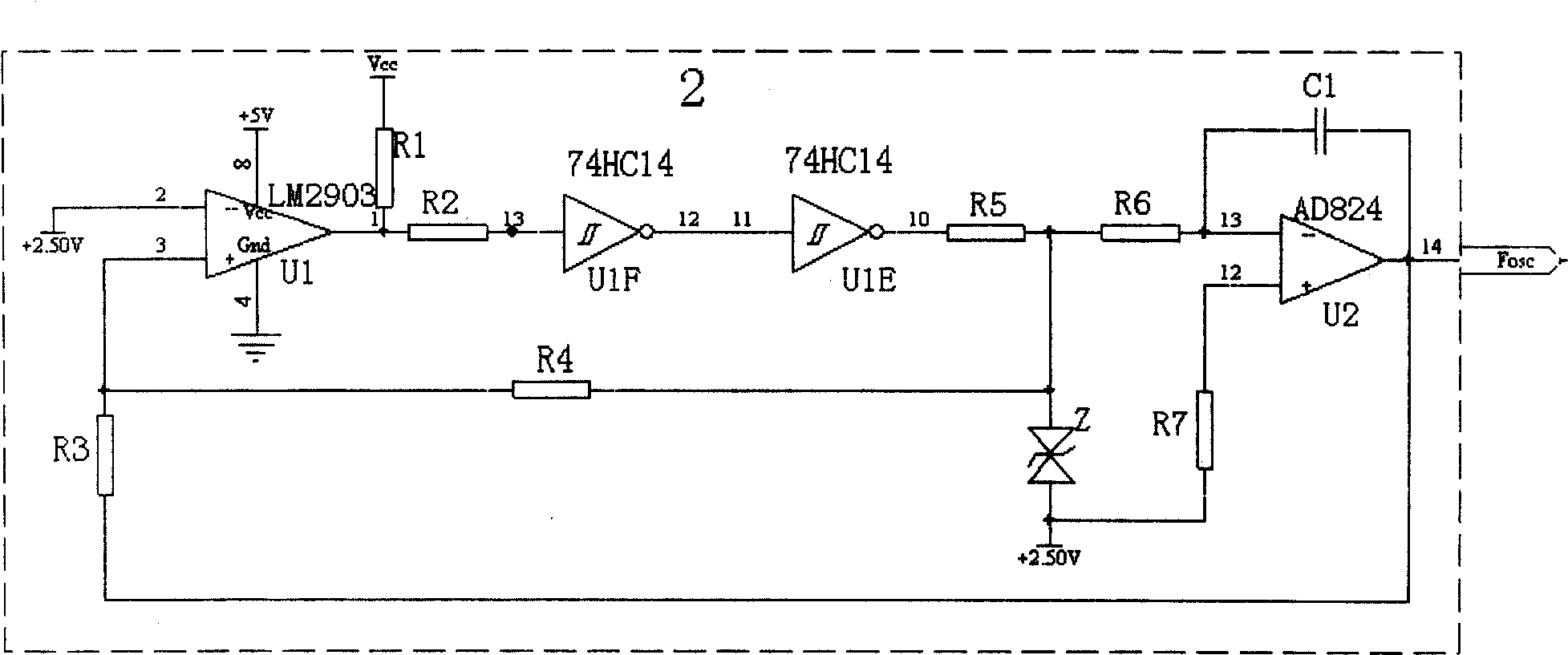

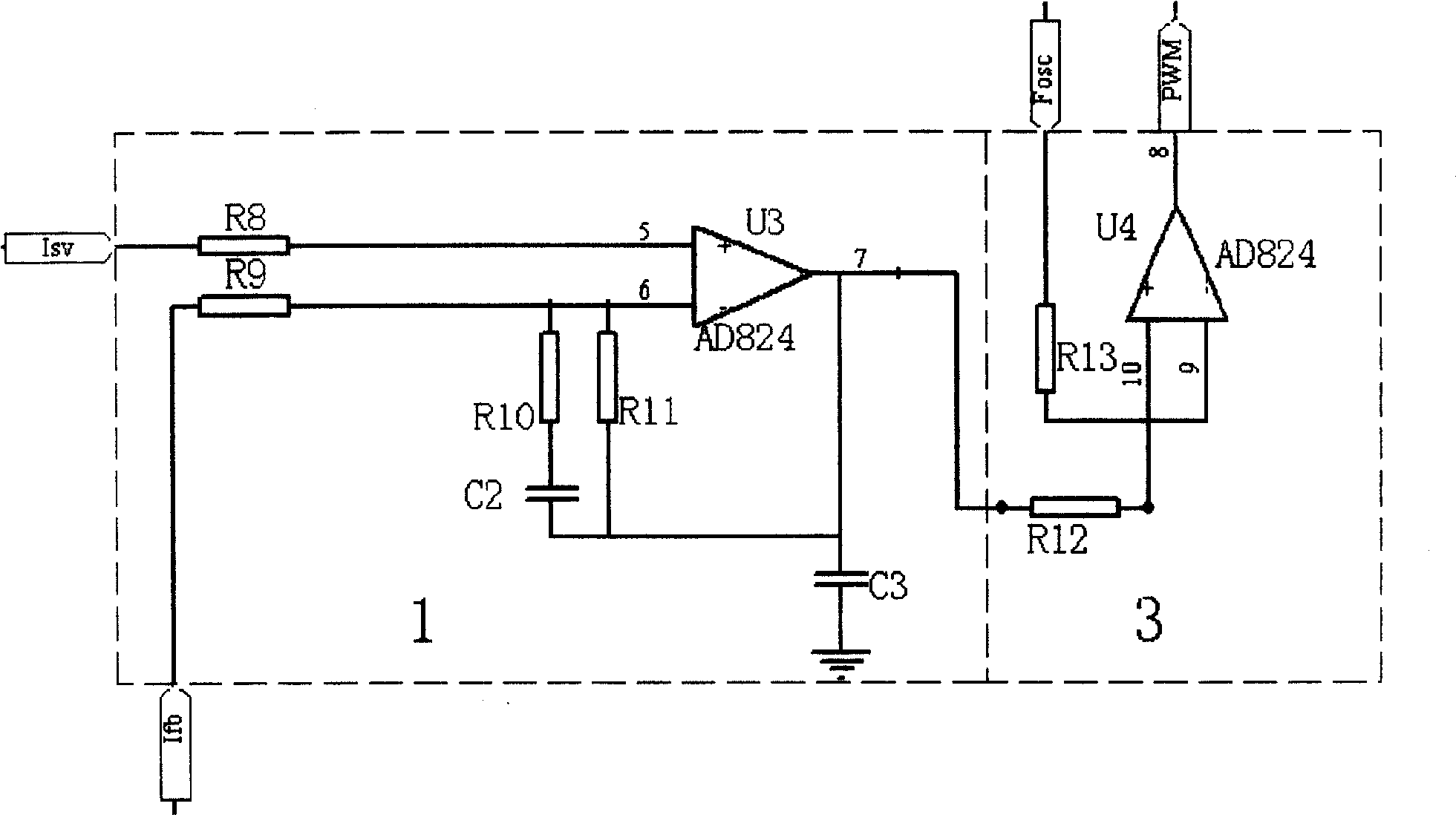

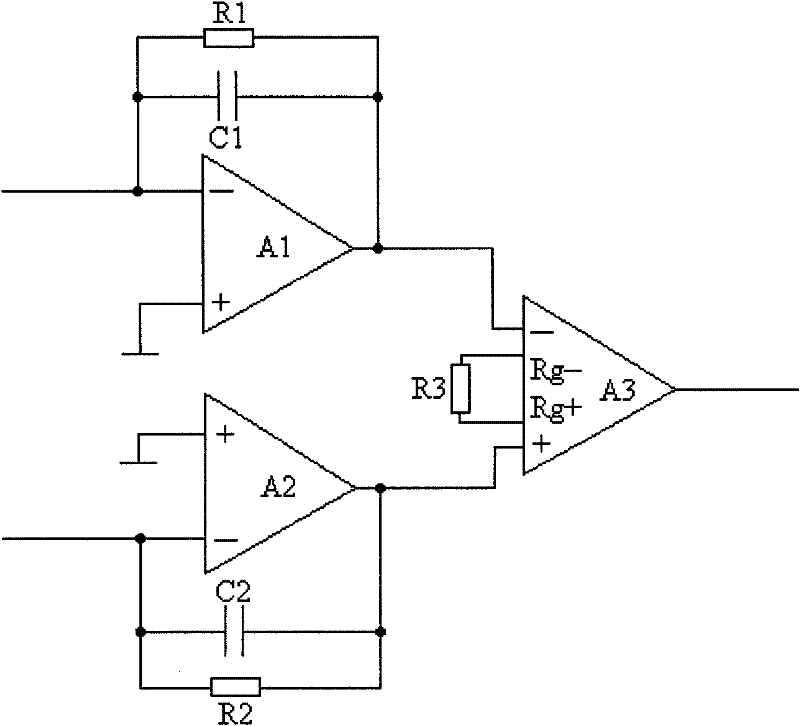

Electrical servo power-assisted steering controller

InactiveCN100514838CSave internal resourcesLower performance requirementsAC motor controlElectrical steeringMotor driveSteering control

The present invention discloses an electrical servo steering controller, which comprises a PID controller, a triangular wave generating circuit, a comparator, a motor current detecting circuit, a motor drive circuit, a microprocessor and a motor current setting circuit. Wherein, the PID controller outputs an adjusting voltage to the comparator according to a difference between a motor current setting signal output by the motor current setting circuit and a motor current detecting signal output by the motor current detecting circuit. The comparator compares a triangular wave signal output by the triangular wave generating circuit to output a pulse width modulation signal to the motor drive circuit to control the motor current. The microprocessor works out and controls a resistance value of a digital potential device in the motor current setting circuit to modify a servo characteristic. An analog circuit is adopted to complete main functions. Besides, a special motor drive chip can provide a higher servo force and ensure a larger applicable scope, simple circuit control, wonderful steering feeling and higher reliability.

Owner:ZHEJIANG UNIV +1

A FPGA-based method and system for preventing misoperation of relay protection

ActiveCN107171297BImprove accuracyImprove reliabilityEmergency protective circuit arrangementsSoftware engineeringRelay

The invention provides an FPGA-based method and system for preventing relay protection misoperation. A CPU periodically transmits protection starting / outlet data to an FPGA, and when the FPGA detects that the protection starting / outlet data is valid, a starting / outlet relay is controlled to act; when the FPGA detects that a protection outlet state signal is invalid, and after a timed non-continued set time, the FPGA detects that the protection starting / outlet data is valid, the starting / outlet relay is controlled to act; or when the data is invalid, and after the timed non-continued set time, the starting / outlet relay is controlled not to act. By virtue of the method and the system, the protection starting / outlet data accuracy and relay protection action reliability are improved; in addition, the protection starting and outlet signals are sent out directly through the FPGA, without through an outlet plug-in, so that multilayer data transfer is reduced, and speed, reliability and accuracy of relay protection are improved; and furthermore, the periodical judgment on the protection data is simple in logic, troublesome signal content analysis is omitted, and the FPGA internal resource is saved.

Owner:XUJI GRP +3

A real-time digital image enhancement method and system

ActiveCN110996005BProcessing speedSave internal resourcesTelevision system detailsColor television detailsImaging processingData transport

The invention relates to a real-time digital image enhancement method and system, belonging to the technical field of digital image processing. When processing a digital image, the grayscale image collected by an industrial camera is obtained and transmitted to a first data conversion module by a CameraLink input interface for processing. The serial-to-parallel conversion is then transmitted to the FPGA chip. The FPGA chip acts as the core processing unit and the main control unit to control the logic timing of the entire system, process the image, and then transmit the image data to the second data conversion module for further processing. After a serial-to-parallel conversion, the enhanced image is output through the CameraLink output interface. The present invention is mainly implemented by utilizing internal resources of the FPGA, and adopts a pipeline method for data processing, thereby improving the image processing speed, occupying less resources, and reducing the power consumption of the FPGA.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

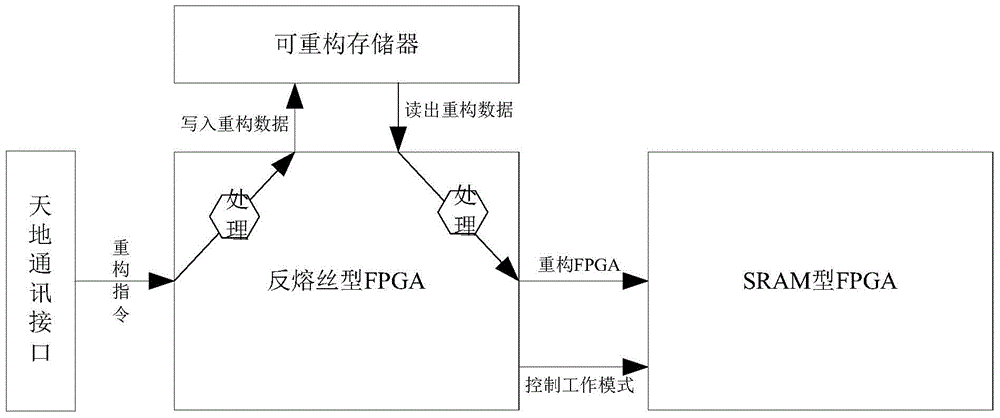

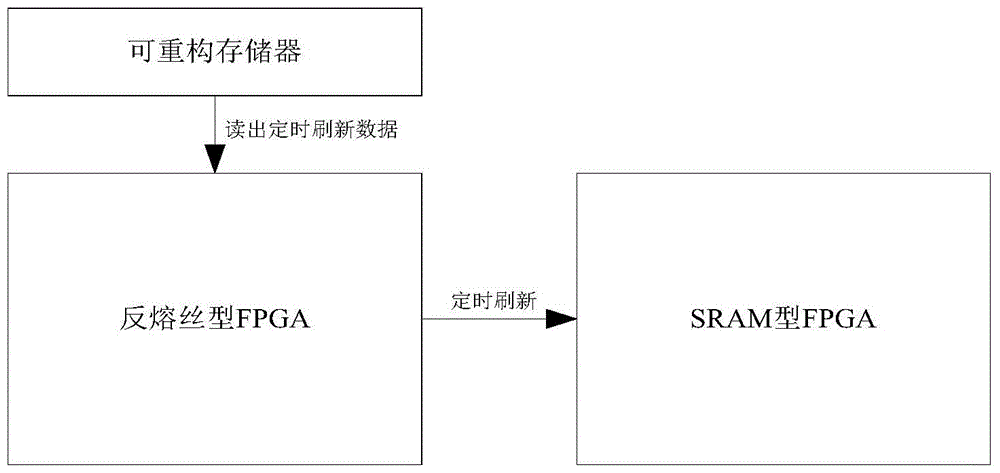

An On-orbit Reconfigurable Method

ActiveCN104063292BSave internal resourcesImprove reliabilityRedundant operation error correctionSingle event upsetField-programmable gate array

The invention relates to an on-track reconfigurable method based on anti-fuse FPGA (field programmable gate array) and SRAM (static random access memory) FPGA because the SRAM FPGA is likely to have single event upset on the track, but the anti-fuse FPGA has the advantages of less internal resource, high reliability and applicability to the on-track control. According to the method, the anti-fuse FPGA and the SRAM FPGA are combined to process the on-track reconfiguration, the anti-fuse FPGA is used for receiving the reconfiguration data uploaded by the ground so as to reconfigure the function of the SRAM FPGA, so that not only can the stability and reliability in work of the SRAM FPGA be guaranteed, but also the on-track updating and maintenance requirement of a spacecraft can be met.

Owner:NO 513 INST THE FIFTH INST OF CHINA AEROSPACE SCI & TECH

Data processing system and data processing method

ActiveCN100552660CSpeed is not affectedSave internal resourcesElectric digital data processingData processing systemMultiplexing

The invention discloses a data processing system and a data processing method, comprising: the address and data multiplexing bus pins of the CPU processor are connected with the data bus pins of the data storage device, and the CPU processor controls the Bus pins, addresses and data multiplex bus pins to send control commands and address information; after receiving the control commands and address information, the converter converts them into control signals and address signals in the format of the data storage device and sends them to the data storage device ; The data storage device responds to the data operation performed by the CPU processor through the address and data multiplexing bus pins and the data bus pins of the data storage device according to the control signal and the address signal. Using the invention, the data operation speed of the CPU processor to the peripheral devices is not affected by the converter, and the data does not need to be processed by the converter during data operation, which saves the internal resources of the converter.

Owner:广东北斗南方科技有限公司

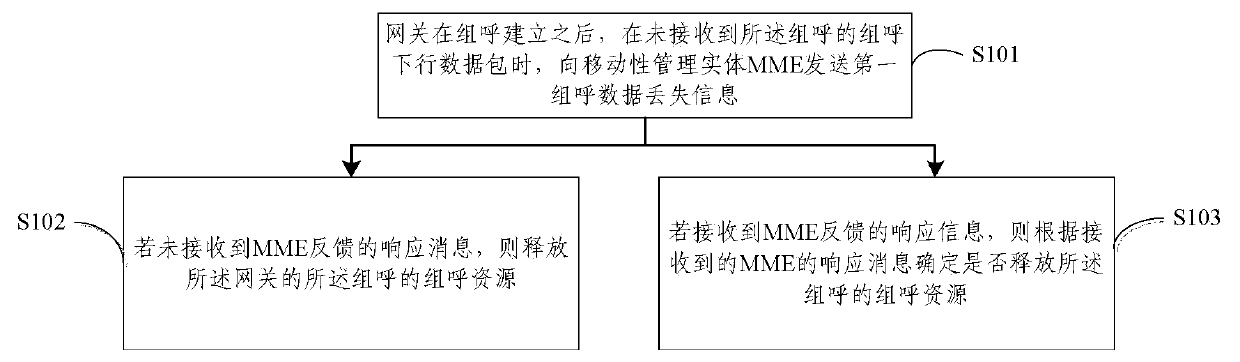

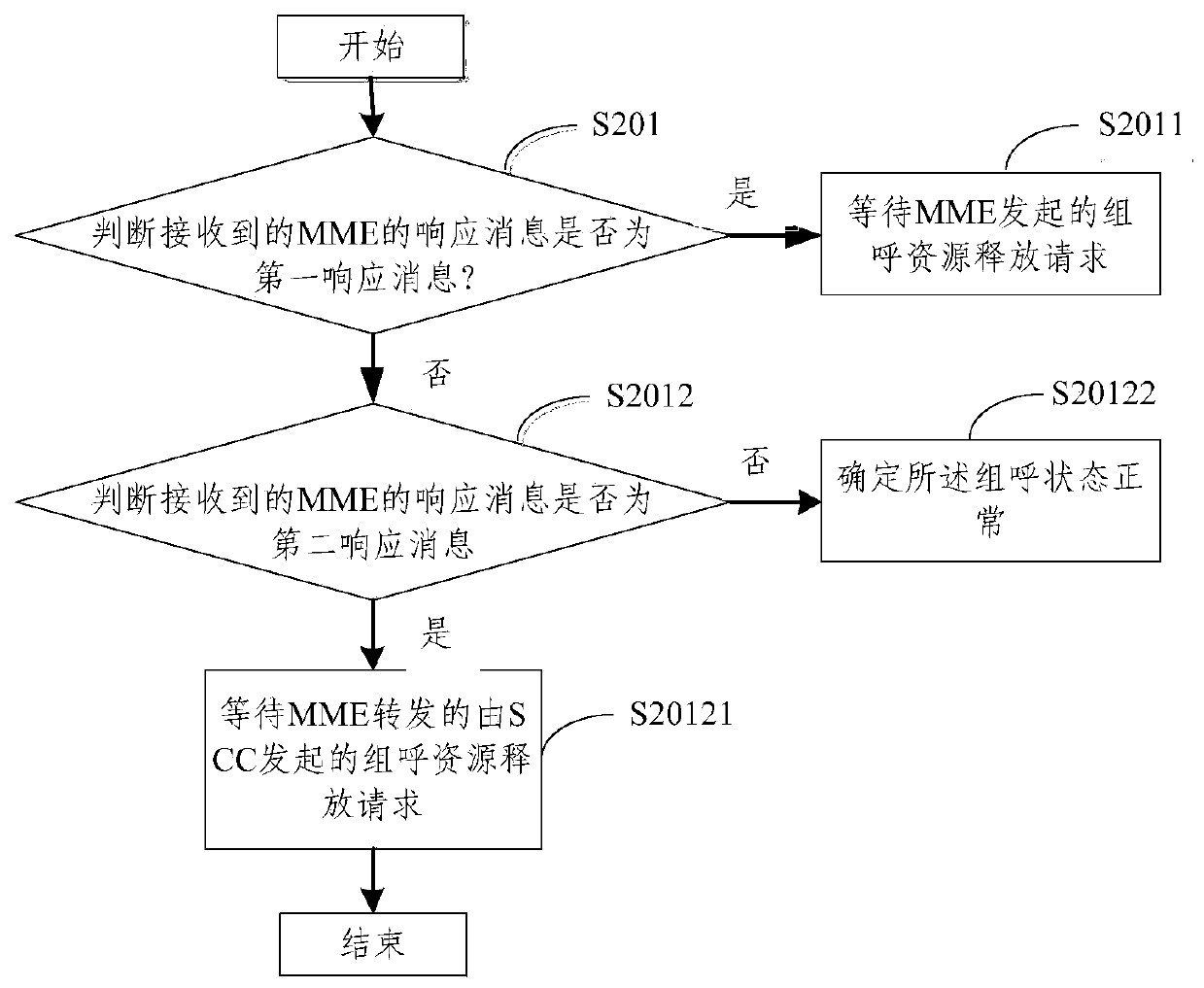

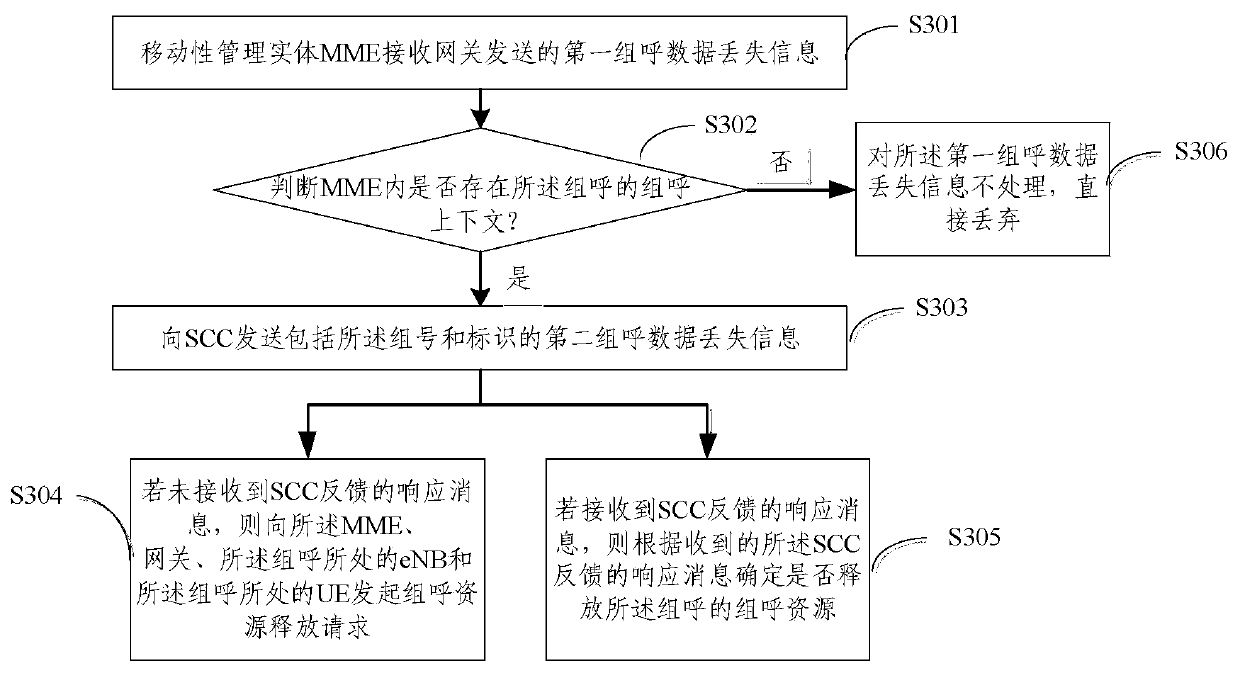

Group call service processing method and system of a broadband trunking communication system

InactiveCN106658423BSave internal resourcesBroadcast service distributionCommunications systemBroadbanding

The invention provides a group call service processing method of a broadband cluster communication system. The method comprises that when a group call is established but a downlink data packet of the group call is not received, a gateway sends first group call data loss information including the group number and identification of the group call to a mobility management entity (MME); if response information back fed by the MME is not received, resources of the group call of the gateway are released; and if the response information back fed by the MME is received, whether to release the resources of the group call is determined according to the received the response information of the MME. According to the method, the group call is established, whether the gateway includes downlink data of the group call is monitored, signaling interaction with the MME and an SCC is made when there is not downlink data of the group call, whether the group call is normal is determined, and a resource release mechanism is triggered when the group call is abnormal; and thus, bandwidth resources and internal resources of logical network elements are saved effectively. The invention also relates to a group call service processing system of the broadband cluster communication system.

Owner:POTEVIO INFORMATION TECH CO LTD

Panoramic video cylindrical image storage method and system

InactiveCN103093485BEasy to readSave resourcesMemory adressing/allocation/relocationInternal memoryData segment

The invention provides a full view video cylindrical surface image storage method and a system. The method includes that pixel data is received by row and first in,first out (FIFO) is used for caching. Whether an FIFO is full of the caching pixel data or not is judged. If it is full, a row of pixel data is continuously read out from the FIFO and the cylindrical surface transformation is carried out. New coordinates are obtained by calculating each pixel and the pixel addresses of each pixel are calculated. Data after the transformation of the cylindrical surface is divided into a plurality of data sections, wherein, among the divided data sections, the pixel address in every data section is consecutive and the next data sections belong to different rows. BURST is formed by the pixel numbers in the data section, the BURST proruption length in the internal memory, the storage unit digit of the internal memory and the pixel address of the first pixel in the data sections. The composed BURST data is stored into the internal memory. The full view video cylindrical surface image storage method and the system achieve the transformation of the cylindrical surface of the video image as well as improve the bandwidth availability ratio.

Owner:GUANGDONG VTRON TECH CO LTD

A kind of nand Flash bad block management method, device and memory

ActiveCN106649137BDoes not take up storage spaceSave internal resourcesMemory adressing/allocation/relocationComputer architectureRandom access memory

The invention discloses a Nand Flash bad block management method and device and a memory. The bad block management method comprises the steps of establishing a random access memory RAM in an FPGA module with the same block number as a Nand Flash module, adopting an address of each RAM as a block address of each block in the Nand Flash module, then, storing a detected block state of the each block in the Nand Flash module into a RAM of the corresponding address so that corresponding writing and reading operation can be conducted according to the address of the each RAM and block state data stored in the RAM. According to the Nand Flash bad block management method and device and the memory, the address of the RAM is adopted as the block address of the each block in the Nand Flash module, and thus the space occupied by the RAM storage block address is saved; moreover, the RAM address needs to be shown with only one counter, thus the storage space of the FPGA module is not occupied, and the inner resource of the FPGA module is further saved.

Owner:BEIJING LUSTER LIGHTTECH

A digital oscilloscope with configurable multiplexing digital interpolation and digital filtering functions

ActiveCN102109542BImprove waveform refresh rateSave internal resourcesDigital variable displayFpga implementationsComputer module

The invention discloses a digital oscilloscope capable of configuring multiplex digital interpolating and digital filtering functions. The digital oscilloscope comprises a digital interpolating and filtering module realized by an FPGA (field programmable gate array), wherein, the digital interpolating and filtering module determines the current operation mode according to an interpolating / filtering gating signal, receives and stores input data, transfers the delayed data and filtering coefficients into a multiply and accumulate (MAC) calculating unit for calculation, and then transfers calculated results into a subsequent calculating unit; the subsequent calculating unit decides whether accumulation is required according to the current operation mode; when the operation mode is digital interpolating operation, the calculated results are directly taken as interpolation results to be output; and when the operation mode is digital filtering operation, digital filtering operation results are output after accumulation. The digital oscilloscope combines two signal processing modes such as digital interpolating and digital filtering into one by means of multiplexing mode configuration, thus effectively saving internal resources of the FPGA and being very economical and efficient.

Owner:RIGOL

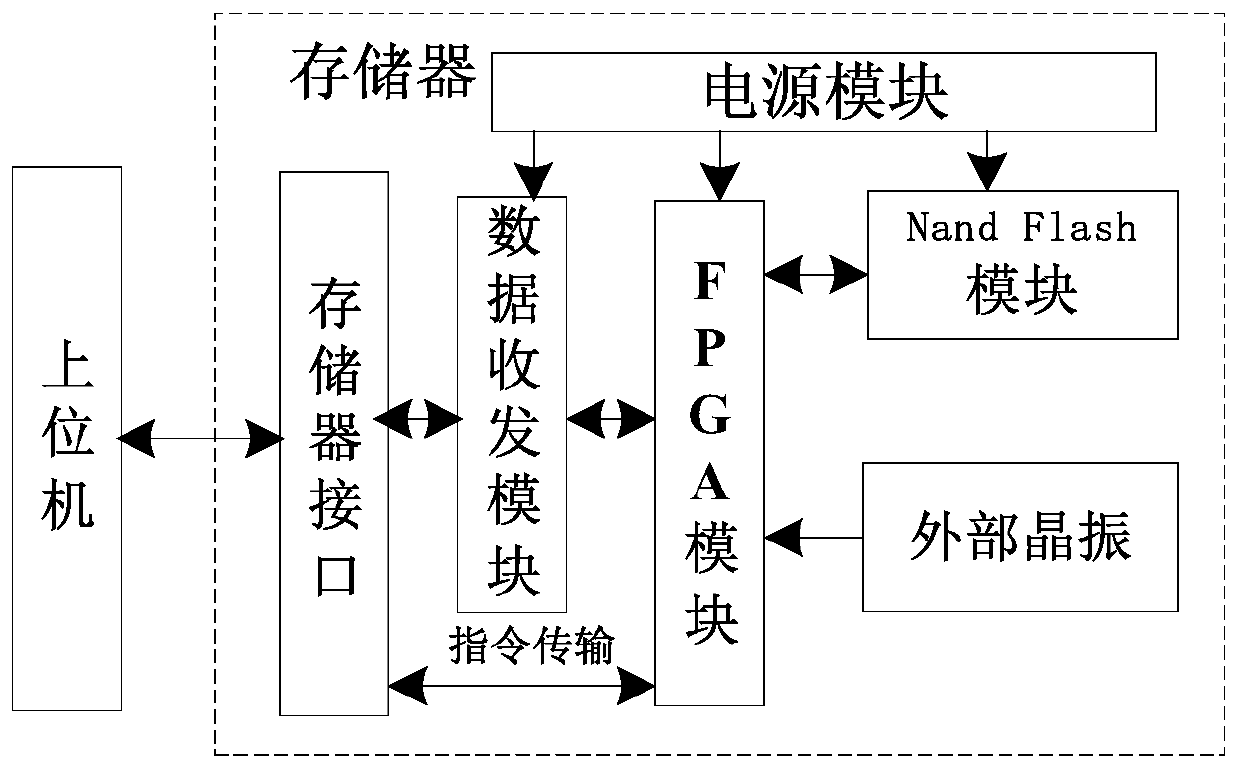

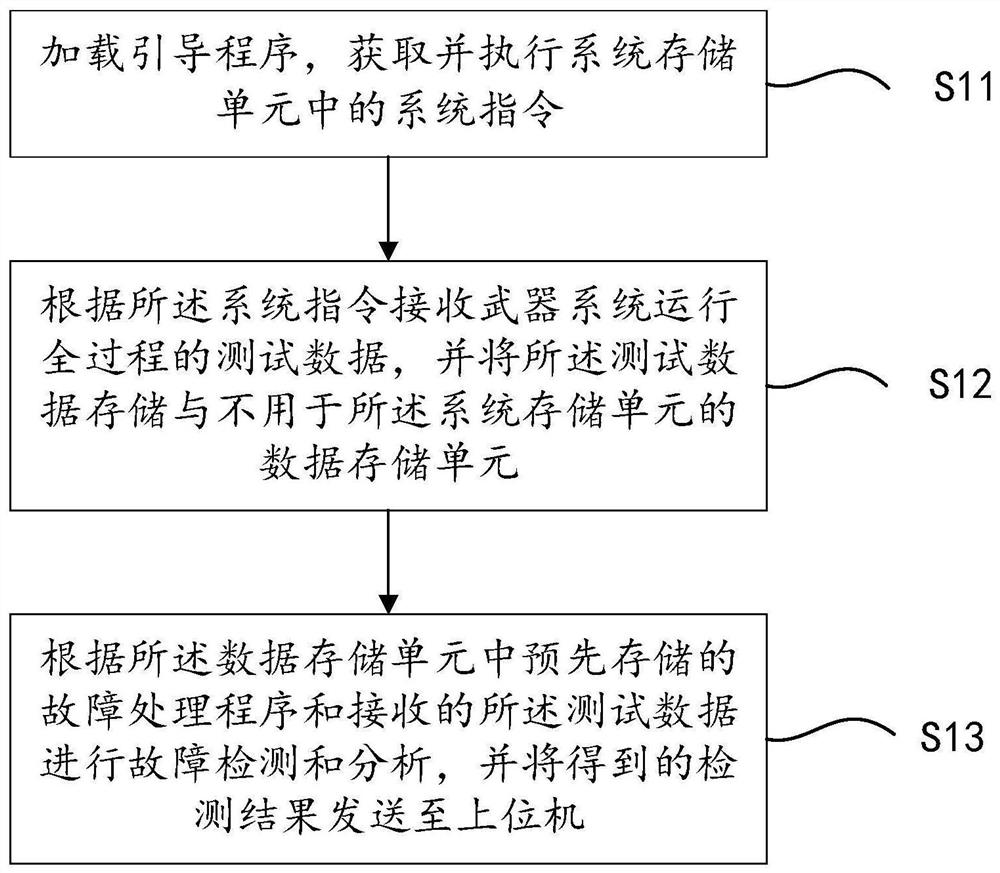

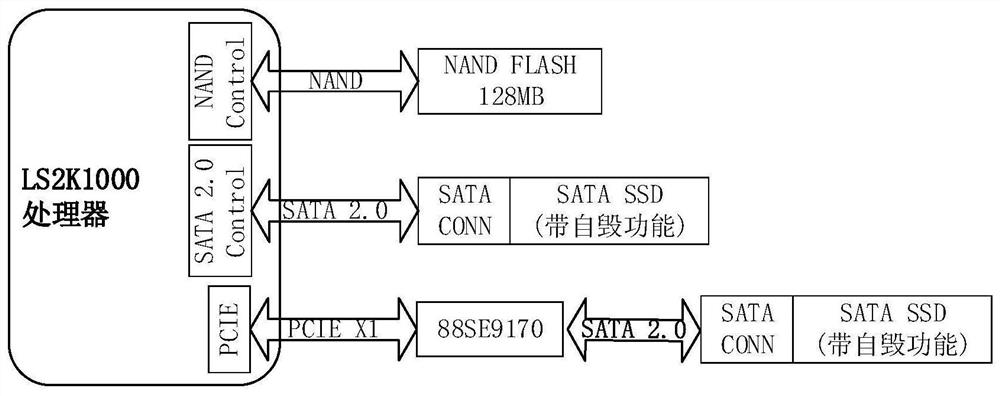

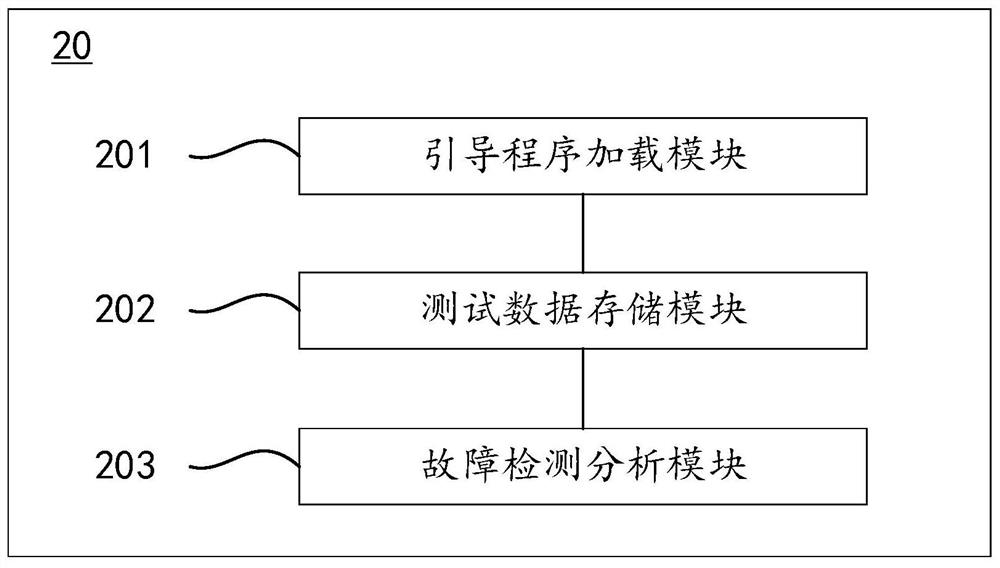

Weapon system test data processing method, device and equipment

PendingCN113836073ARapid positioningMeet diversityElectric digital data processingWeapon systemData store

The invention discloses a weapon system data processing method, and the method comprises the following steps: loading a bootstrap program, and acquiring and executing a system instruction in a system storage unit; receiving test data of the whole operation process of the weapon system according to the system instruction, and storing the test data in a data storage unit different from the system storage unit; carrying out the fault detection and analysis according to a fault processing program pre-stored in the data storage unit and the received test data, and sending an obtained detection result to an upper computer. The problems that in the prior art, data of the whole operation process of a weapon system cannot be stored, so that quick positioning cannot be conducted after faults occur in the operation process, and historical data cannot be analyzed and predicted can be solved.

Owner:HUBEI SANJIANG AEROSPACE WANFENG TECH DEV

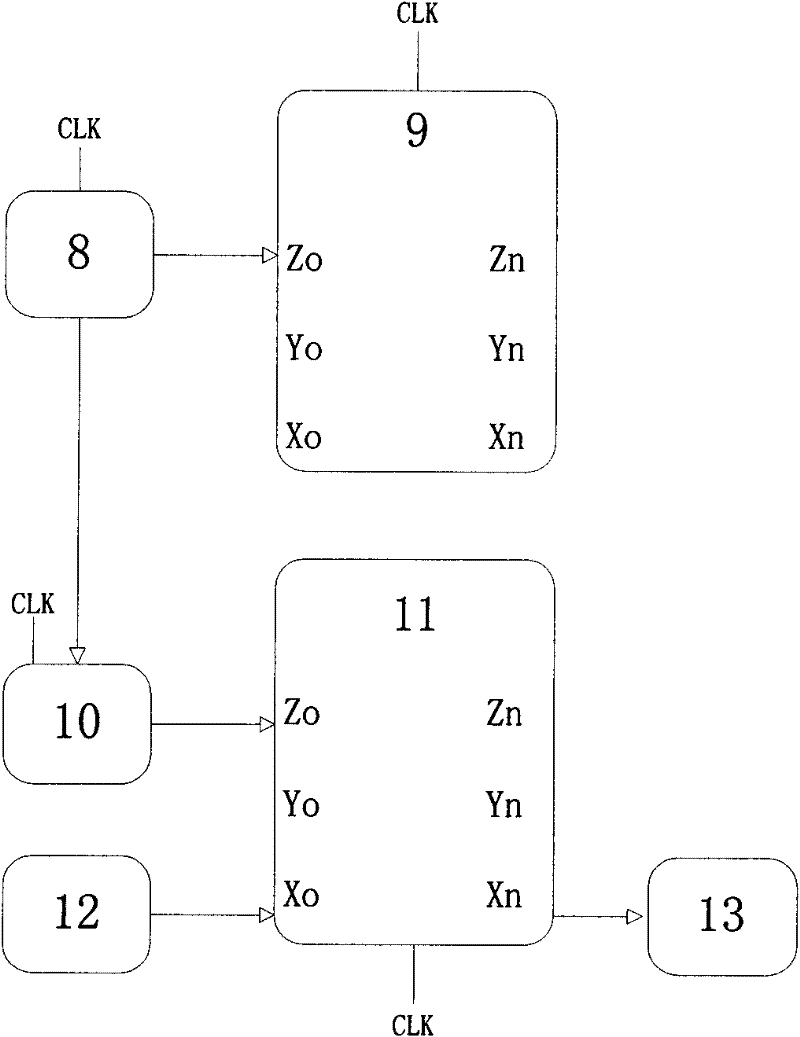

CORDIC algorithm-based capacitive micro-accelerometer signal detection device

InactiveCN101738495BOvercome the shortcomings of being susceptible to environmental factors such as temperatureSuppress low frequency noiseAcceleration measurementBandpass filteringAccelerometer

Owner:ZHEJIANG UNIV

Broadband digital receiver suited for pulse compression signal

InactiveCN101571588BSave internal resourcesReduce power consumptionWave based measurement systemsCode moduleFpga implementations

Owner:HARBIN ENG UNIV

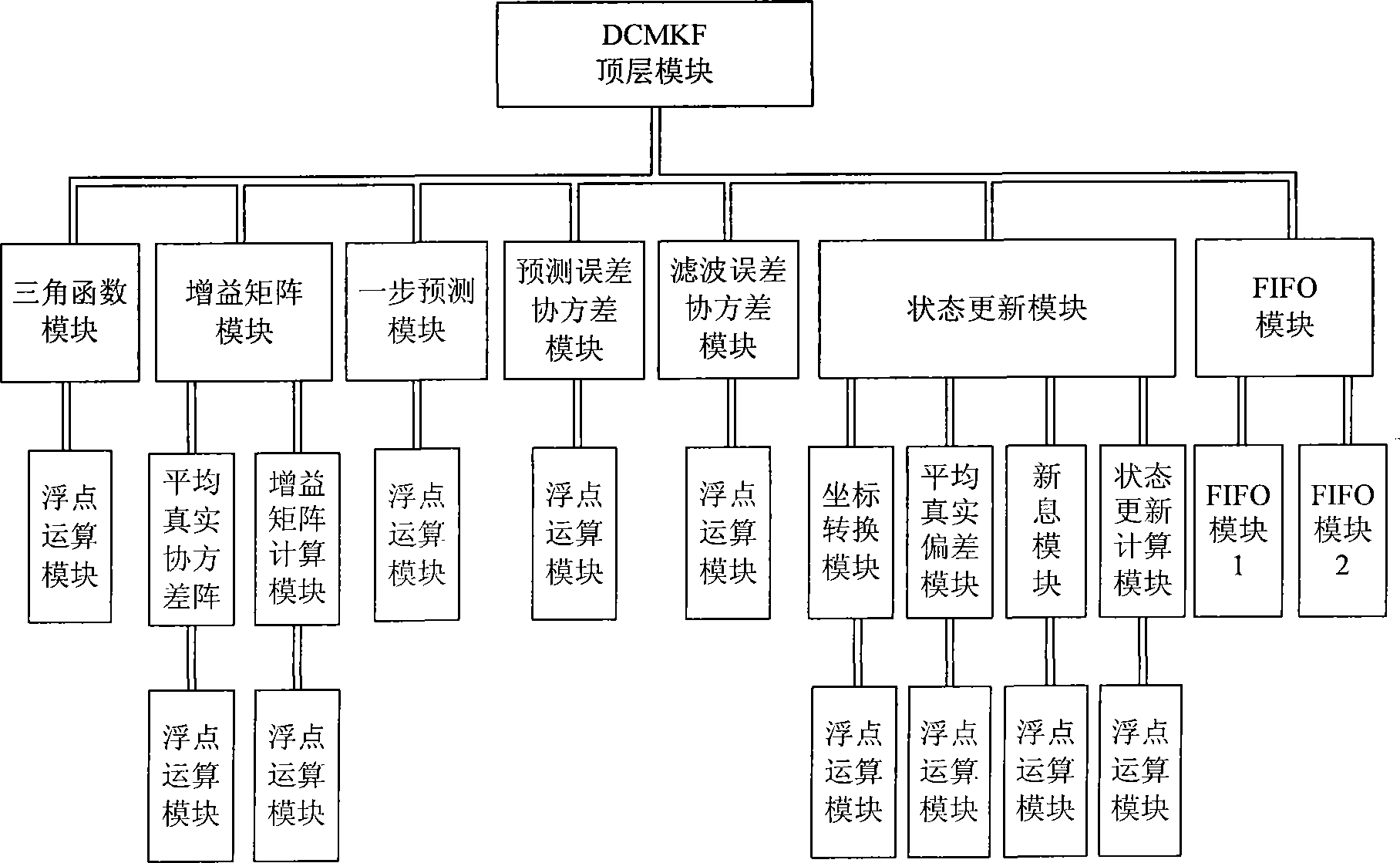

Method for designing DCMFK (Debiased Converted Measurement Kalman filter) based on FPGA (Field Programmable Gate Array)

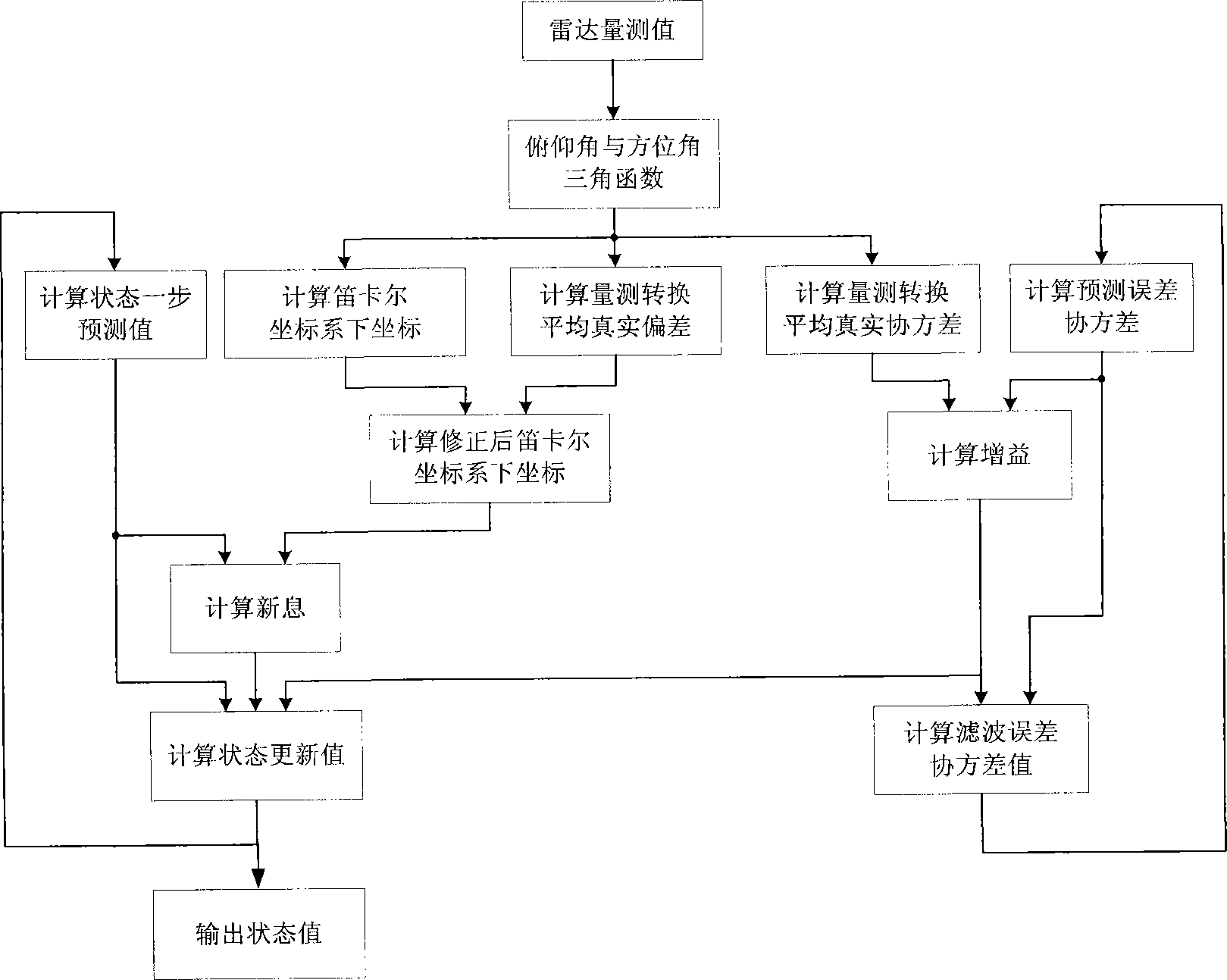

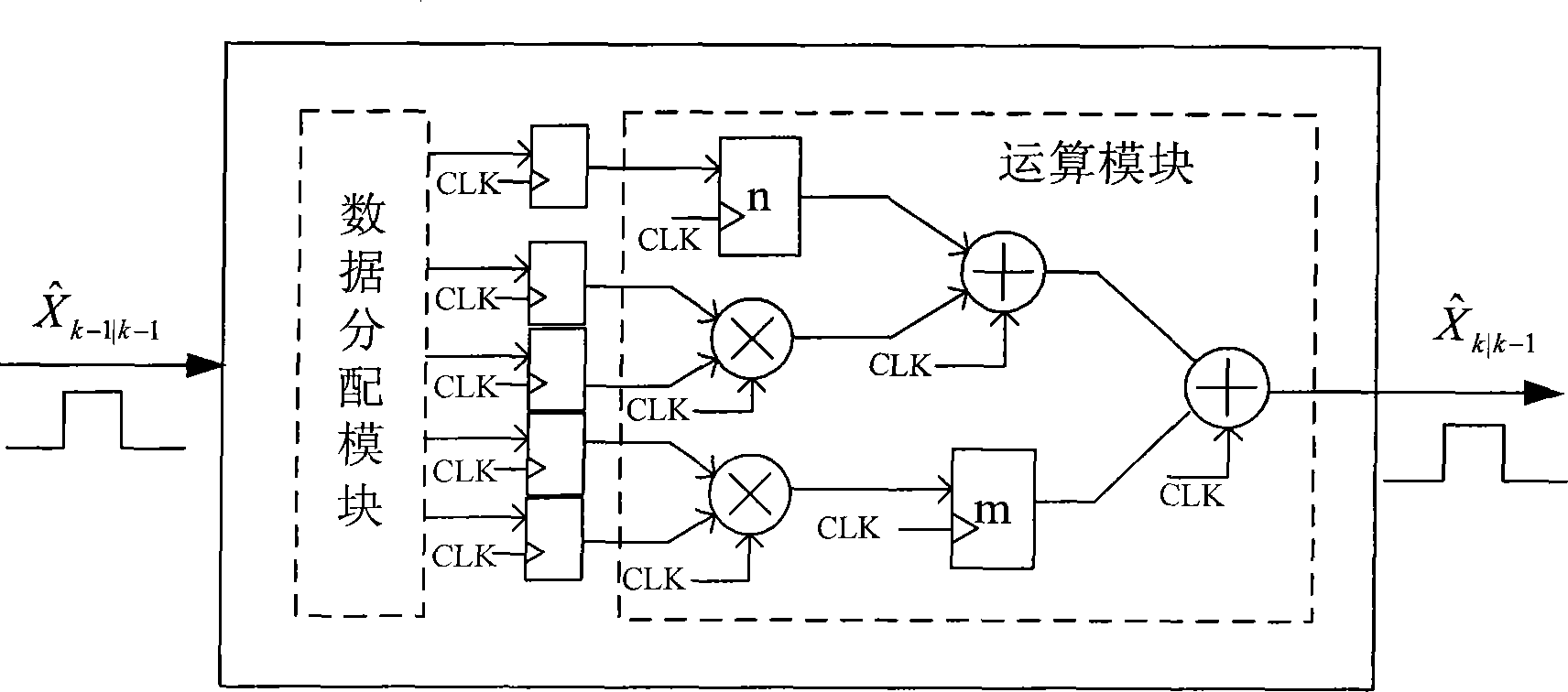

ActiveCN102064799BEasy to divideSave internal resourcesAdaptive networkRadio wave reradiation/reflectionKaiman filterFloating point

The invention discloses a method for designing a DCMFK (Debiased Converted Measurement Kalman filter) based on an FPGA (Field Programmable Gate Array). Firstly, a system of the DCMFK based on the FPGA is designed. A gain matrix module comprises an average real covariance submodule and a gain matrix submodule; a state update module comprises a coordinate transformation submodule, an average real deviation submodule, an innovation submodule and a state update submodule; a trigonometric function module, a one-step prediction module, a prediction error covariance module, a filter error covariance module, the average real covariance submodule, the gain matrix submodule, the coordinate transformation submodule, the average real deviation submodule, the innovation submodule and the state update submodule respectively invoke floating adding, subtracting, multiplying and dividing operation modules. A hierarchical design is adopted in the method, modules at the bottom layer realize input by utilizing a VHDL (Very High Speed Integrated Circuit Hardware Description Language), and a schematic diagram input manner is adopted by the modules on the top layer; therefore, the method can improve the readability of codes, is easy to divide modules, and is convenient to simulate during designing.

Owner:NANJING UNIV OF SCI & TECH