Time sequence optimization circuit and method, chip and electronic equipment

An optimization method and timing technology, applied in electrical digital data processing, computer-aided design, instruments, etc., can solve problems such as timing problems not being optimized by tools, unsatisfactory timing optimization effects, and chip performance affecting project progress, etc., to achieve Improve timing optimization effects, shorten design time, and solve timing problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

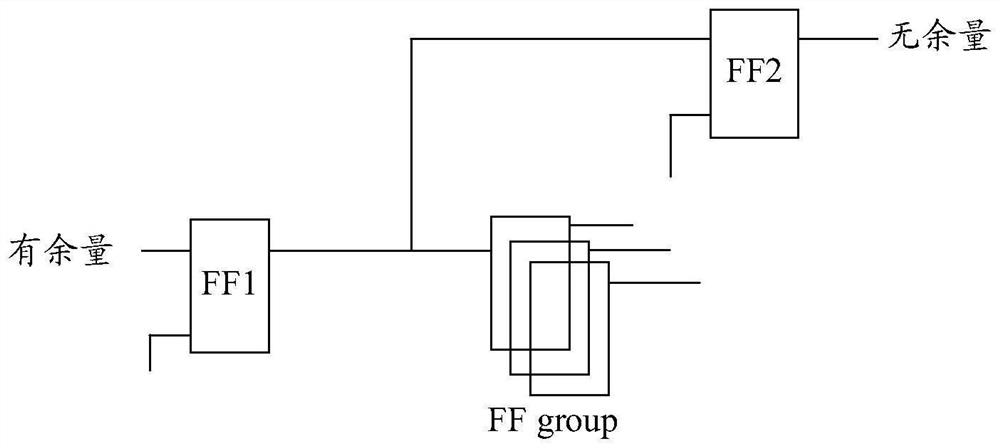

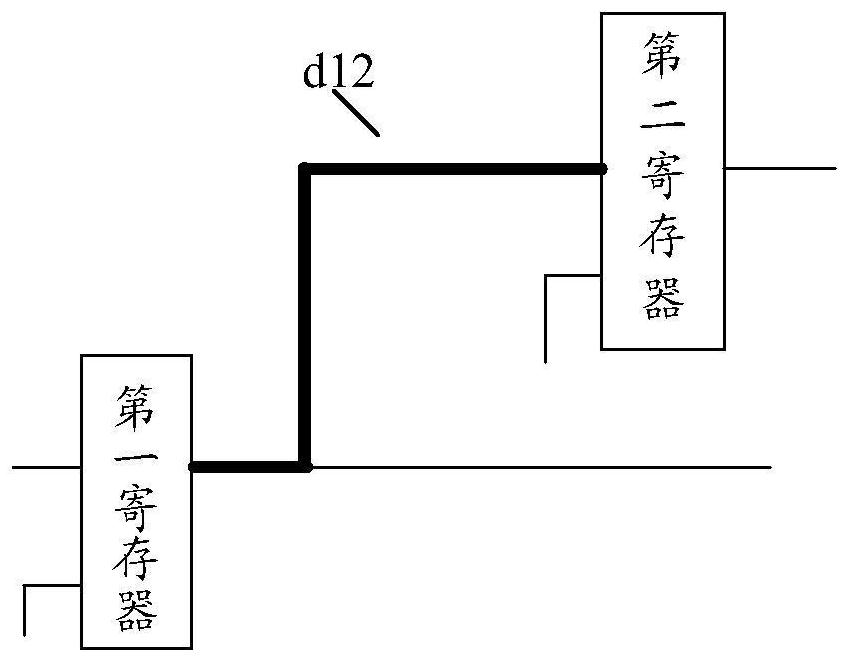

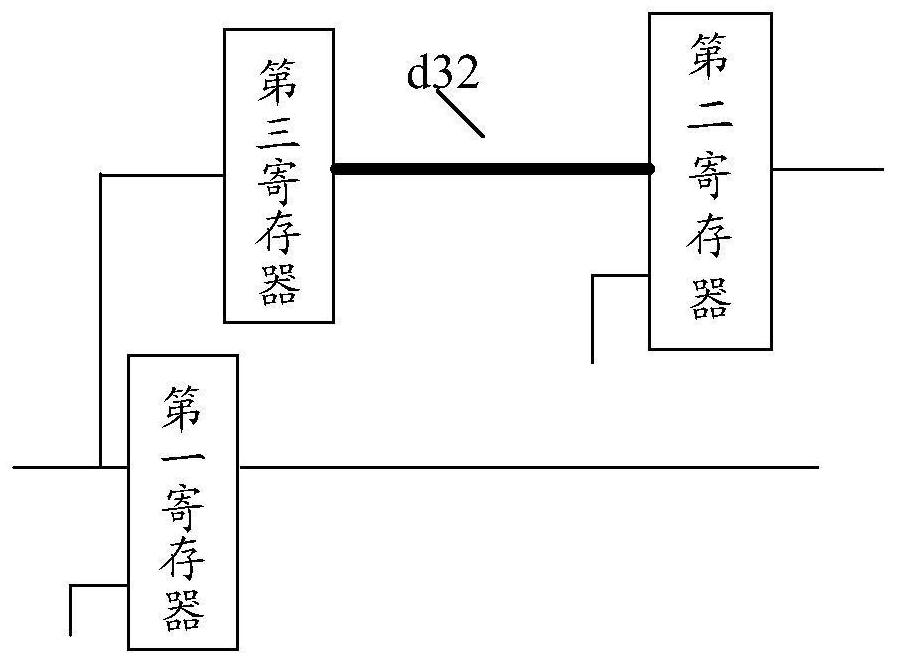

[0030] The technical solutions in the embodiments of the present application will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present application. It should be understood that the specific embodiments described herein are only used to explain the related application, but not to limit the application. In addition, it should be noted that, for the convenience of description, only the parts related to the relevant application are shown in the drawings.

[0031] Before further describing the embodiments of the present invention in detail, the terms and terms involved in the embodiments of the present invention are described. The terms and terms involved in the embodiments of the present invention are applicable to the following explanations.

[0032] Place and route (Place and Route, PnR). Among them, Place is the layout, and Route is the wiring.

[0033] Electronic Design Automation (EDA) refers to the use of C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More