Control method and system for data transmission of data flow architecture neural network chip

A neural network and data transmission technology, applied in the control method and system field of data transmission, to achieve the effect of improving resource utilization efficiency, saving resources, and improving chip performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

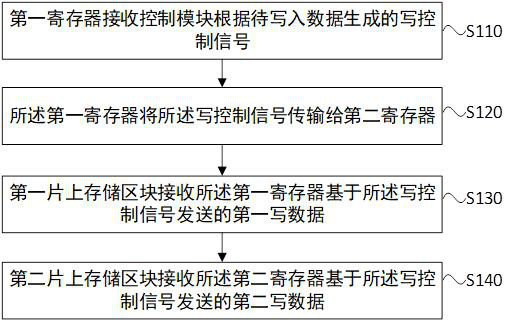

[0056] figure 1 A schematic flowchart of a method for controlling data transmission of a data flow architecture neural network chip provided by an embodiment of the present invention is applicable to the scenario of transmitting data in a neural network chip based on a data flow architecture design. The method can be implemented by The data flow architecture is implemented by the control system of the data transmission of the neural network chip. In this embodiment, the neural network chip designed based on the data flow architecture is referred to as the data flow architecture neural network chip for short.

[0057] Such as figure 1 As shown, the data transmission control method of the data flow architecture neural network chip provided by the embodiment of the present invention includes:

[0058] S110. The first register receives the write control signal generated by the control module according to the data to be written.

[0059] Wherein, the first register refers to a r...

Embodiment 2

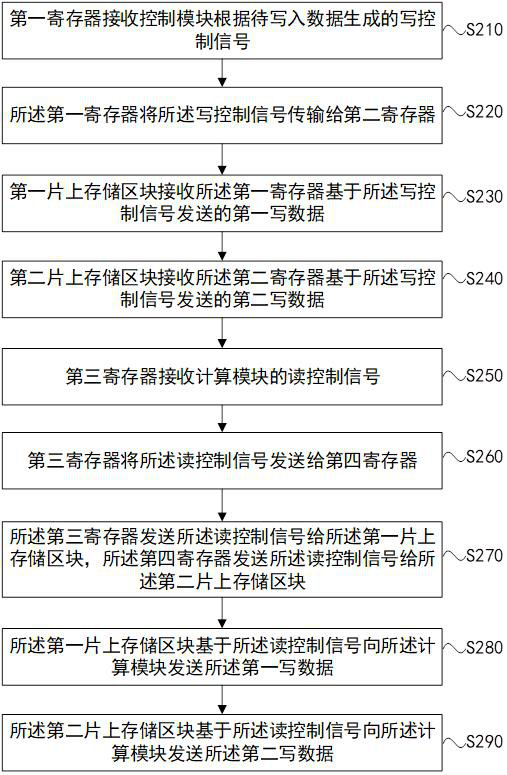

[0074] figure 2 It is a schematic flowchart of a method for controlling data transmission of a data flow architecture neural network chip provided by an embodiment of the present invention. This embodiment is an optional embodiment based on the above technical solution, and is applicable to the scenario of transmitting data in a neural network chip designed based on a data flow architecture. The method can be executed by the data transmission control system of the neural network chip with the data flow architecture. In this embodiment, the neural network chip designed based on the data flow architecture is referred to as the data flow architecture neural network chip for short.

[0075] Such as figure 2 As shown, the data transmission control method of the data flow architecture neural network chip provided by the embodiment of the present invention includes:

[0076] S210. The first register receives the write control signal generated by the control module according to t...

Embodiment 3

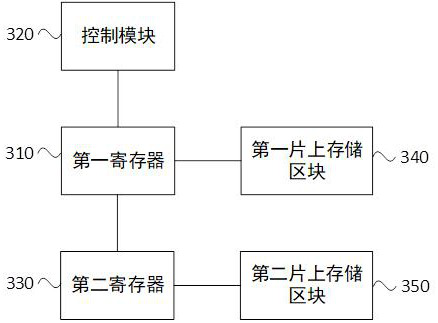

[0107] image 3 It is a schematic structural diagram of a control system for data transmission of a neural network chip with a data stream architecture provided by an embodiment of the present invention. This embodiment is applicable to the scenario of transmitting data in a neural network chip based on a data stream architecture design.

[0108] Such as image 3 As shown, the data transmission control system of the data flow architecture neural network chip provided in this embodiment may include a first register 310, a control module 320, a second register 330, a first on-chip storage block 340 and a second on-chip storage area Block 350, where:

[0109] The first register 310 is electrically connected to the control module 320, and the first register 310 is configured to receive a write control signal generated by the control module 320 according to the data to be written;

[0110] The first register 310 is electrically connected to the second register 330, and the first ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More