Memory chip packaging structure and preparation method thereof

A memory chip and packaging structure technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as increased process risk, increased number of stacked layers, and inclination, so as to improve integration and functionality, Excellent electrical conductivity and cost reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

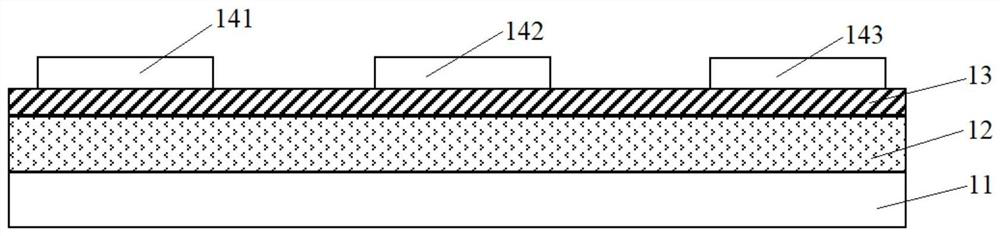

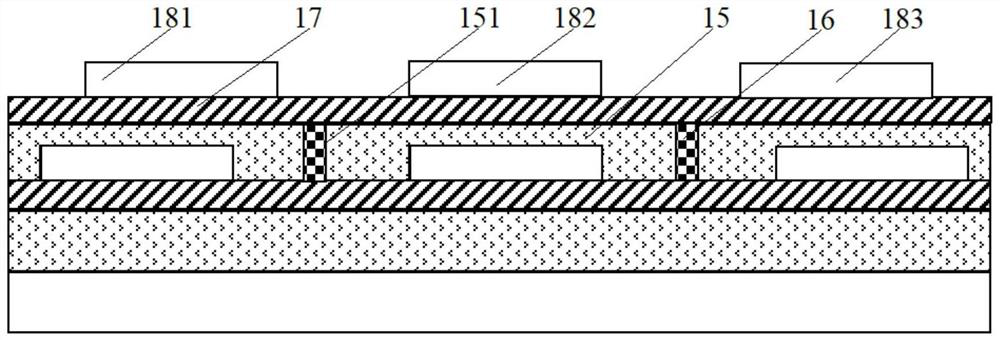

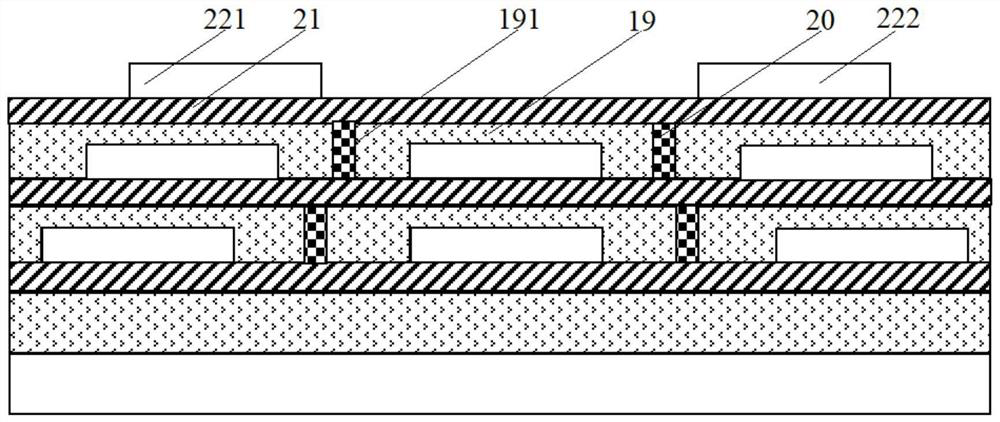

[0019] It is to be appreciated that the following disclosure provides many different embodiments, or examples, for implementing different components of the presented subject matter. Specific examples of each component and its arrangement are described below in order to simplify the description of the disclosure. Of course, these are examples only and are not intended to limit the present disclosure. For example, the following disclosure describes that a first component is formed on or over a second component, which means that it includes the embodiment in which the first component is formed in direct contact with the second component, and also includes In addition, an additional component may be formed between the first component and the second component, so that the first component may not be in direct contact with the second component. In addition, different examples in the disclosure may use repeated reference signs and / or words. These repetitions or words are used for si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More