Wafer test classification method and system

A technology of wafer testing and classification methods, applied in semiconductor/solid-state device testing/measurement, electrical components, semiconductor/solid-state device manufacturing, etc., can solve the problem of uncontrollable FT yield rate in mass production of high-performance product specifications and inability to effectively process performance Requires production and testing process chip products, high production and testing costs, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0112] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0113] It should be clear that the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

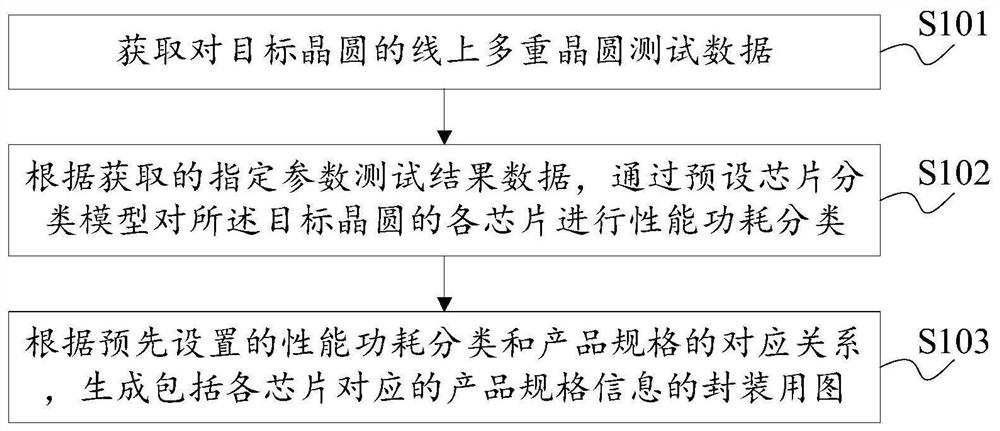

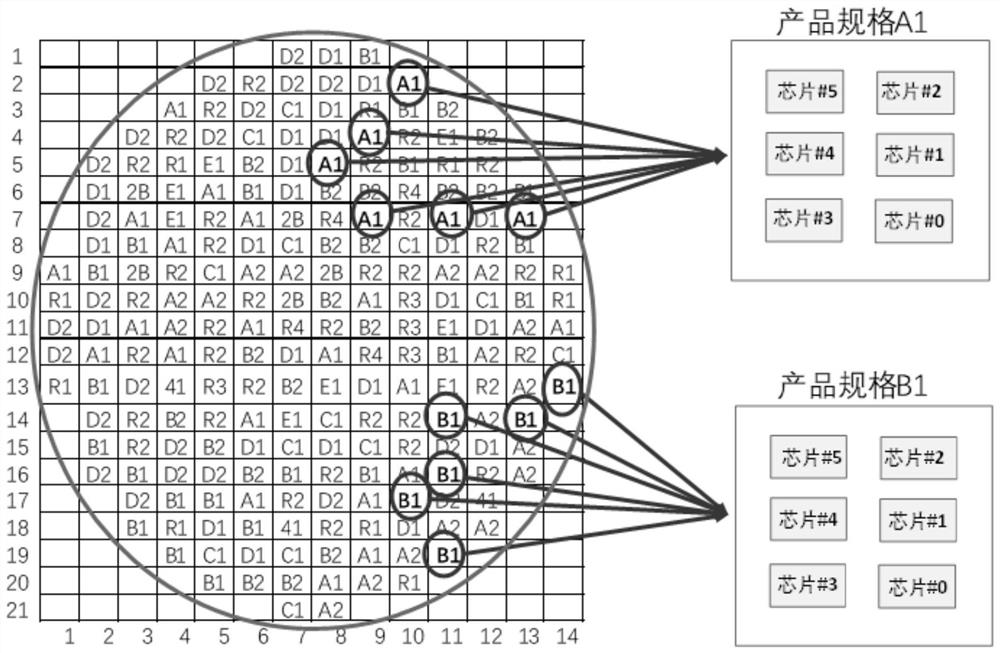

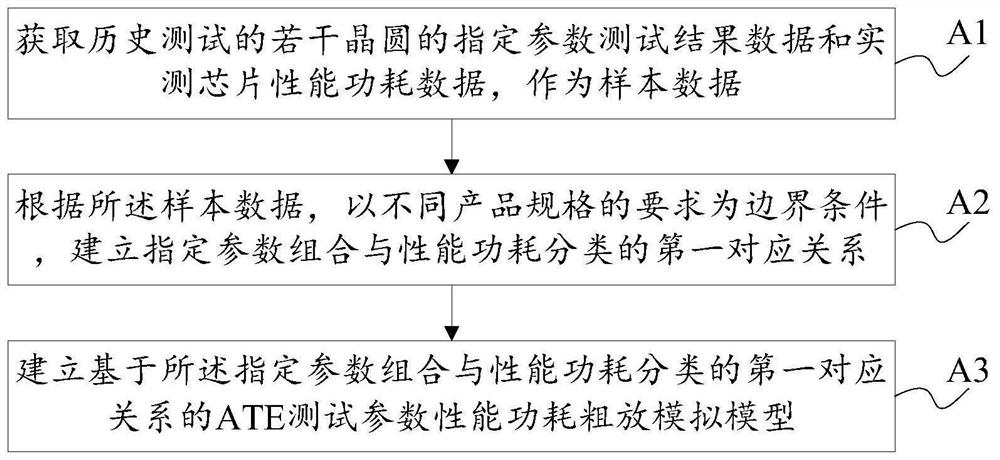

[0114] figure 1 It is a schematic flowchart of Embodiment 1 of a wafer test classification method provided by an embodiment of the present invention. see figure 1 , the method includes the following steps before the encapsulation step:

[0115] Step S101, obtaining online multi-wafer test data for the target wafer;

[0116] Wherein, the test data includes the specified parameter test result data of the target wafer under different temperature and voltage test conditions;

[0117] In this embodiment, the test and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More