Simulation verification method and system based on combination of virtual platform and FPGA

A virtual platform and simulation verification technology, which is applied in the field of simulation verification, can solve the problems of slow simulation speed and RTL simulation speed that cannot meet the project cycle requirements, and achieve the effect of facilitating optimization and modification, reducing economic costs and verification costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

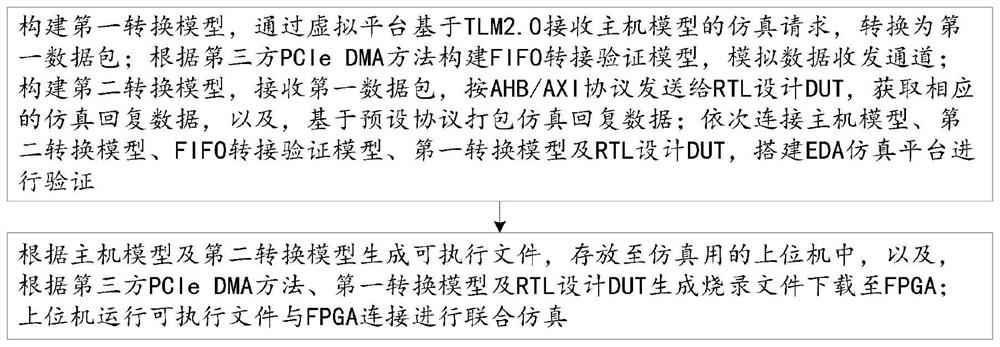

Method used

Image

Examples

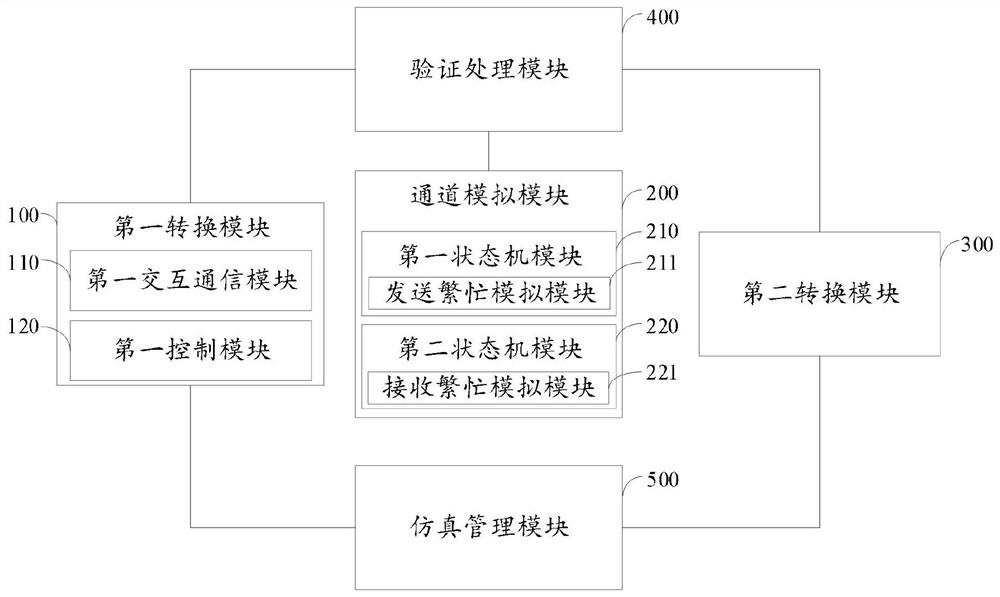

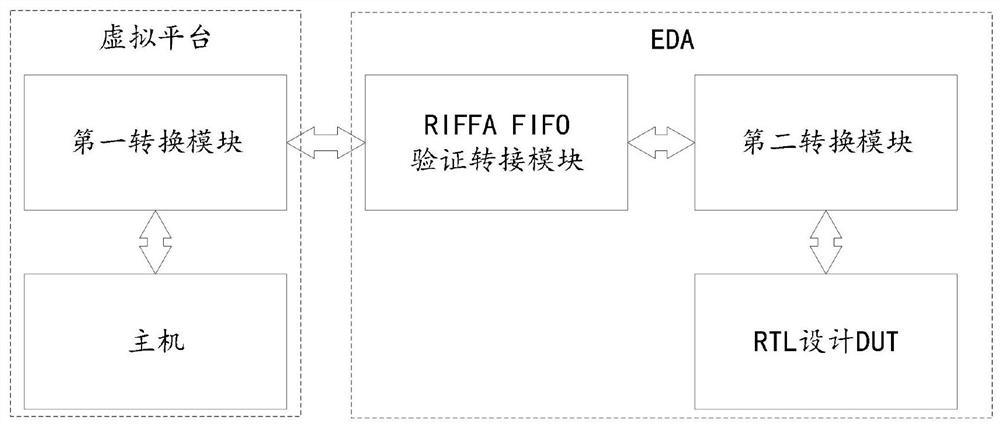

Embodiment Construction

[0029] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

[0030] In the description of the present invention, the meaning of several means one or more, and the meaning of multiple means two or more than two. Greater than, less than, exceeding, etc. are understood as not including the original number, and above, below, within, etc. are understood as including the original number . If the description of the first and second is only for the purpose of distinguishing the technical features, it cannot be understood as indicating or implying the relative importance or implicitly indicating the number o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More