Chip design method based on RISC-V, navigation chip and receiver

A RISC-V and chip design technology, applied in CAD circuit design, computer-aided design, computing, etc., can solve problems such as insufficient to meet the pursuit of low power consumption, achieve high versatility, reduce chip power consumption, and reliability Good results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

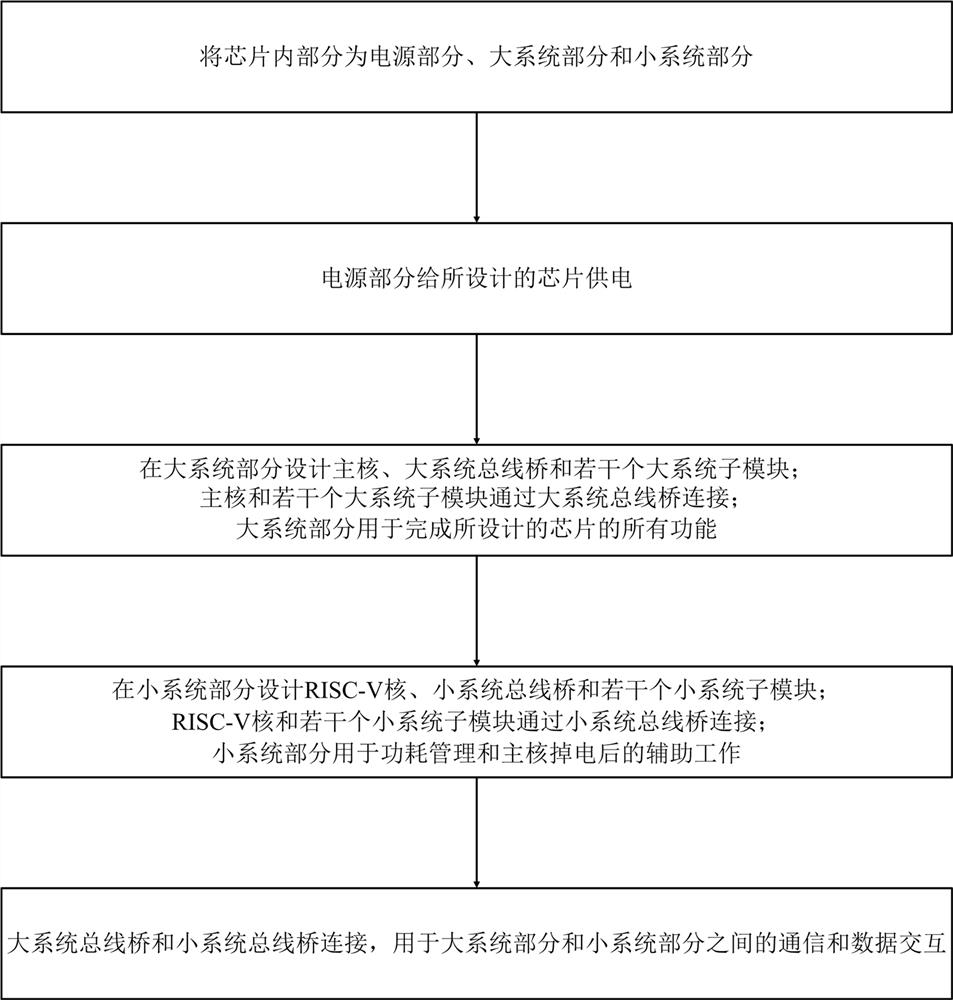

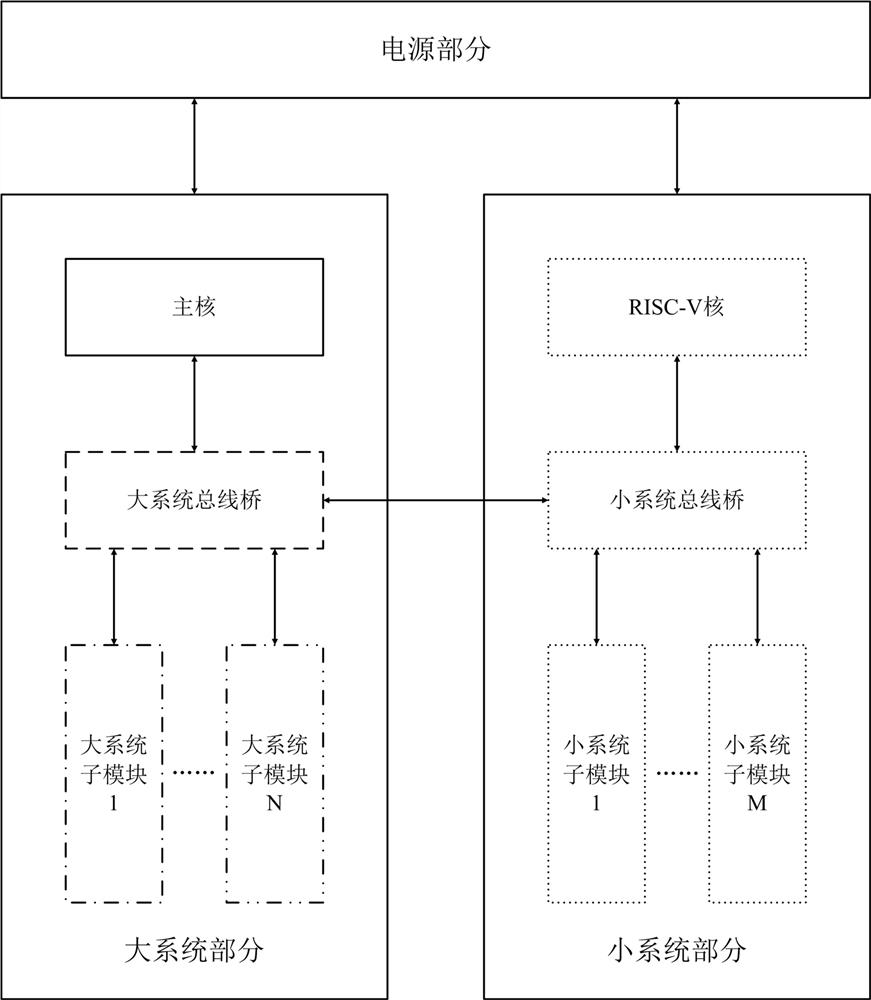

[0028] Such as figure 1 Shown is the method flow diagram of the method of the present invention, as figure 2 Shown is a schematic diagram of the internal architecture of the chip designed by the method of the present invention: the RISC-V-based chip design method provided by the present invention includes the following steps:

[0029] S1. Divide the inside of the chip into a power supply part, a large system part and a small system part;

[0030] S2. The power supply part supplies power to the designed chip;

[0031] S3. Design the main core, large system bus bridge and several large system submodules in the large system part; the main core and several large system submodules are connected through the large system bus bridge; the large system part is used to complete all of the designed chip Function;

[0032] The main core can adopt mainstream high-performance CPU, which is responsible for the main functions of the chip;

[0033] S4. Design RISC-V core, small system bus ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com