Equalizer for high-speed interface circuit and its control method

A high-speed interface, equalizer technology, applied in the direction of shaping network, electrical components, digital transmission system in transmitter/receiver, etc., can solve the channel bit error rate increase, data edge jitter, can not meet high-speed data transmission, etc. problem, to achieve the effect of reducing data jitter, reducing design difficulty, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

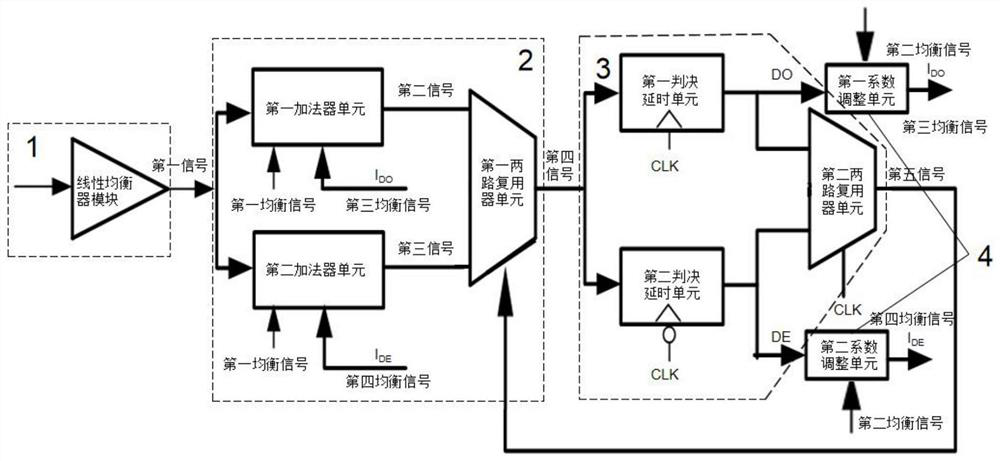

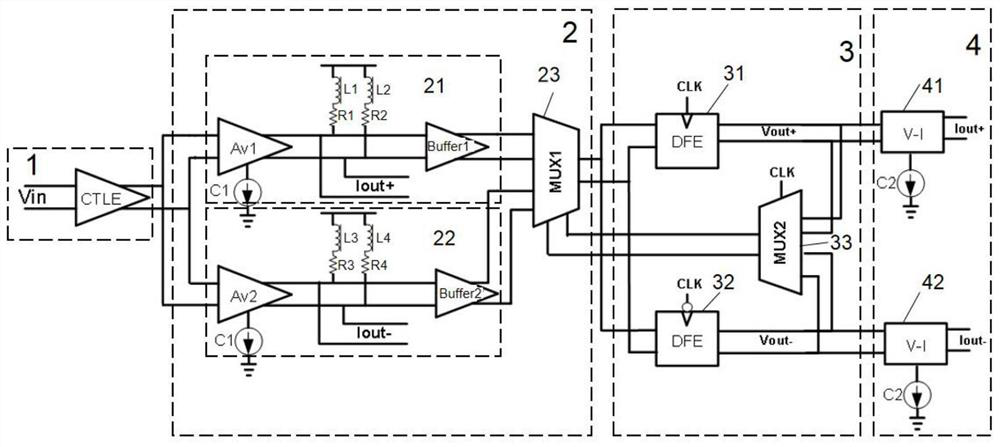

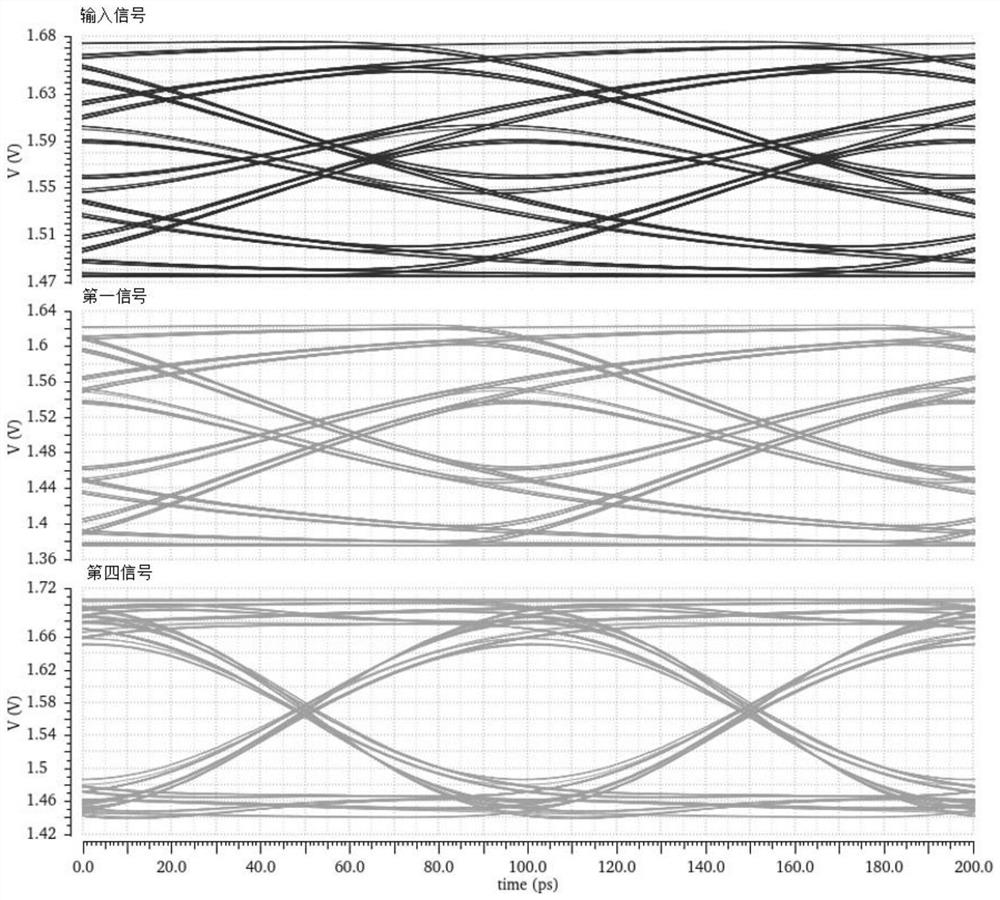

[0030] Embodiment 1 of the present invention provides an equalizer for a high-speed interface circuit, such as Figure 1-3 As shown, it includes a linear equalizer module 1 for receiving and primary balancing input signals, an adder compensation module 2, a decision delay module 3 and a coefficient adjustment module 4, and the linear equalizer module 1 is sequentially connected to the adder compensation module 2 , a decision delay module 3 and a coefficient adjustment module 4, the adder compensation module 2 combines the input signal after the primary balance of the linear equalizer module 1 with the multi-channel equalized signal for addition processing and then selects the output through the channel, and the decision delay The module 3 selects and outputs the signal of the adder compensation module 2 channel according to the control signal, and then outputs it to the adder compensation module 2 through the channel selection. The coefficient weighting adjustment is output to...

Embodiment 2

[0048] Embodiment 2 of the present invention provides a method for controlling an equalizer applying the high-speed interface circuit, including the following steps:

[0049] S1. The linear equalizer module receives and primary balances the input signal;

[0050] S2, the adder compensation module performs addition processing on the primary balanced input signal in S1 combined with the multi-channel equalized signal, and then selects the output through the channel;

[0051] S3, the decision delay module performs the decision delay of the signal output by the channel selection in the S2 according to the control signal CLK, and then outputs the signal to the adder compensation module through the channel selection;

[0052] S4. The coefficient adjustment module performs coefficient weighting adjustment on the decision-delayed signal in S3 and outputs it to the adder compensation module.

[0053] In the control method of the equalizer of the high-speed interface circuit of the pre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More