GaN HEMT and Si-CMOS monolithic integration method

A monolithic integration and epitaxial layer technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of large loss, high cost, and large volume, and achieve low cost, superior performance, and small chip area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further described below with reference to the accompanying drawings and embodiments.

[0017] It should be noted that all directional indications (such as up, down, left, right, front, back, inside, outside, top, bottom...) in the embodiments of the present invention are only used to explain As shown in the figure), if the relative positional relationship between the various components, etc., if the specific posture changes, the directional indication will also change accordingly.

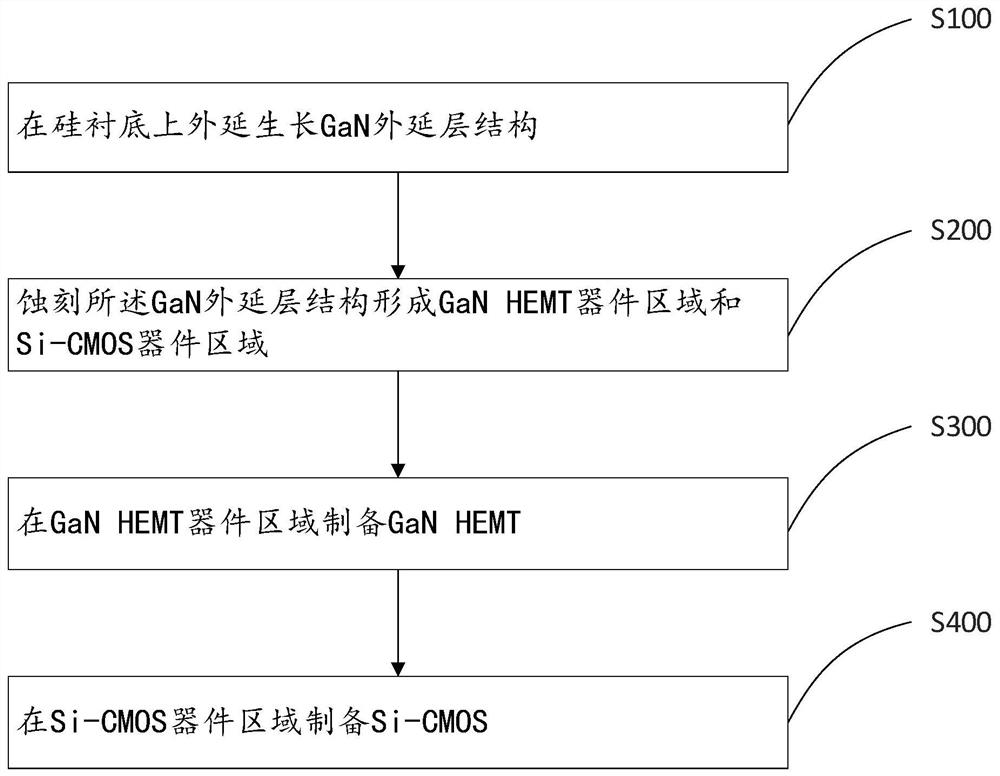

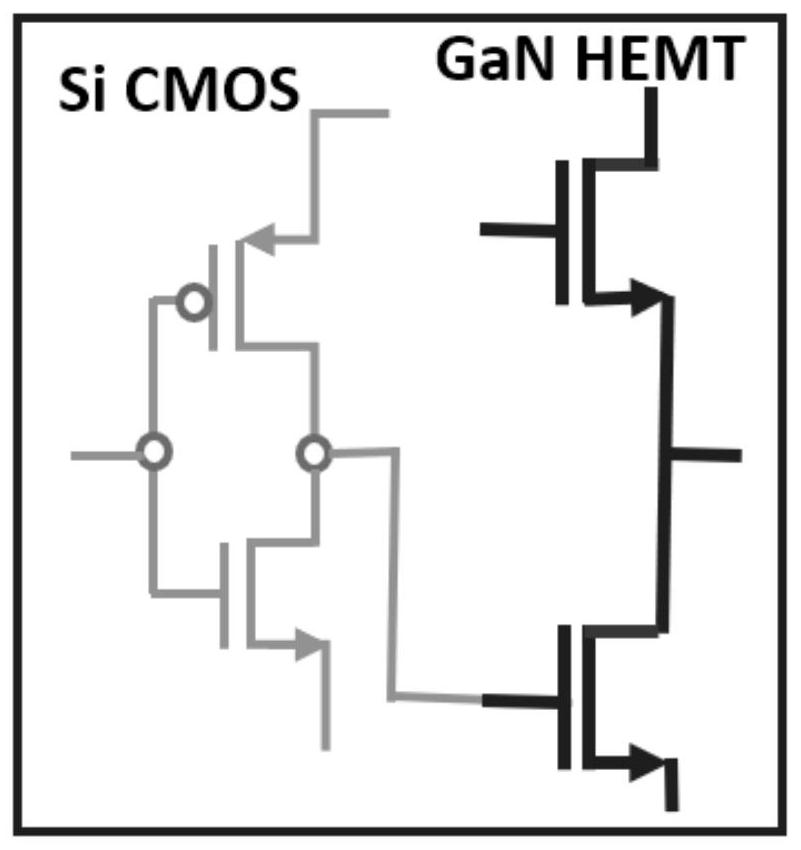

[0018] like figure 1 As shown, the embodiment of the present invention provides a GaN HEMT and Si-CMOS monolithic integration method, comprising the following steps:

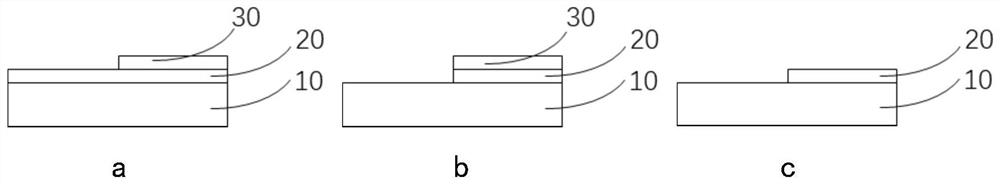

[0019] Step S100, epitaxially growing a GaN epitaxial layer structure on a silicon substrate;

[0020] Step S200, etching the GaN epitaxial layer structure to form a GaN HEMT device region and a Si-CMOS device region;

[0021] Step S300, preparing a GaN HEMT in the GaN HEMT device region;

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com