Defect detection wafer graph optimization method and optimization system thereof

A defect detection and optimization method technology, applied in semiconductor/solid-state device testing/measurement, electrical components, semiconductor/solid-state device manufacturing, etc., can solve problems such as flooding, low value, large quantity, etc., to save time and release machines The effect of increasing production capacity and reducing manpower consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

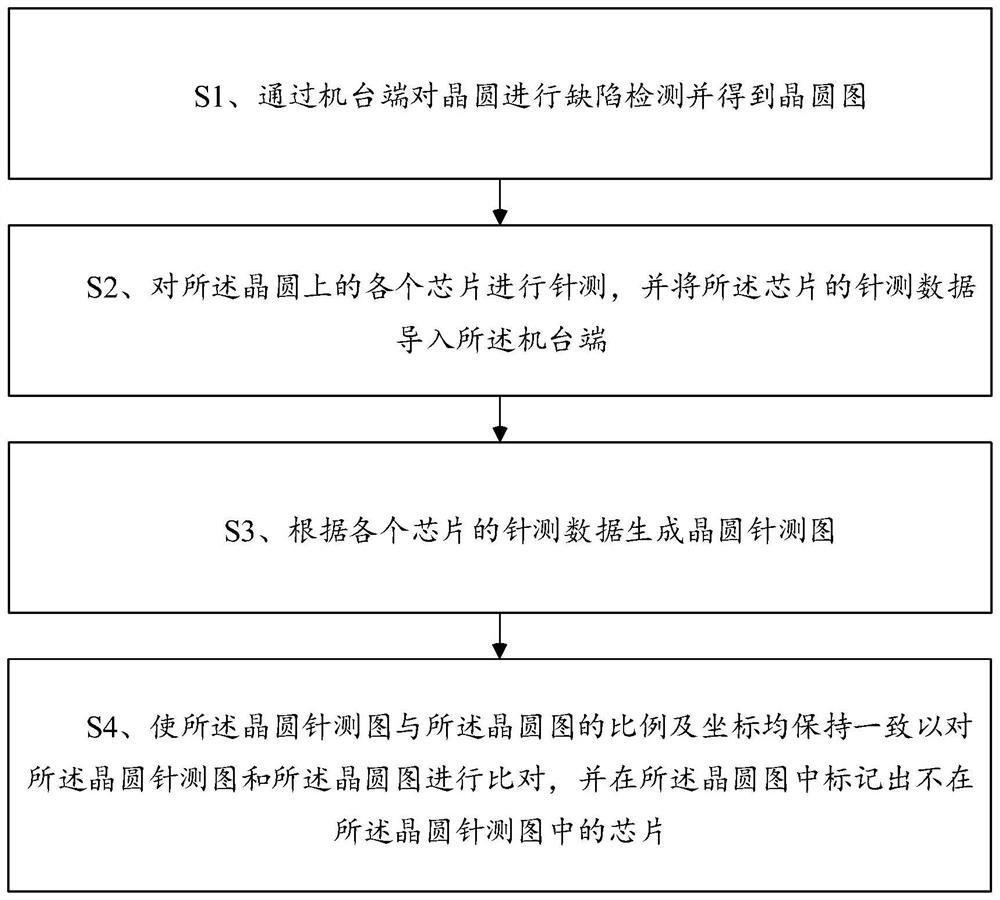

[0034] As mentioned in the background technology, since there are many defects on invalid chips that do not need pin testing, and it is easy to affect the defect detection of valid chips, in order to avoid the influence of such defects, at present, mainly by referring to the scan map (wafer map) in the ACE software ) is compared with the CP map (wafer probe map), and the chip (invalid chip) that does not measure the CP is marked (marked) by manual operation on the software interface and removed. This method has a great influence of human factors, and there will be false marks. The phenomenon.

[0035] Based on this, the present invention provides a defect detection wafer map optimization method and its optimization system, which can automatically mark invalid chips directly on the defect detection machine side, optimize the wafer map, and avoid the influence of abnormal defects.

[0036] In order to make the purpose, advantages and features of the present invention clearer, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More