Fractional phase-locked loop

A phase-locked loop, fractional technology, applied in the field of signal processing, can solve problems such as high spurs, and achieve the effects of eliminating spurs, eliminating quantization noise, and avoiding gain mismatch.

Pending Publication Date: 2021-06-11

BEIJING JINMAIJIE TECHNOLOGY CO. LTD.

View PDF0 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

This mismatch introduces higher spurious

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment 2

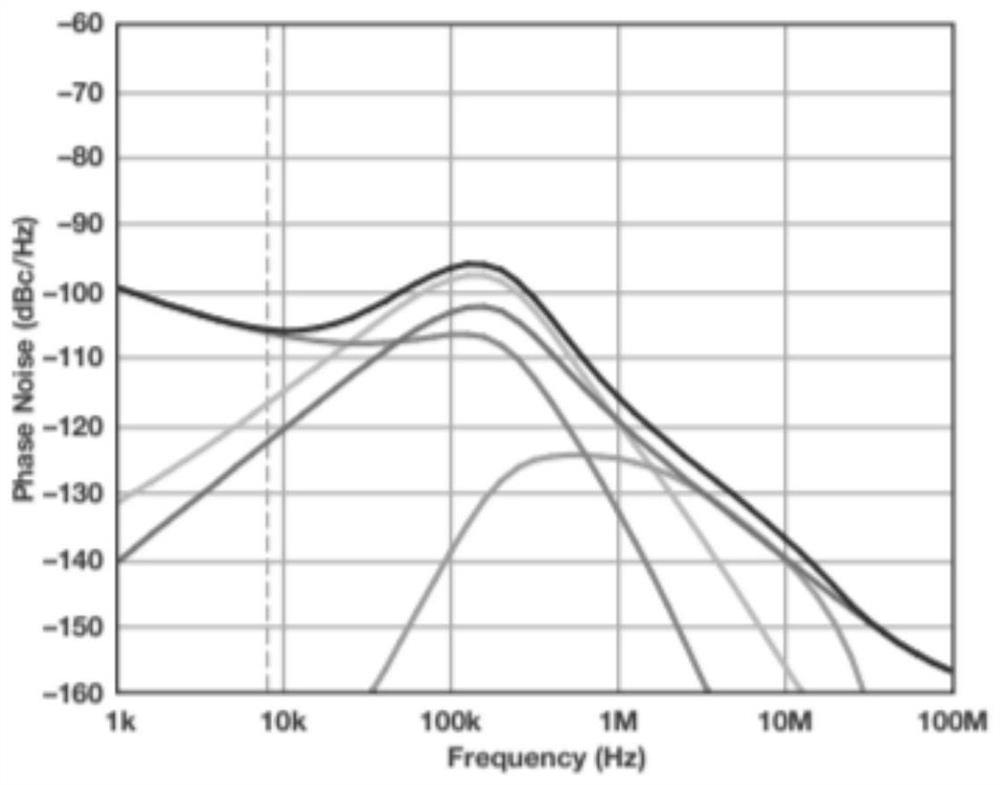

[0028] Embodiment 2: On the basis of Embodiment 1, the small signal model of the phase-locked loop of this design is as follows Figure 7 As shown, in this design K DAC and K CP Naturally equal, thus avoiding the fractional spurs caused by the mismatch.

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

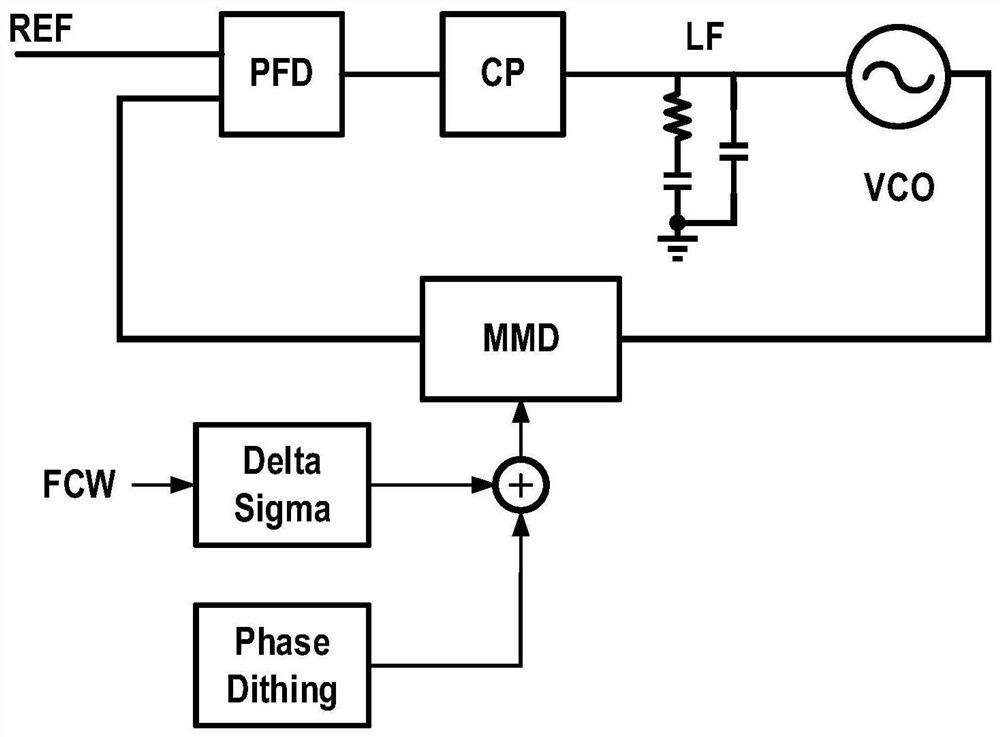

The invention discloses a fractional phase-locked loop which comprises a frequency / phase discriminator PFD, a charge pump CP, a Delta-Sigma modulator, a voltage-controlled oscillator VCO and a multi-mode frequency divider MMD.The input end of the frequency / phase discriminator PFD is connected with the multi-mode frequency divider MMD and a signal FCW, the output end of the frequency / phase discriminator PFD is connected with the charge pump CP, the charge pump CP is further connected with an integrator A and the voltage-controlled oscillator VCO, and the input end of the Delta-Sigma modulator is connected with a signal FCW. An independent digital-analog converter is not used any more, the digital-analog converter is combined with the charge pump, and the extracted quantization noise is directly input into the charge pump. As such, in the small signal model, the gain of the digital-to-analog converter will be normalized into the gain of the charge pump. Therefore, the gain mismatch of the digital-analog converter and the charge pump is avoided, and the aim of eliminating stray and quantization noise at the same time is fulfilled.

Description

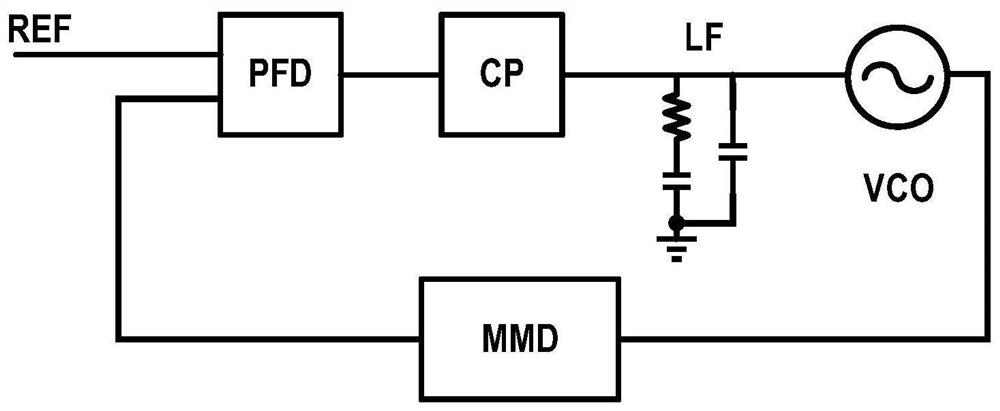

technical field [0001] The invention relates to the technical field of signal processing, in particular to a fractional phase-locked loop. Background technique [0002] Common phase-locked loop structures are divided into integer phase-locked loops and fractional phase-locked loops. The significance of the fractional phase-locked loop is that its frequency is not an integer multiple of the reference clock frequency. Compared with the integer PLL, its design is more difficult. In modern wireless communication systems, fractional phase-locked loops are more commonly used, and their general structure is as follows figure 1 As shown, its main modules are composed of frequency / phase detector (PFD), charge pump (CP), loop filter (LP), voltage-controlled oscillator (VCO) and multi-mode frequency divider (MMD). The output frequency of the voltage-controlled oscillator is controlled by the control voltage, and its output is compared with the reference clock (REF) after passing thr...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More IPC IPC(8): H03L7/08H03L7/18

CPCH03L7/08H03L7/18

Inventor 张昌金沈羿禹沈杰

Owner BEIJING JINMAIJIE TECHNOLOGY CO. LTD.