Multilayer hybrid semiconductor package

A multi-layer hybrid, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of reduced practicability and diversification of semiconductors, cumbersome, and user troublesome, so as to avoid the tilt of the body. Derailment, improving solid structure, increasing diversity and effectiveness of diversification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

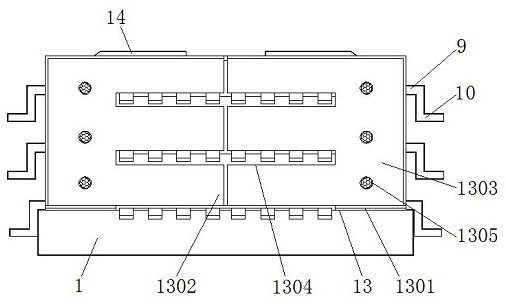

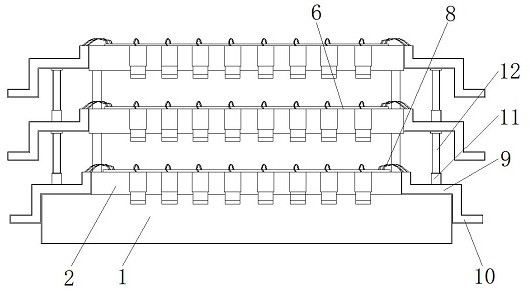

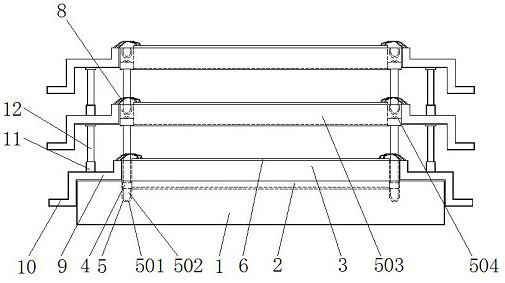

[0027] see Figure 1-5 , the present invention provides a technical solution: a multilayer hybrid semiconductor package, including a base 1, an embedding groove 2, a chip holder 3, a fixing ring 4, an erection mechanism 5, a first embedding groove 501, a double-headed embedding rod 502, Additional layer 503, hollow groove 504, second embedding groove 505, semiconductor chip 6, connecting wire plate 7, connecting wire 8, lead frame 9, pin 10, solder sleeve 11, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More