Verification method, device and equipment for algorithm module in chip and readable storage medium

A technology of algorithm module and verification method, which is applied in the directions of calculation, instrumentation, error detection/correction, etc., can solve the problems of inability to quickly and effectively locate the error position and inconvenient use, so as to ensure timing consistency, reduce workload, and improve verification efficiency effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

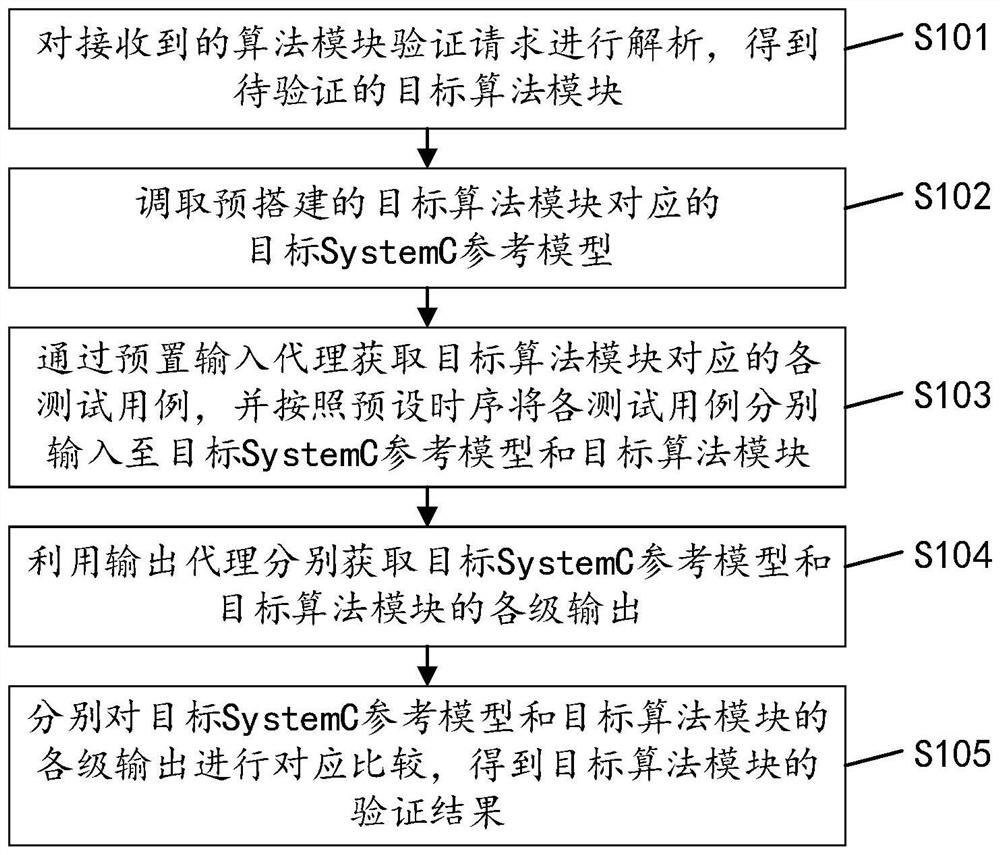

[0073] see figure 1 , figure 1 It is an implementation flowchart of a method for verifying an algorithm module in a chip in an embodiment of the present invention, and the method may include the following steps:

[0074] S101: Analyzing the received algorithm module verification request to obtain a target algorithm module to be verified.

[0075] When the algorithm module in the chip needs to be verified, an algorithm module verification request is sent to the pre-built chip algorithm module verification platform. The algorithm module verification request can include the target algorithm module to be verified, the chip information to which the target algorithm module belongs, etc. The chip algorithm module verification platform receives the algorithm module verification request, and analyzes the received algorithm module verification request to obtain the target algorithm module to be verified.

[0076] S102: Call the target SystemC reference model corresponding to the pre-b...

Embodiment 2

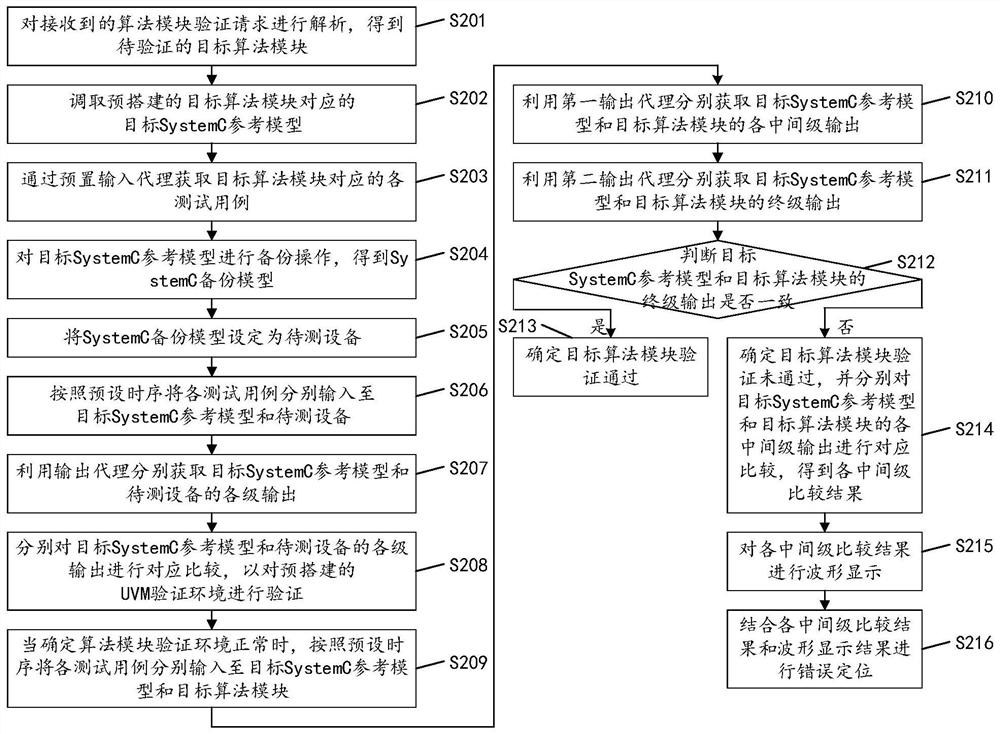

[0089] see figure 2 , figure 2 It is another implementation flowchart of the verification method of the algorithm module in the chip in the embodiment of the present invention, and the method may include the following steps:

[0090] S201: Analyzing the received algorithm module verification request to obtain a target algorithm module to be verified.

[0091] S202: Call the target SystemC reference model corresponding to the pre-built target algorithm module.

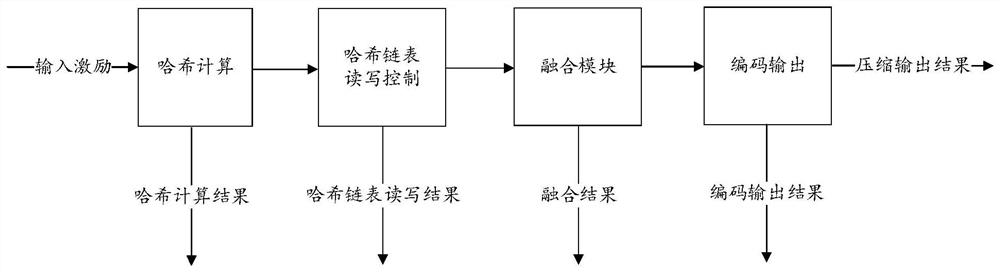

[0092] see image 3 It is a structural block diagram of a SystemC reference model corresponding to a compression algorithm module in an embodiment of the present invention. When the target algorithm module is a compression algorithm module, the compression algorithm module searches for repeated parts in the input original text and replaces these repeated parts with a specific code, thereby replacing a long original text with a shorter code , so as to realize the compression of the input. The SystemC reference mod...

Embodiment 3

[0169] Corresponding to the above method embodiment, the present invention also provides a verification device for the algorithm module in the chip, the verification device for the algorithm module in the chip described below and the verification device method for the algorithm module in the chip described above can refer to each other .

[0170] see Figure 6 , Figure 6 It is a structural block diagram of a verification device for an algorithm module in a chip in an embodiment of the present invention, and the device may include:

[0171] The request parsing unit 61 is configured to parse the received algorithm module verification request to obtain the target algorithm module to be verified;

[0172] Model calling unit 62, used to call the target SystemC reference model corresponding to the pre-built target algorithm module;

[0173] The use case input unit 63 is used to obtain each test case corresponding to the target algorithm module through a preset input agent, and i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More