Power balancer for series-connected load zones of integrated circuit

A power balance and integrated circuit technology, applied in the direction of circuit devices, DC power supply parallel operation, DC network circuit devices, etc., can solve the problems of limiting the reliability of chip packaging current flow, high power cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

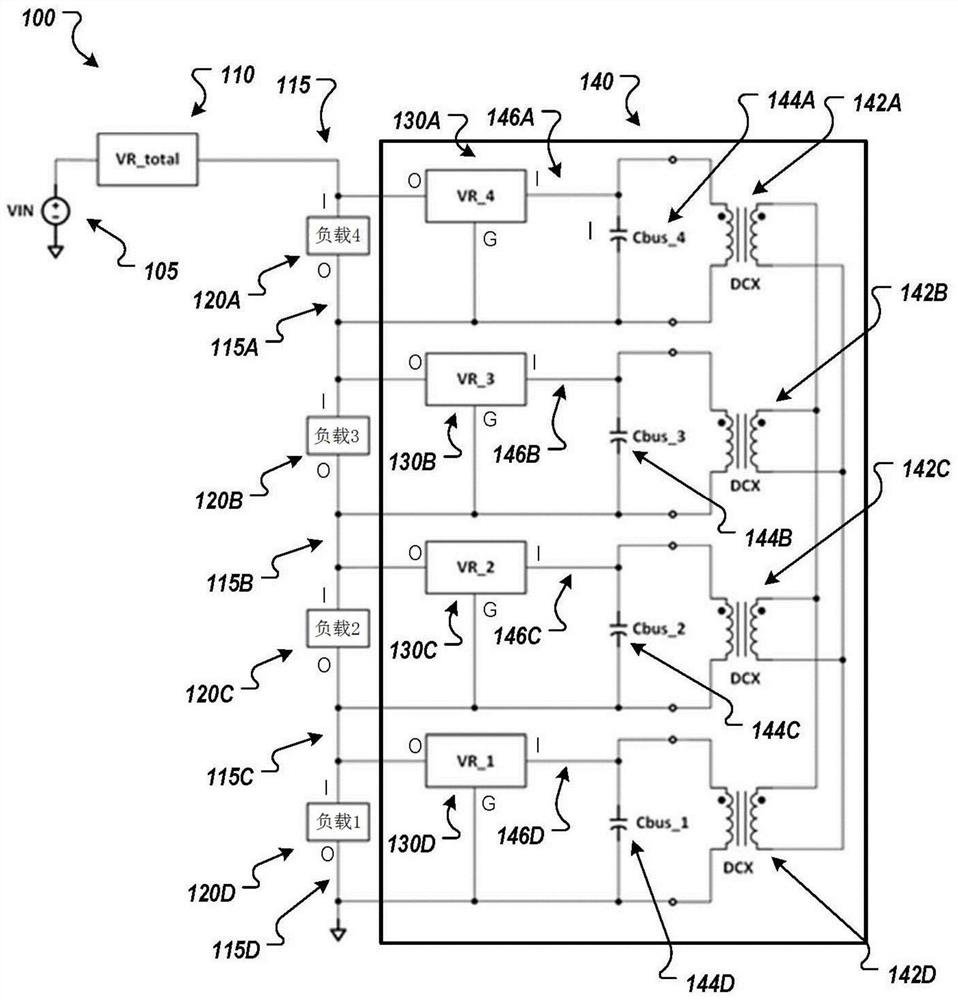

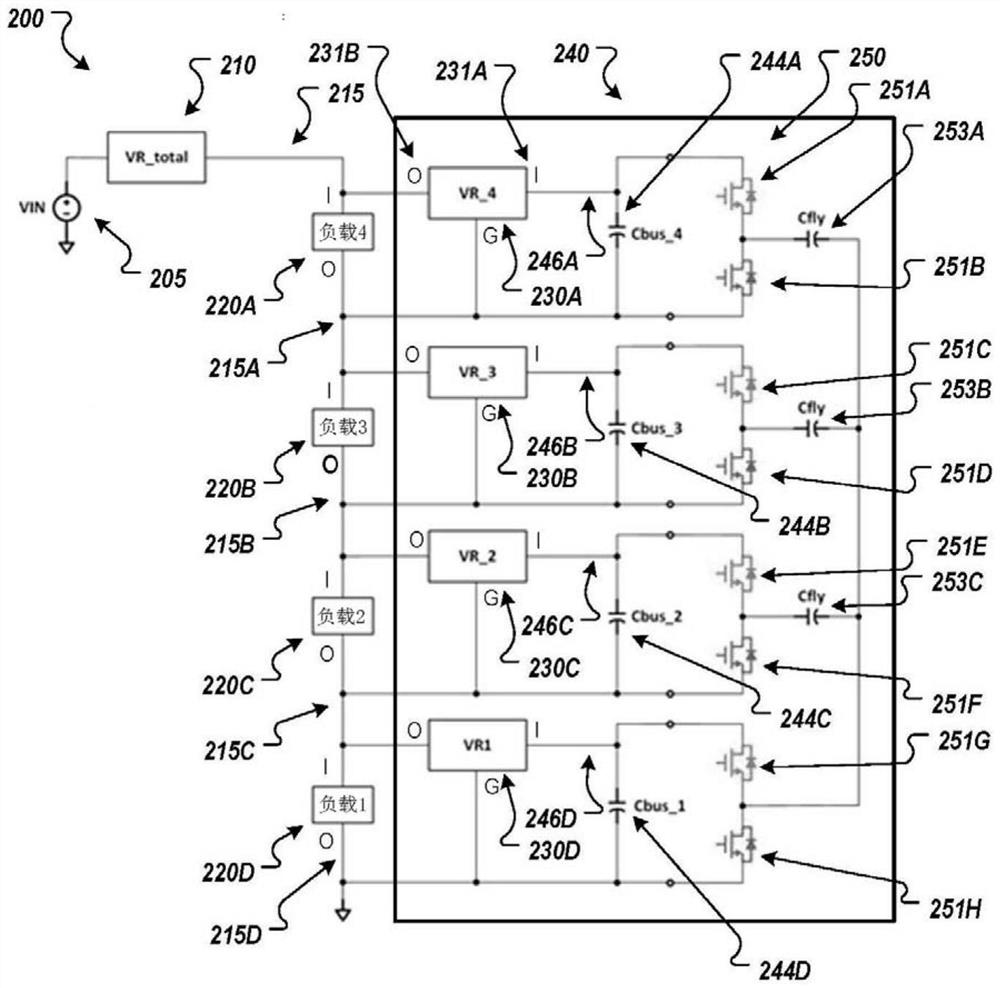

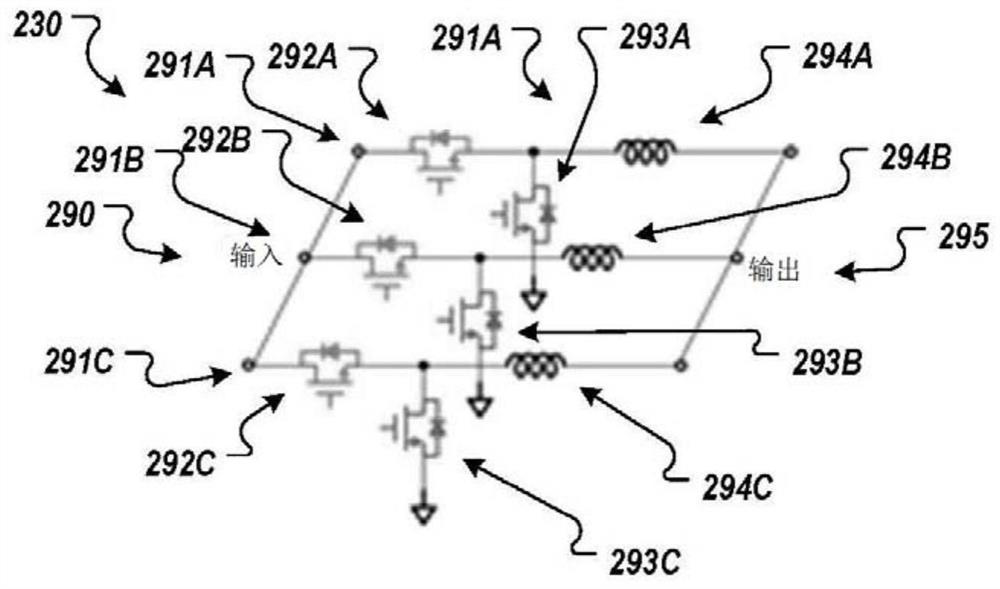

[0025] In general, the systems and techniques described herein relate to power balancer circuits that enable multiple load regions of an IC to be powered in series while maintaining a balanced voltage across each load region. Each load zone is a group of one or more electrical loads fabricated on-chip and powered as a group using a common power source. An example load region is a processor core. For example, the cores of a multicore processor can be powered in series using the power balancer described in this document. Since the core (or other load zones) may require different amounts of current, a power balancer is used to maintain the same voltage level in each load zone. In some implementations, the power balancer includes separate voltage regulators for each load zone. Each individual voltage regulator further regulates the operating voltage in its load zone.

[0026] figure 1 is a diagram of a circuit 100 including a plurality of loads 120A- 120D powered in series and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More