Circuit aging test method based on BIST structure and self-oscillation ring

A aging test and self-oscillation technology, which is applied in the direction of electronic circuit testing, measuring electronics, measuring devices, etc., can solve the problems of inaccurate testing, affecting the timing of critical paths, and large hardware overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

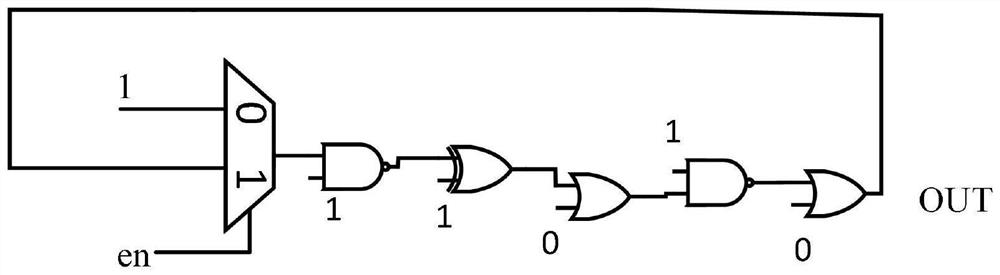

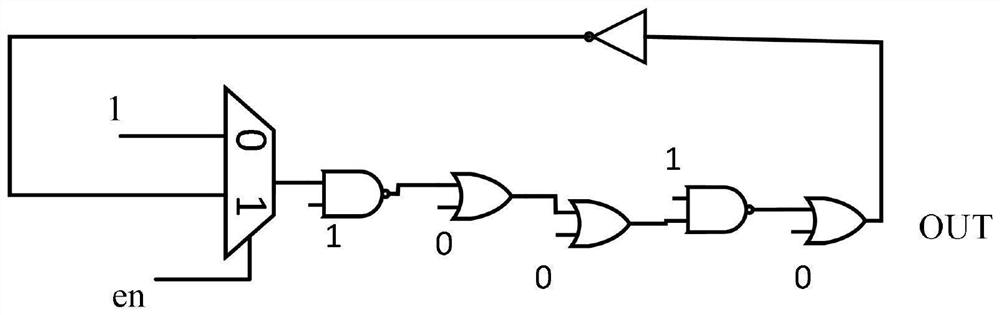

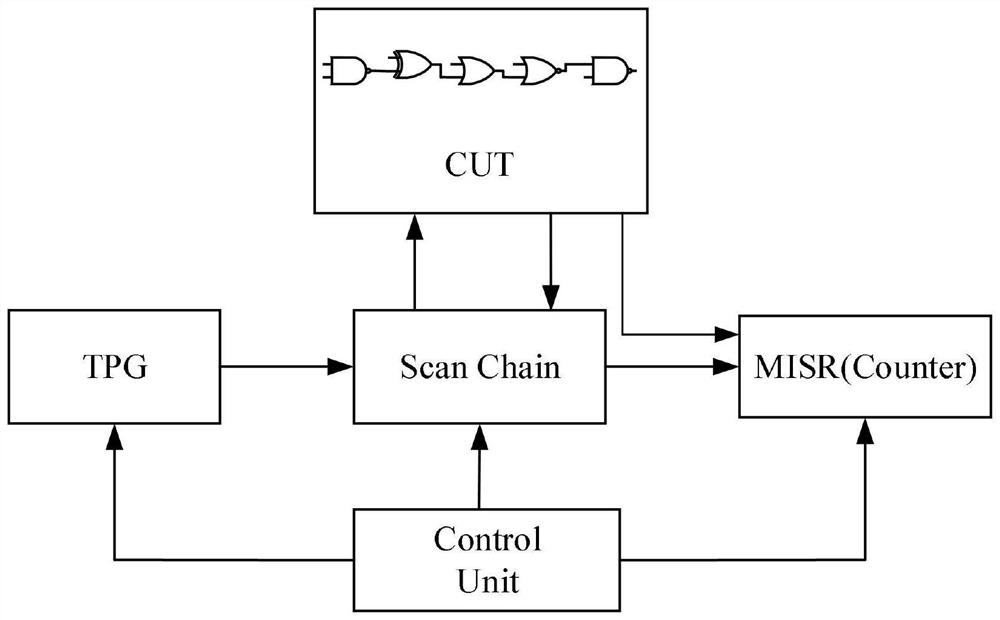

[0056] In this embodiment, a circuit aging test method based on a BIST structure and a self-oscillating ring is performed as follows:

[0057] Step 1. Select a representative critical path from the circuit under test:

[0058] Step 1.1. Use the static timing analysis tool to analyze the timing of the circuit to be tested, and select a path whose timing margin is less than m of the clock period and add it to the initial path set N 0 Among them, m represents the ratio of the timing margin to the clock cycle, ranging from 15% to 20%;

[0059] Step 1.2, use the strong correlation filtering method to filter the initial path set N 0 The paths are screened, and the redundant paths with the same gate unit structure and the same number of gate units or a difference of one are removed, so as to obtain the filtered path set N’ 0 ;

[0060] Step 1.3, use the fan-out filtering method to filter the path set N' 0 Sort the sum of the fan-out numbers of all gates in each path, and take the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More