Multi-finger transistor and power amplifier circuit

A transistor and electrical connection technology, applied in the field of multi-finger transistors and power amplifier circuits, can solve the problems of inability to obtain amplification characteristics, uneven action, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach and comparative example

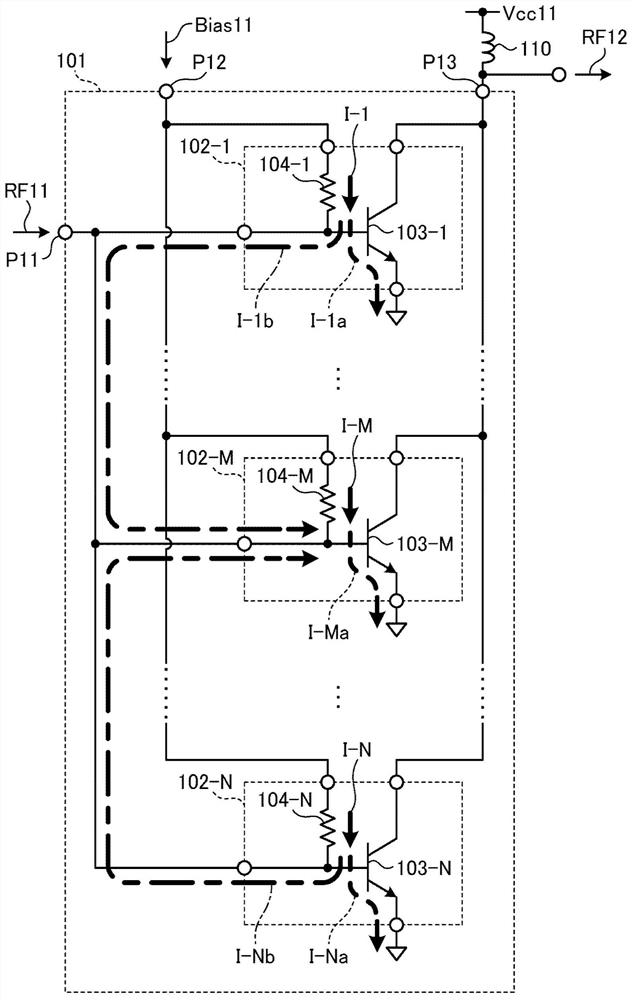

[0027] Hereinafter, the first embodiment will be described, but in order to make the first embodiment easier to understand, a comparative example will be described first.

no. 1 Embodiment approach

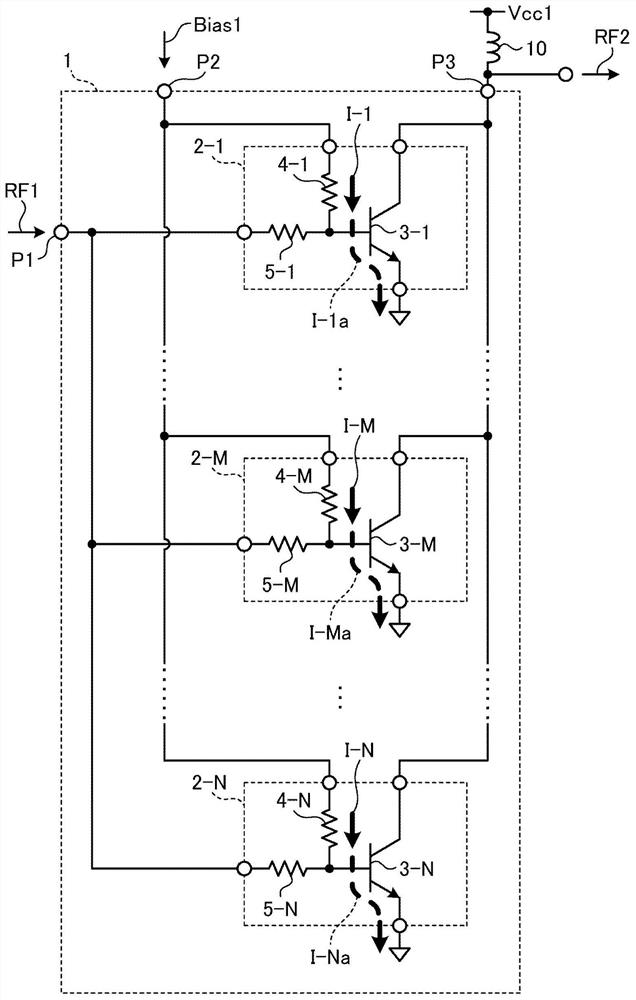

[0044] figure 2 It is a figure showing the structure of the multi-finger transistor of 1st Embodiment. The multi-finger transistor 1 is formed by electrically connecting a plurality of unit transistors in parallel. A unit transistor refers to a minimum structure constituting a transistor.

[0045] The finger transistor 1 has a first terminal P1 to which an AC signal RF1 is input, a second terminal P2 to which a bias current Bias1 is input, and a third terminal P3 to which an AC signal RF2 is output. The third terminal P3 is electrically connected to the power supply potential Vcc1 via the choke inductor 10 .

[0046] The first terminal P1 corresponds to an example of the "common input terminal" in the present disclosure. The second terminal P2 corresponds to an example of the "common bias terminal" in the present disclosure. The third terminal P3 corresponds to an example of the "common output terminal" in the present disclosure.

[0047]The multi-finger transistor 1 is ...

no. 2 Embodiment approach

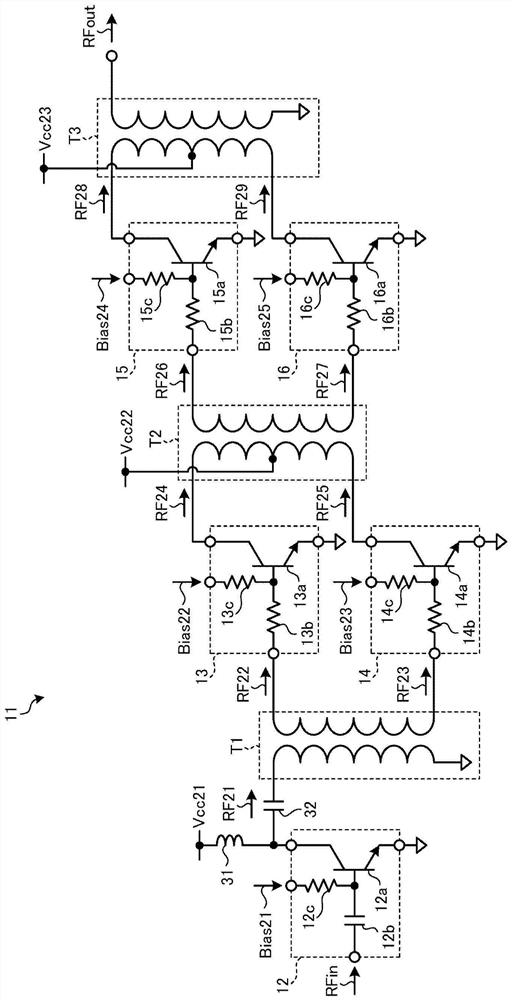

[0063] image 3 It is a figure which shows the structure of the power amplifier circuit of 2nd Embodiment. in detail, image 3 It is a diagram showing the configuration of a power amplifying circuit to which the multi-finger transistor 1 of the first embodiment is applied.

[0064] The power amplifying circuit 11 may be realized by a hybrid IC (also referred to as a module) in which a plurality of components (semiconductor chips, etc.) are mounted on one substrate, but the present disclosure is not limited thereto.

[0065] The power amplifying circuit 11 includes a multi-finger transistor 12 as a first-stage power amplifier, multi-finger transistors 13 and 14 as a second-stage power amplifier, and multi-finger transistors 15 and 16 as a third-stage power amplifier. In addition, the number of stages of the power amplifier is not limited to three, and may be two or less or four or more.

[0066] The multi-finger transistor 12 is a general multi-finger transistor in which a D...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com