FPGA (Field Programmable Gate Array) for improving reliability of key configuration code stream by multiplexing buffer memory

A configuration code and reliability technology, applied in the field of FPGA, can solve problems such as single event flip, circuit function failure, configuration content flip error, etc., to improve operational reliability and ensure accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

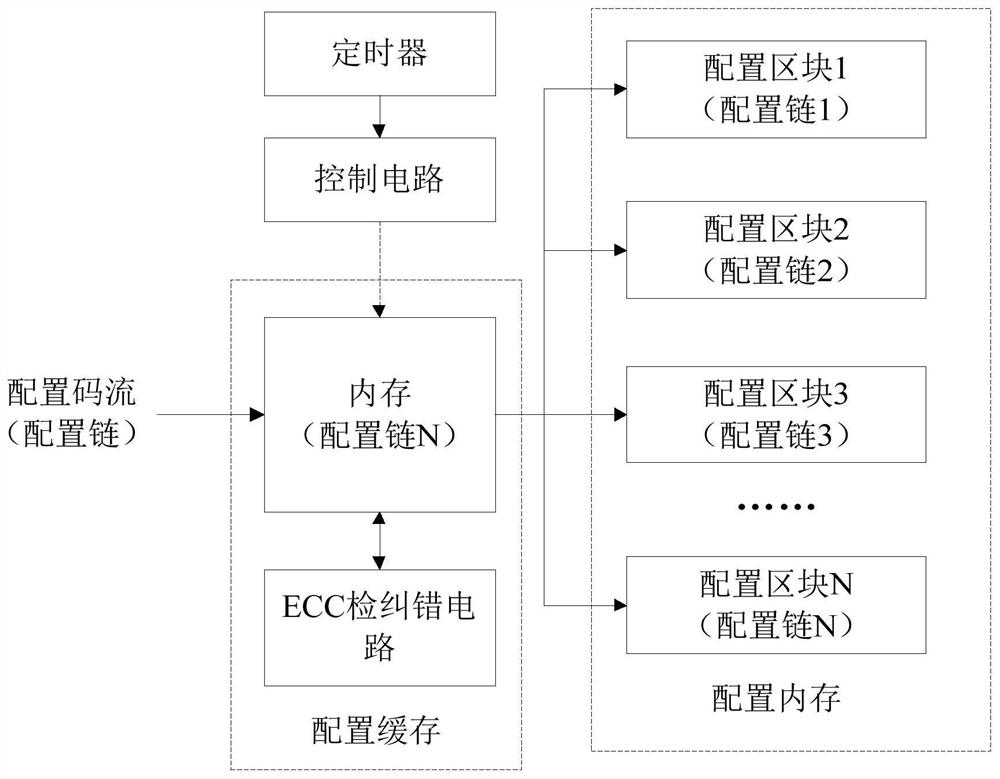

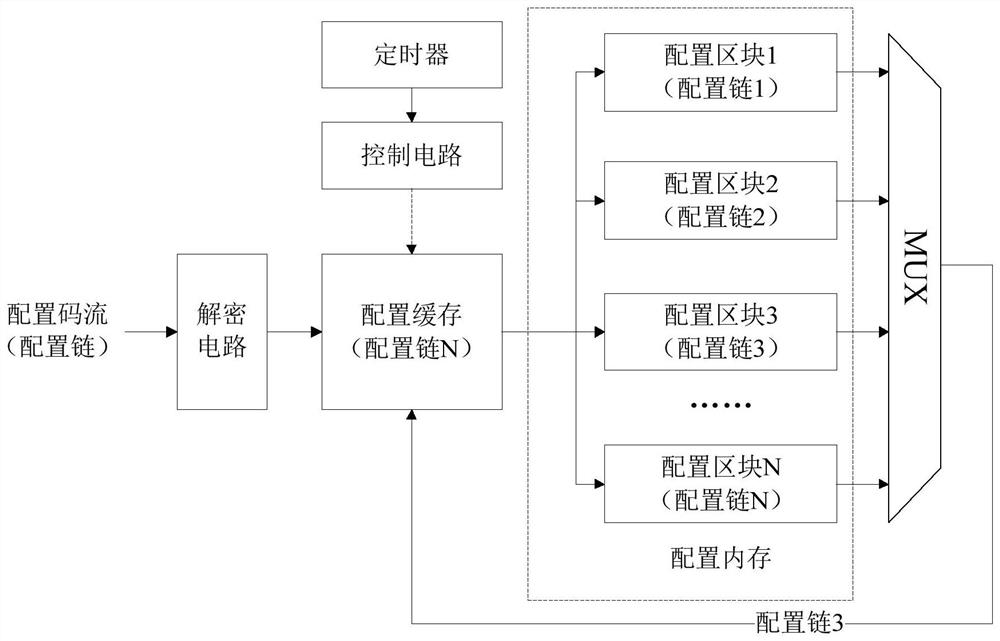

[0027] This application discloses an FPGA that improves the reliability of key configuration code streams by multiplexing buffer memory, such as figure 1 , the FPGA internally includes a configuration cache, a configuration memory and a control circuit, and the configuration memory includes N configuration blocks, such as figure 1 Taking the configuration memory including configuration blocks 1 to N as an example, the configuration cache is connected to the writing end of each configuration block.

[0028] The FPGA writes the corresponding configuration code stream designed by the user sequentially in units of configuration chains. Each configuration chain includes consecutive configuration bits with a predetermined number of bits in the configuration code stream, such as 1024 bits or 2048 bits or any custom number of bits. The number of co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com