Ultrathin coreless three-layer circuit board and preparation method thereof

A circuit board, three-layer board technology, applied in the direction of multi-layer circuit manufacturing, printed circuit manufacturing, circuit devices, etc., can solve the problems of insufficient wire processing thin plate ability, material waste, etc., to reduce production and process costs, reduce materials Waste, the effect of improving manufacturing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

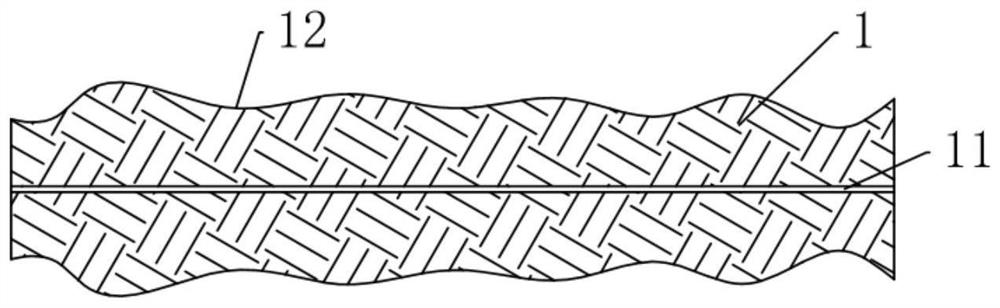

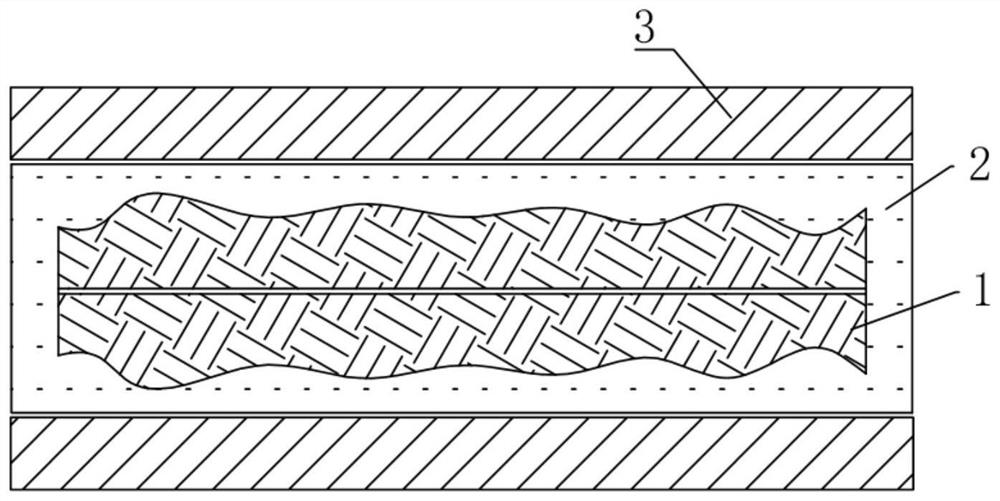

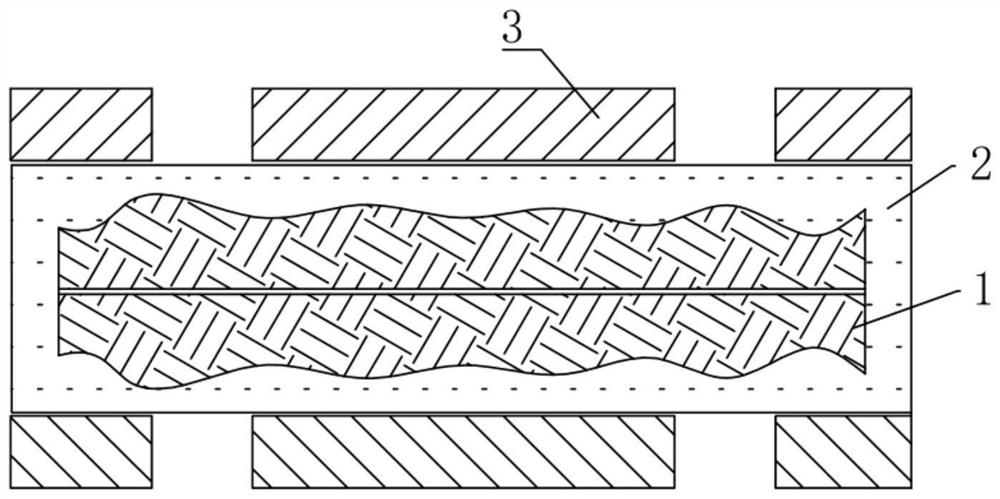

[0045] A kind of ultra-thin coreless three-layer circuit board, see Figure 1-7 , including the composite board, the composite board includes two three-layer boards, it can be understood that after the composite board is manufactured, the composite board can be disassembled into two three-layer boards, that is, two three-layer circuit boards are formed.

[0046] The composite board includes two conductor layers 1 that are attached to each other, and the first PP layer 2 is wrapped around the two conductor layers 1, that is, under the wrapping of the first PP layer 2, the two conductor layers 1 are fixed together to form a As a whole, other components can be added on the outside of the two conductor layers 1 to form a two-part symmetrical circuit board.

[0047] In practical applications, the first PP layer 2 can be a semi-cured PP layer, and the semi-cured PP layer can be placed on the outside of the two conductor layers 1 at the beginning, and then under high temperature pres...

Embodiment 2

[0065] A kind of ultra-thin coreless three-layer circuit board, differs from Embodiment 1 in that, see Figure 8 A solder resist layer 6 is provided on the outside of the second copper foil layer 5, and the solder resist layer 6 may be a solder resist ink layer.

[0066] In practical application, when printing the solder resist layer 6, it is necessary to leak out the solder pads needed by the packaging factory and the assembly factory, and a protective layer 7 is provided on the outside of the second copper foil layer 5 where the solder resist layer 6 is not provided. , the protection layer 7 can be one of nickel-gold layer, nickel-palladium-gold layer, nickel-silver-gold layer, nickel-silver layer, OSP layer or tin layer.

[0067] This embodiment also provides a preparation process for an ultra-thin coreless three-layer circuit board. The difference from Embodiment 1 is that after the two three-layer boards are obtained, it also includes:

[0068] Perforate the second coppe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com